Nächste Seite: Re: TTL-Gatter, Atmega 8, Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: 32 Bit

library ieee;

use ieee.std_logic_1164.all;

entity fulladder is

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end;

architecture behaviour of fulladder is

begin

s <= a xor b xor c;

u <= (a and b) or ((a or b) and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarryadder32 is

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of ripplecarryadder32 is

component fulladder

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end component;

signal c : std_logic_vector (31 downto 0);

signal u : std_logic_vector (31 downto 0);

begin

c(0) <= '0';

add1: fulladder PORT MAP (c=>c(0),b=>b(0),a=>a(0),s=>s(0),u=>u(0));

l1:

for i in 1 to 31 generate

sn: fulladder PORT MAP (c=>u(i-1),b=>b(i),a=>a(i),s=>s(i),u=>u(i));

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity srlatch is

port (

q: out std_logic;

r, s: in std_logic

);

end;

architecture behaviour of srlatch is

signal q1, q2: std_logic;

begin

q1 <= s when q1 = 'U' else (q2 nor s);

q2 <= not s when q2 = 'U' else (q1 nor r);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity csrlatch is

port (

q: out std_logic;

r, s, c: in std_logic

);

end;

architecture behaviour of csrlatch is

component srlatch

port (

q: out std_logic;

r, s: in std_logic

);

end component;

signal s1, r1 : std_logic;

begin

sn: srlatch PORT MAP (s=>s1, r=>r1, q=>q);

s1 <= c and s;

r1 <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

q: out std_logic;

d, c: in std_logic

);

end;

architecture behaviour of dlatch is

component csrlatch

port (

q: out std_logic;

s, r, c: in std_logic

);

end component;

signal s1, r1 : std_logic;

begin

sn: csrlatch PORT MAP (s=>s1, r=>r1, c=>c, q=>q);

s1 <= d;

r1 <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsff is

port (

q: out std_logic;

d, c: in std_logic

);

end;

architecture behaviour of dmsff is

component dlatch

port (

q: out std_logic;

d, c: in std_logic

);

end component;

signal c1, c2 : std_logic;

signal q1 : std_logic;

begin

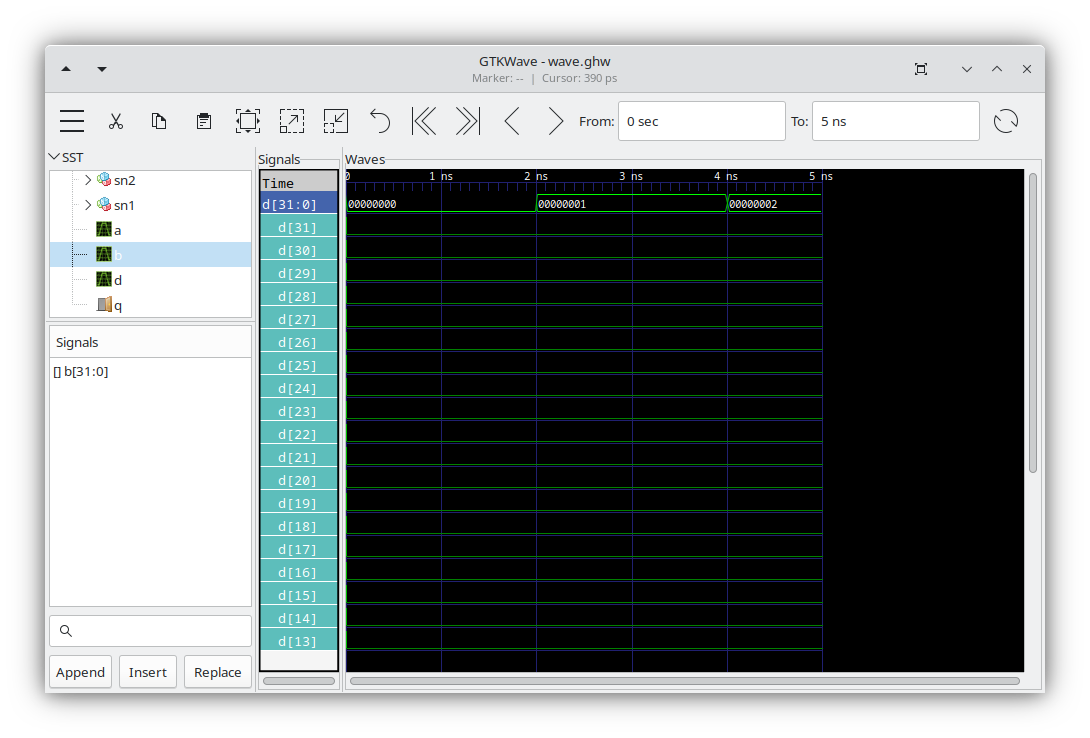

sn1: dlatch PORT MAP (d=>d, c=>c1, q=>q1);

sn2: dlatch PORT MAP (d=>q1, c=>c2, q=>q);

c1 <= c;

c2 <= not c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

c: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dmsff

port (

q: out std_logic;

d, c: in std_logic

);

end component;

begin

l1:

for i in 0 to 31 generate

sn: dmsff PORT MAP (q=>q(i), d=>d(i), c=>c);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity counter32 is

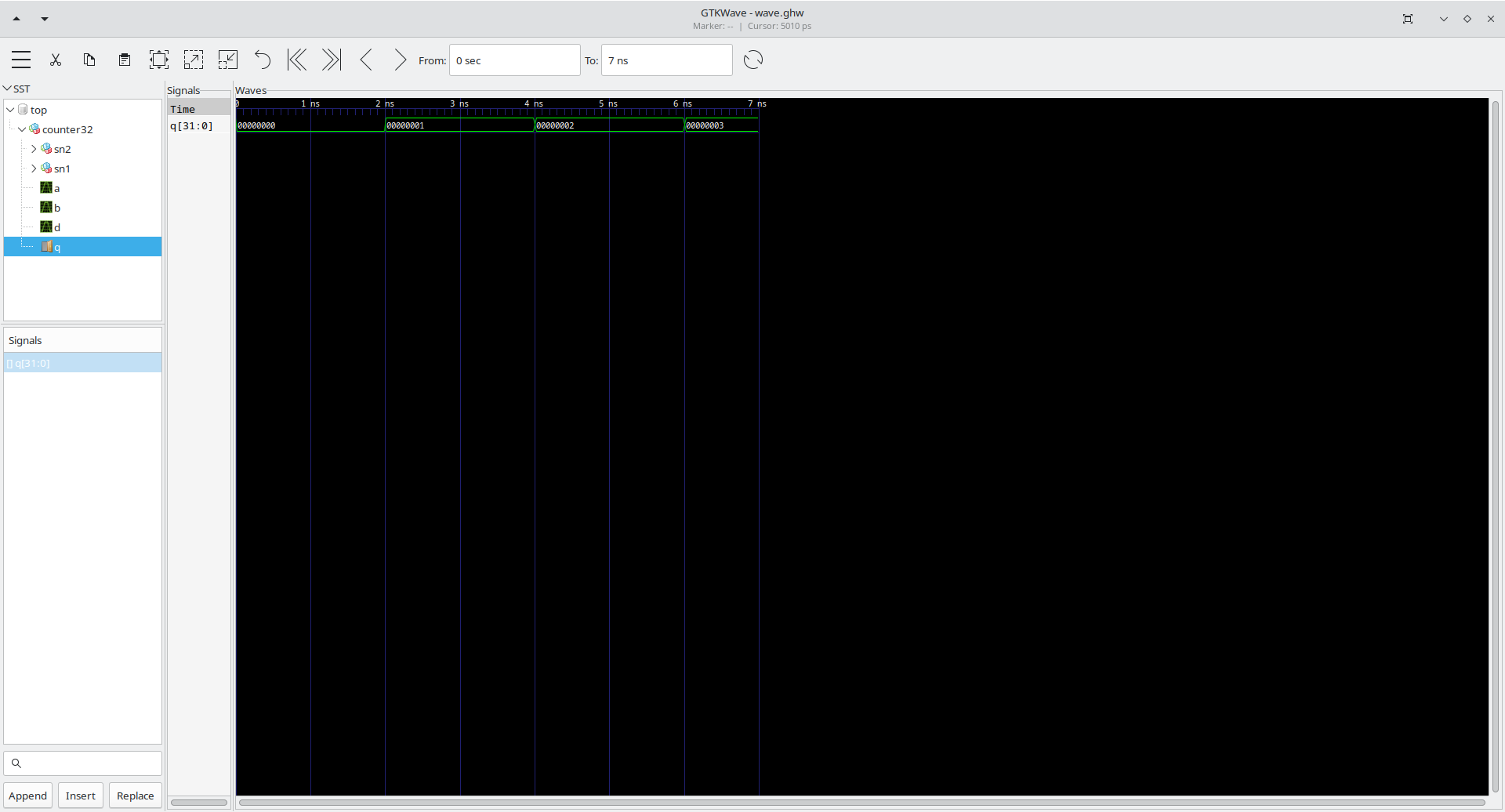

port (

q: inout std_logic_vector (31 downto 0)

);

end;

architecture behaviour of counter32 is

component reg32

port (

c: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end component;

component ripplecarryadder32

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (31 downto 0);

signal b: std_logic_vector (31 downto 0);

signal a: std_logic_vector (31 downto 0);

signal c: std_logic;

begin

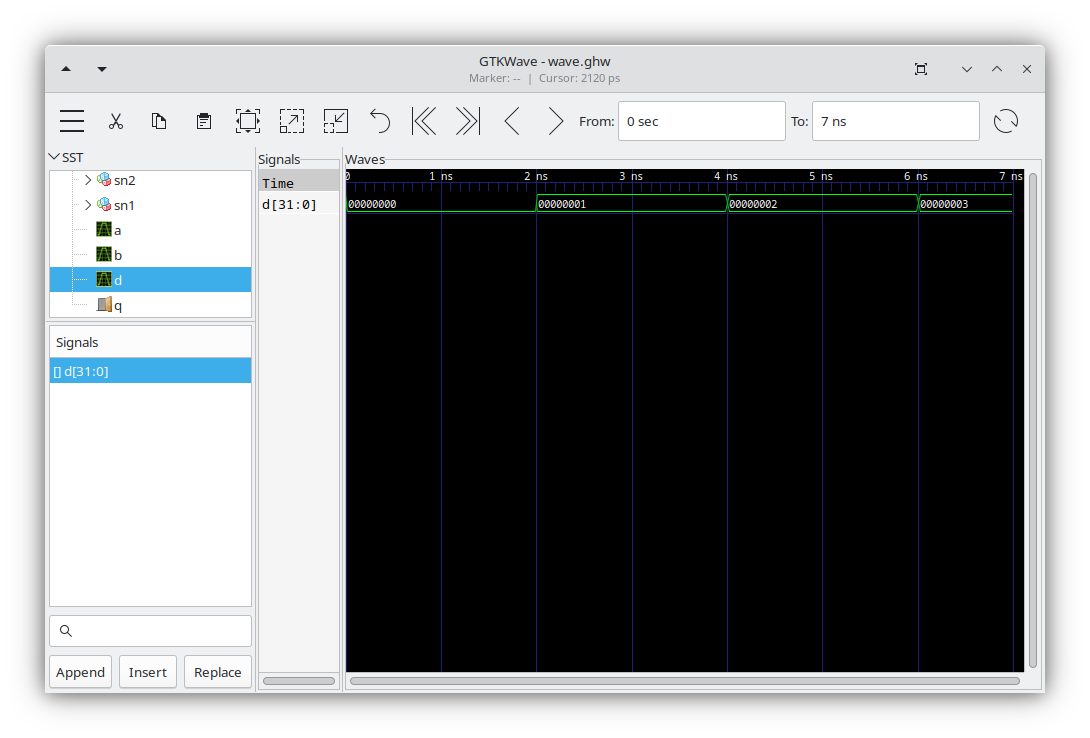

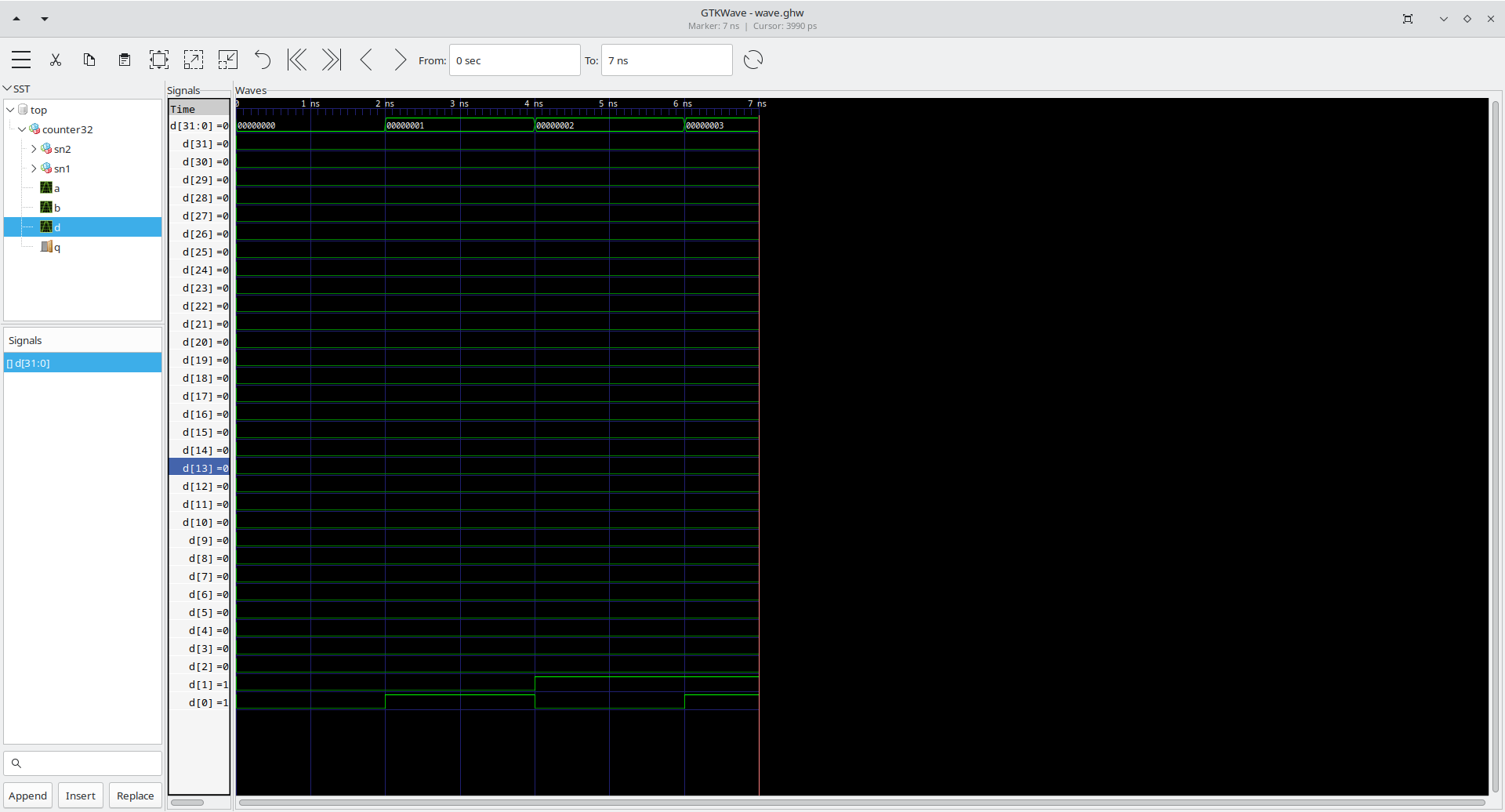

sn1: reg32 PORT MAP (q=>b, d=>d, c=>c);

sn2: ripplecarryadder32 PORT MAP (b=>b, a=>a, s=>d);

a <= ('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','1') after 0 ns;

q <= d;

--b <= ('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0') after 0 ns;

--d <= ('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0') after 0 ns;

c <= '0' after 0 ns, '1' after 1 ns, '0' after 2 ns, '1' after 3 ns, '0' after 4 ns, '1' after 5 ns, '0' after 6 ns, '1' after 7 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity fulladder is

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end;

architecture behaviour of fulladder is

begin

s <= a xor b xor c;

u <= (a and b) or ((a or b) and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarryadder32 is

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of ripplecarryadder32 is

component fulladder

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end component;

signal c : std_logic_vector (31 downto 0);

signal u : std_logic_vector (31 downto 0);

begin

c(0) <= '0';

add1: fulladder PORT MAP (c=>c(0),b=>b(0),a=>a(0),s=>s(0),u=>u(0));

l1:

for i in 1 to 31 generate

sn: fulladder PORT MAP (c=>u(i-1),b=>b(i),a=>a(i),s=>s(i),u=>u(i));

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity srlatch is

port (

q: out std_logic;

r, s: in std_logic

);

end;

architecture behaviour of srlatch is

signal q1, q2: std_logic;

begin

q1 <= s when q1 = 'U' else (q2 nor s);

q2 <= not s when q2 = 'U' else (q1 nor r);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity csrlatch is

port (

q: out std_logic;

r, s, c: in std_logic

);

end;

architecture behaviour of csrlatch is

component srlatch

port (

q: out std_logic;

r, s: in std_logic

);

end component;

signal s1, r1 : std_logic;

begin

sn: srlatch PORT MAP (s=>s1, r=>r1, q=>q);

s1 <= c and s;

r1 <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

q: out std_logic;

d, c: in std_logic

);

end;

architecture behaviour of dlatch is

component csrlatch

port (

q: out std_logic;

s, r, c: in std_logic

);

end component;

signal s1, r1 : std_logic;

begin

sn: csrlatch PORT MAP (s=>s1, r=>r1, c=>c, q=>q);

s1 <= d;

r1 <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsff is

port (

q: out std_logic;

d, c: in std_logic

);

end;

architecture behaviour of dmsff is

component dlatch

port (

q: out std_logic;

d, c: in std_logic

);

end component;

signal c1, c2 : std_logic;

signal q1 : std_logic;

begin

sn1: dlatch PORT MAP (d=>d, c=>c1, q=>q1);

sn2: dlatch PORT MAP (d=>q1, c=>c2, q=>q);

c1 <= c;

c2 <= not c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

c: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dmsff

port (

q: out std_logic;

d, c: in std_logic

);

end component;

begin

l1:

for i in 0 to 31 generate

sn: dmsff PORT MAP (q=>q(i), d=>d(i), c=>c);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity counter32 is

port (

q: inout std_logic_vector (31 downto 0)

);

end;

architecture behaviour of counter32 is

component reg32

port (

c: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end component;

component ripplecarryadder32

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (31 downto 0);

signal b: std_logic_vector (31 downto 0);

signal a: std_logic_vector (31 downto 0);

signal c: std_logic;

begin

sn1: reg32 PORT MAP (q=>b, d=>d, c=>c);

sn2: ripplecarryadder32 PORT MAP (b=>b, a=>a, s=>d);

a <= ('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','1') after 0 ns;

q <= d;

--b <= ('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0') after 0 ns;

--d <= ('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0') after 0 ns;

c <= '0' after 0 ns, '1' after 1 ns, '0' after 2 ns, '1' after 3 ns, '0' after 4 ns, '1' after 5 ns, '0' after 6 ns, '1' after 7 ns;

end;

Man muss vor allem eines machen, da kommt man nicht drum rum

Das Problem liegt im Latch selber - am Anfang ist der Zustand 'U'. Das muss man gross schreiben - also Undefined. Und da

q1 <= (q2 nor s); q2 <= (q1 nor r);

Beim RS-Latch. Jetzt wenn man das so selber lötet, würde sich das vielleicht einpendeln. Umgekehrt in VHDL gibt es die Regel. wenn ein Bit 'U' und in ein Schaltnetz geschickt wird, dann ist der Ausgang wieder 'U'. Blöd beim Schaltwerk, wo es in den Zustand wieder rein geht. Man kriegt, jetzt das 'U' nicht mehr raus. Jetzt braucht man das IF

Ich habe das so gemacht. Damit geht es

architecture behaviour of srlatch is

signal q1, q2: std_logic;

begin

q1 <= s when q1 = 'U' else (q2 nor s);

q2 <= not s when q2 = 'U' else (q1 nor r);

q <= q1;

end;

architecture behaviour of reg32 is

component dmsff

port (

q: out std_logic;

d, c: in std_logic;

we: in std_logic

);

end component;

signal c1: std_logic;

begin

c1 <= we and c;

l1:

for i in 0 to 31 generate

sn: dmsff PORT MAP (q=>q(i), d=>d(i), c=>c1);

end generate;

end;

-- gut package und type habe ich hingekriegt, f"ur den 32x32 bit registersatz - bitte nichts denken, der Code nicht vollst"andig, aber ich habe es getestet, package und type funktioniert. Das braucht man wegen dem 32x32_1 multiplexer und wegen dem 32x1_32 demultiplexer

library ieee;

use ieee.std_logic_1164.all;

entity fulladder is

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end;

architecture behaviour of fulladder is

begin

s <= a xor b xor c;

u <= (a and b) or ((a or b) and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarryadder32 is

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of ripplecarryadder32 is

component fulladder

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end component;

signal c : std_logic_vector (31 downto 0);

signal u : std_logic_vector (31 downto 0);

begin

c(0) <= '0';

add1: fulladder PORT MAP (c=>c(0),b=>b(0),a=>a(0),s=>s(0),u=>u(0));

l1:

for i in 1 to 31 generate

sn: fulladder PORT MAP (c=>u(i-1),b=>b(i),a=>a(i),s=>s(i),u=>u(i));

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity srlatch is

port (

q: out std_logic;

r, s: in std_logic

);

end;

architecture behaviour of srlatch is

signal q1, q2: std_logic;

begin

q1 <= s when q1 = 'U' else (q2 nor s);

q2 <= not s when q2 = 'U' else (q1 nor r);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity csrlatch is

port (

q: out std_logic;

r, s, c: in std_logic

);

end;

architecture behaviour of csrlatch is

component srlatch

port (

q: out std_logic;

r, s: in std_logic

);

end component;

signal s1, r1 : std_logic;

begin

sn: srlatch PORT MAP (s=>s1, r=>r1, q=>q);

s1 <= c and s;

r1 <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

q: out std_logic;

d, c: in std_logic

);

end;

architecture behaviour of dlatch is

component csrlatch

port (

q: out std_logic;

s, r, c: in std_logic

);

end component;

signal s1, r1 : std_logic;

begin

sn: csrlatch PORT MAP (s=>s1, r=>r1, c=>c, q=>q);

s1 <= d;

r1 <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsff is

port (

q: out std_logic;

d, c: in std_logic

);

end;

architecture behaviour of dmsff is

component dlatch

port (

q: out std_logic;

d, c: in std_logic

);

end component;

signal c1, c2 : std_logic;

signal q1 : std_logic;

begin

sn1: dlatch PORT MAP (d=>d, c=>c1, q=>q1);

sn2: dlatch PORT MAP (d=>q1, c=>c2, q=>q);

c1 <= c;

c2 <= not c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

c: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0);

we: in std_logic

);

end;

architecture behaviour of reg32 is

component dmsff

port (

q: out std_logic;

d, c: in std_logic

);

end component;

signal c1: std_logic;

begin

c1 <= we and c;

l1:

for i in 0 to 31 generate

sn: dmsff PORT MAP (q=>q(i), d=>d(i), c=>c1);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

library ieee;

use ieee.std_logic_1164.all;

package t_32x32 is

type t_32x32 is array (31 downto 0) of std_logic_vector (31 downto 0);

end package t_32x32;

use t32_32;

entity mux32x32_1 is

port (

data_in32: in t_32x32;

data_out32: out std_logic_vector (31 downto 0)

);

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset32x32 is

port (

we: in std_logic;

read_register_1: in std_logic_vector (4 downto 0);

read_register_2: in std_logic_vector (4 downto 0);

write_register: in std_logic_vector (4 downto 0);

read_data_1: in std_logic_vector (31 downto 0);

read_data_2: in std_logic_vector (31 downto 0);

write_data: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of registerset32x32 is

component reg32

port (

c: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end component;

component mux32x32_1

port (

);

end component;

component demux32x1_32

port (

);

end component;

begin

l1:

for i in 0 to 31 generate

sn: dmsff PORT MAP (q=>q(i), d=>d(i), c=>c1);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity counter32 is

port (

q: inout std_logic_vector (31 downto 0)

);

end;

architecture behaviour of counter32 is

component reg32

port (

c: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end component;

component ripplecarryadder32

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (31 downto 0);

signal b: std_logic_vector (31 downto 0);

signal a: std_logic_vector (31 downto 0);

signal c: std_logic;

begin

sn1: reg32 PORT MAP (q=>b, d=>d, c=>c);

sn2: ripplecarryadder32 PORT MAP (b=>b, a=>a, s=>d);

a <= ('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','1') after 0 ns;

q <= d;

--b <= ('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0') after 0 ns;

--d <= ('0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0','0') after 0 ns;

c <= '0' after 0 ns, '1' after 1 ns, '0' after 2 ns, '1' after 3 ns, '0' after 4 ns, '1' after 5 ns, '0' after 6 ns, '1' after 7 ns;

end;