Nächste Seite: Re: Aufgaben und Übungen, Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: Aufgaben und Übungen,

// Das Programm sieht jetzt wie folgt aus, das war die erste Version, die hat aber noch einen Fehler, weil - x0 und x1, Eingangsvariable, konnte mehrfach belegt werden, das l"ose ich im nachfolgenden Programm, poste ich gleich

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define N_STATES 4

int main (void) {

int x1;

int x2;

time_t t;

int i, j;

int n_next;

int state;

int state_next;

int y;

srand ((unsigned)time(\&t));

printf ("tAtBtCtDt[CODE]n", state, x1, x2, y, state_next);

for (i = 0; i < N_STATES; i++) {

state = i;

n_next = (rand () % (N_STATES-1)) + 1;

for (j = 0; j < n_next; j++) {

state_next = rand () % N_STATES;

x1 = rand () % 2;

x2 = rand () % 2;

y = rand () % 2;

printf ("t%it%i%it%it%it[CODE]n", state, x1, x2, y, state_next);

}

}

printf ("A: Aktueller Zustand\B: Eingabe, x1, x2\C: Ausgabe, y, D: Folgezustandn");

return 0;

}

# Das w"are die Ausgabe des Programms, man sieht x1 und x0 ist mehrfach belegt A B C D [CODE] 0 00 1 1 [CODE] 1 01 1 2 [CODE] 1 01 0 0 [CODE] 2 10 1 0 [CODE] 2 11 0 0 [CODE] 2 11 0 1 [CODE] 3 01 1 3 [CODE] 3 01 1 2 [CODE] 3 10 0 1 [CODE] A: Aktueller ZustandB: Eingabe, x1, x2C: Ausgabe, y, D: Folgezustand

// Jetzt die verbesserte Version

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define N_STATES 4

int main (void) {

int x1;

int x2;

time_t t;

int i, j;

int n_next;

int state;

int state_next;

int y;

srand ((unsigned)time(\&t));

printf ("tAtBtCtDt[CODE]n", state, x1, x2, y, state_next);

for (i = 0; i < N_STATES; i++) {

state = i;

n_next = (rand () % (N_STATES-1)) + 1;

for (j = 0; j < n_next; j++) {

state_next = rand () % N_STATES;

x1 = j \& 0x01;

x2 = (j \& 0x02) >> 1;

y = rand () % 2;

printf ("t%it%i%it%it%it[CODE]n", state, x2, x1, y, state_next);

}

}

printf ("A: Aktueller ZustandnB: Eingabe, x1, x2nC: Ausgabe, y, D: Folgezustandn");

return 0;

}

# Die Ausgabe unten musste ich noch korrigieren, das haeb ich gemacht. A B C D [CODE] 0 00 1 0 [CODE] 0 01 1 3 [CODE] 0 10 1 2 [CODE] 1 00 1 3 [CODE] 1 01 1 3 [CODE] 2 00 1 0 [CODE] 2 01 1 3 [CODE] 3 00 1 2 [CODE] 3 01 0 2 [CODE] A: Aktueller ZustandB: Eingabe, x1, x2C: Ausgabe, y, D: Folgezustand

# Gut, das kommt jetzt auf meine Homepage und dann fange ich mit der "Ubung gleich an A B C D [CODE] 0 00 0 0 [CODE] 0 01 0 2 [CODE] 0 10 1 3 [CODE] 1 00 0 1 [CODE] 2 00 1 2 [CODE] 2 01 0 1 [CODE] 2 10 0 2 [CODE] 3 00 0 1 [CODE] A: Aktueller Zustand B: Eingabe, x1, x2 C: Ausgabe, y, D: Folgezustand

A B C D Un"ar Kodierter Folgezustand 0 00 0 0 0001 0 01 0 2 0100 0 10 1 3 1000 1 00 0 1 0010 2 00 1 2 0100 2 01 0 1 0010 2 10 0 2 0100 3 00 0 1 0010 A: Aktueller Zustand B: Eingabe, x1, x2 C: Ausgabe, y, D: Folgezustand

A C D1 D2 D3 D4 0 0 0 2 0 1 3 1 0 1 2 1 2 2 0 1 2 3 0 1 (0,1) (0,1), (2,1) (0,2) (0,2), (2,2) (0,3) ()

A B C D Un"ar Kodierter Folgezustand 0 00 0 0 0001 0 01 0 2 0100 0 10 1 3 1000 1 00 0 1 0010 2 00 1 2 0100 2 01 0 1 0010 2 10 0 2 0100 3 00 0 1 0010 A: Aktueller Zustand B: Eingabe, x1, x2 C: Ausgabe, y, D: Folgezustand

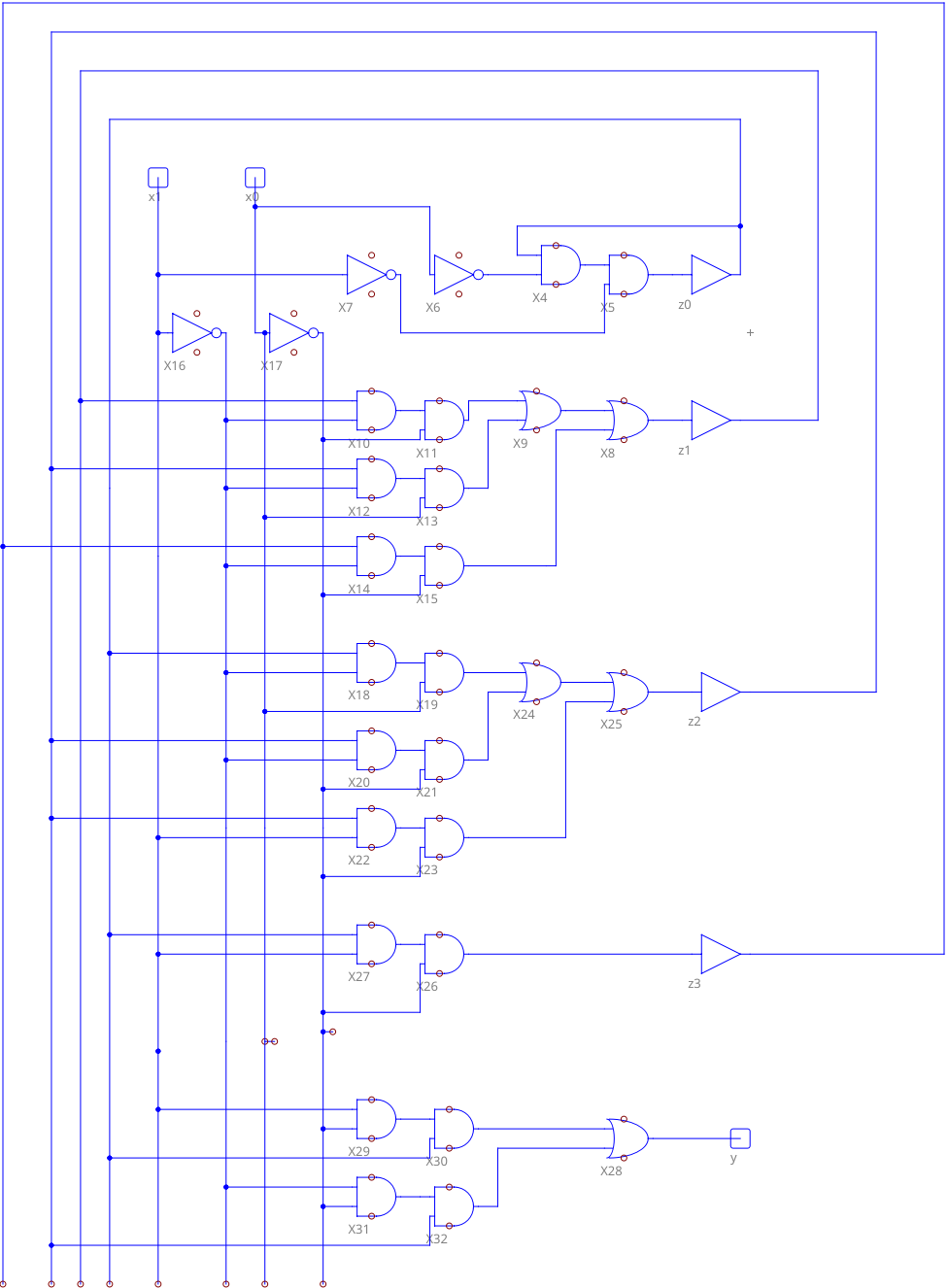

z0+ <= (z0) and not x1 and not x0 z1+ <= ((z1) and not x1 and not x0) or (z2 and (x1 and not x0)) or (z3 and not x1 and not x0) z2+ <= (z0 and not x1 and x0) or (z2 and not x1 and not x0) or (z2 and x1 and not x0) z3+ <= (z0 and x1 and not x0) y <= (z0+ and x1 and not x0) or (z2 or not x1 and not x0)

Da war ein kleiner Fehler drin

A B C D Un"ar Kodierter Folgezustand 0 00 0 0 0001 0 01 0 2 0100 0 10 1 3 1000 1 00 0 1 0010 2 00 1 2 0100 2 01 0 1 0010 2 10 0 2 0100 3 00 0 1 0010 A: Aktueller Zustand B: Eingabe, x1, x2 C: Ausgabe, y, D: Folgezustand z0+ <= (z0) and not x1 and not x0 z1+ <= ((z1) and not x1 and not x0) or (z2 and (not x1 and x0)) or (z3 and not x1 and not x0) z2+ <= (z0 and not x1 and x0) or (z2 and not x1 and not x0) or (z2 and x1 and not x0) z3+ <= (z0 and x1 and not x0) y <= (z0 and x1 and not x0) or (z2 or not x1 and not x0)

z0+ <= (z0) and not x1 and not x0 z1+ <= ((z1) and not x1 and not x0) or (z2 and (not x1 and x0)) or (z3 and not x1 and not x0) z2+ <= (z0 and not x1 and x0) or (z2 and not x1 and not x0) or (z2 and x1 and not x0) z3+ <= (z0 and x1 and not x0) y <= (z0 and x1 and not x0) or (z2 or not x1 and not x0)

library ieee;

use ieee.std_logic_1164.all;

entity meinautomat2024_01_03 is

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y: out std_logic

);

end;

architecture verhalten of meinautomat2024_01_03 is

begin

z0s <= (z0) and not x1 and not x0;

z1s <= ((z1) and not x1 and not x0) or (z2 and (not x1 and x0)) or (z3 and not x1 and not x0);

z2s <= (z0 and not x1 and x0) or (z2 and not x1 and not x0) or (z2 and x1 and not x0);

z3s <= (z0 and x1 and not x0);

y <= (z0 and x1 and not x0) or (z2 and not x1 and not x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity meinautomat2024_01_03_testbench is

port (

z3s, z2s, z1s, z0s: out std_logic;

y: out std_logic

);

end;

architecture verhalten of meinautomat2024_01_03_testbench is

component meinautomat2024_01_03

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y: out std_logic

);

end component;

signal z3, z2, z1, z0: std_logic;

signal x1, x0: std_logic;

begin

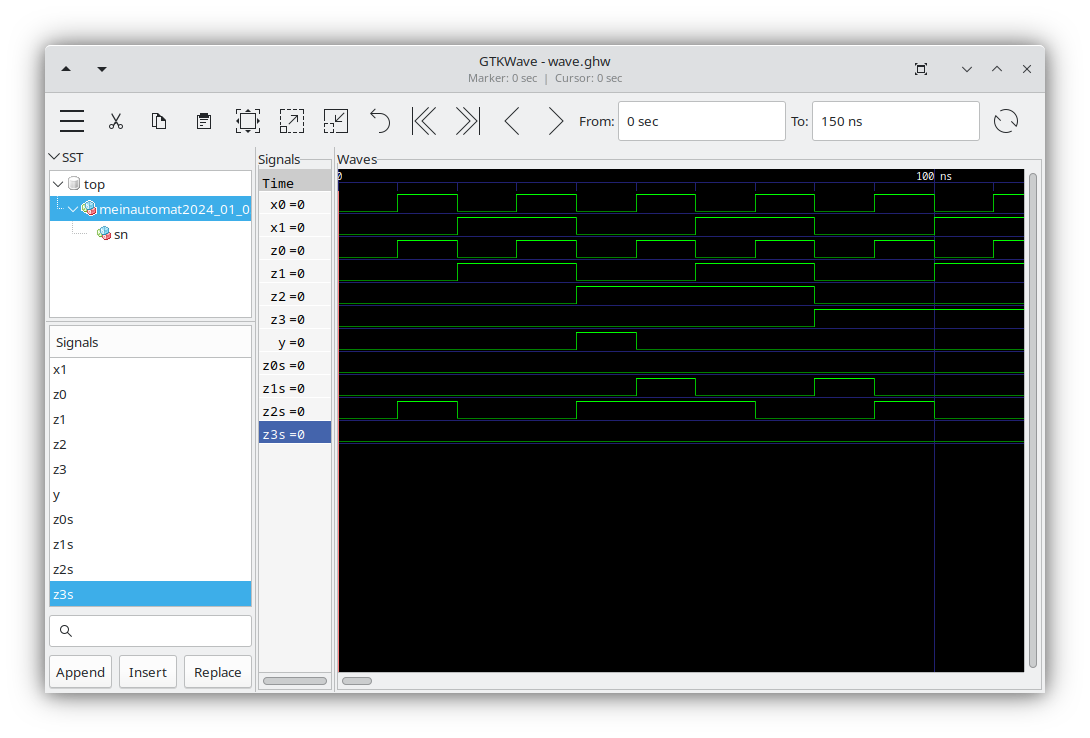

sn: meinautomat2024_01_03 PORT MAP (z3=>z3, z2=>z2, z1=>z1, z0=>z0, x1=>x1, x0=>x0, y=>y, z3s=>z3s, z2s=>z2s, z1s=>z1s, z0s=>z0s );

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

z0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

z1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

z2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

z3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;