Nächste Seite: quine20250404.vhdl Aufwärts: led schaltungen - ttl Vorherige Seite: quine20250304.vhdl

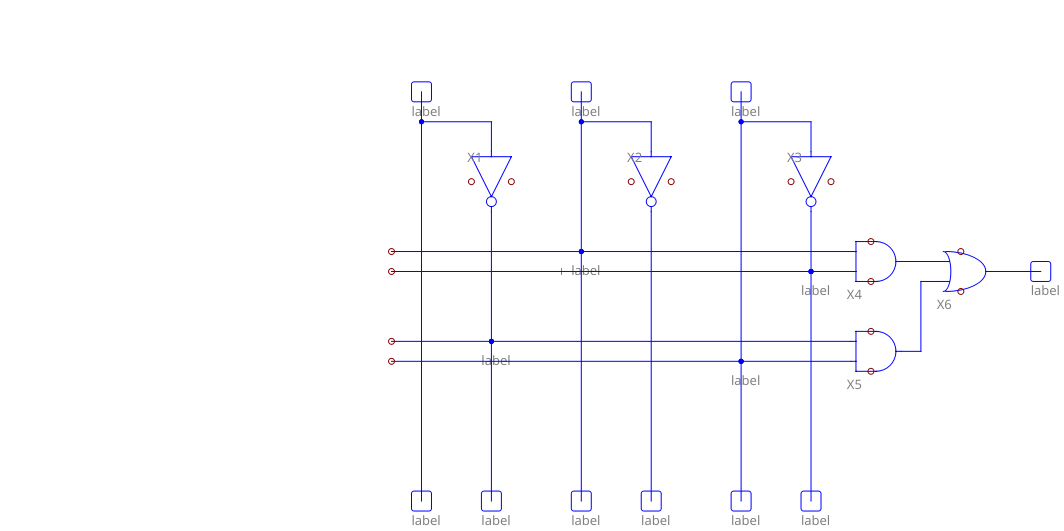

(C) David Vajda Fri Apr 4 14:31:14 2025 3 Network - TTL - Disjunktive Normalform x2 x1 x0 y 0 0 0 0 0 1 0 0 1 1 2 0 1 0 1 3 0 1 1 1 4 1 0 0 0 5 1 0 1 0 6 1 1 0 1 7 1 1 1 0 x2 x1 x0 y 1 0 0 1 1 2 0 1 0 1 3 0 1 1 1 6 1 1 0 1 x2 x1 x0 y Gruppe 1: 1 0 0 1 1 2 0 1 0 1 Gruppe 2: 3 0 1 1 1 6 1 1 0 1 1:3 0 - 1 2:3 0 1 - 2:6 - 1 0 2:6 - 1 0 1:3 0 - 1 2:3 0 1 - 1 2 3 6 2:6 + + 1:3 + + 2:3 + + 1 2 3 6 2:6 + + 1:3 + + 2:6 - 1 0 1:3 0 - 1 y <= (x1 and not x0) or (not x2 and x0); library ieee; use ieee.std_logic_1164.all; entity quine20250404 is port ( x2, x1, x0: in std_logic; y: out std_logic ); end; architecture behaviour of quine20250404 is begin y <= (x1 and not x0) or (not x2 and x0); end; library ieee; use ieee.std_logic_1164.all; entity quine20250404testbench is port ( y: out std_logic ); end; architecture behaviour of quine20250404testbench is component quine20250404 port ( x2, x1, x0: in std_logic; y: out std_logic ); end component; signal x2, x1, x0: std_logic; begin q: quine20250404 PORT MAP (x2=>x2, x1=>x1, x0=>x0, y=>y); |