Nächste Seite: 2024-09-24 Aufwärts: 2024-09-21, heute und gestern Vorherige Seite: smartcard und avr

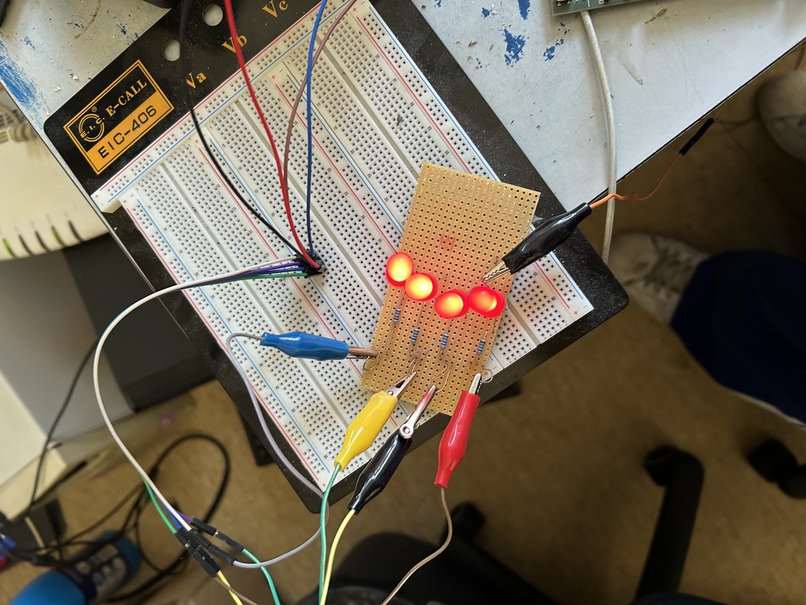

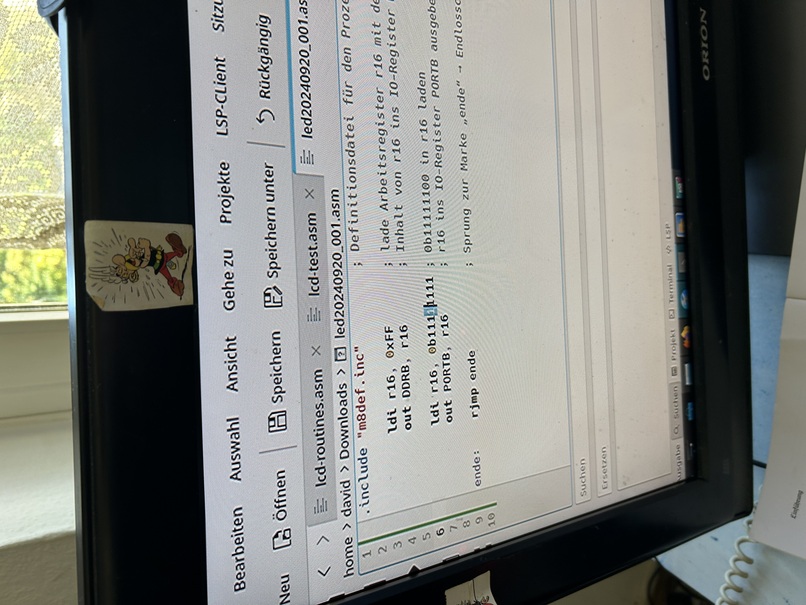

.include "m8def.inc"

ldi r16, 0xFF

out DDRB, r16

ldi r16, 0b11111111

out PORTB, r16

end: rjmp end

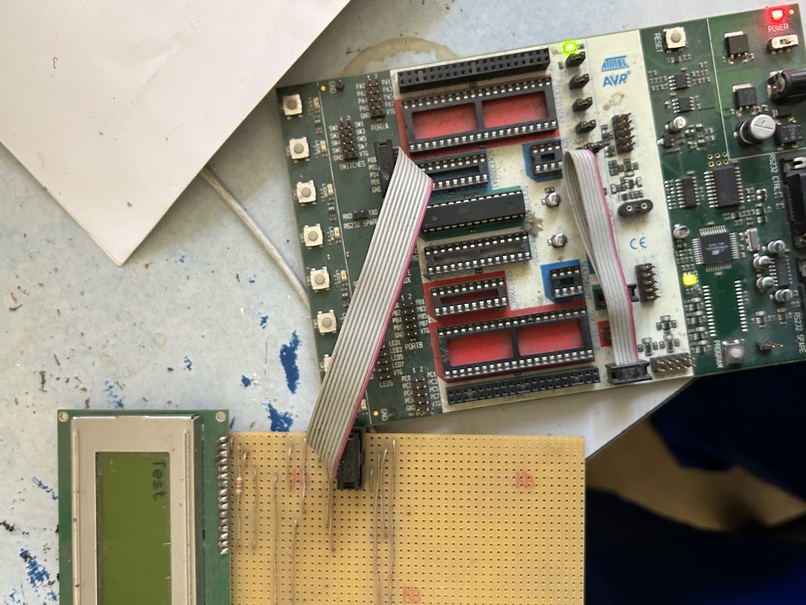

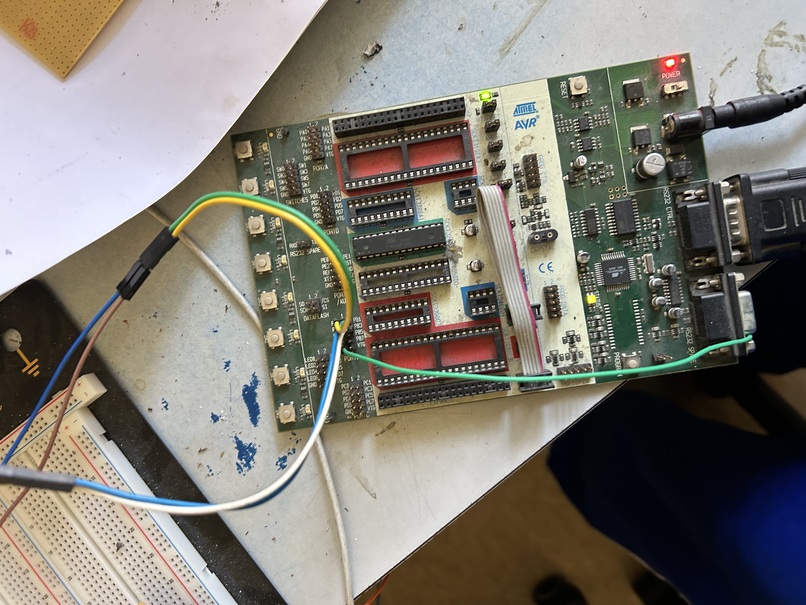

typische cpus der smartcard sind z.B. der Atmel AT90SC3232C AVR

.include "m8def.inc"

ldi r16, 0xFF

out DDRB, r16

sldi r16, 0b00000000

loop5:

com r16

out PORTB, r16

com r16

ldi r20, 0xfe

loop1: dec r20

ldi r21, 0xfe

loop2: dec r21

ldi r22, 0xfe

loop3: dec r22

ldi r23, 0xfe

loop4: dec r23

cpi r23, 0x01

brge loop4

cpi r22, 0x01

brge loop3

cpi r21, 0x01

brne loop2

cpi r20, 0x01

brne loop1

inc r16

rjmp loop5

genuegt nicht, wird mehr, aber einführend

MIPS-Architektur

lb, lbu Laden eines Bytes

sb Speichern eines Bytes

lh, lhu Laden eine Halbwortes

sh Speichern eines Halbwortes

lw Laden eines Wortes

sw Speicher eines Wortes

ld* Laden eines Doppelwortes

sd* Speichern eines Doppelwortes

la* Laden einer Addresse

li* Laden eines immidiate Wertes

l.s*, l.d* Laden eines Gleitkommaregisters

s.s*, s.d* Speichern eines Gleitkommaregisters

move* Transfer zwischen Universalregistern

mov.s* Transfer zwischen Gleitkommaregistern

mov.d*

mfhi Transfer zwischen Universalregister und den Regiestern Hi und Lo

mflo

mthi

mtlo

mfc1 Transfer zwischen Universalregistern und Gleitkommaregistern

mtc1

addi Addition

addi

addu

addiu

sub Subtration

sub

mult Multiplikation

multu

div Division

divu

abs* Absoluter Wert

neg* Negation

rem* Modulo

not* Logisches NOT

and Logisches UND

andi

or Logisches OR

ori

xor Logisches XOR

xori

nor Logisches NOR

sll Logisches Linksschieben

sllv

srl Logischse Rechtsschieben

srlv

sra Arithmetische Rechtsverschiebung

srav

rol* Rotation links

ror* Rotation rechts

slt Vergleich kleiner

slti

sltu

stliu

seq* Vergleich gleich

sne* Vergleich ungleich

sgt* Vergleich groesser

sgtu*

sge* Vergleich groeser gleich

sgeu*

sle* Vergleich kleiner gleich

sleu*

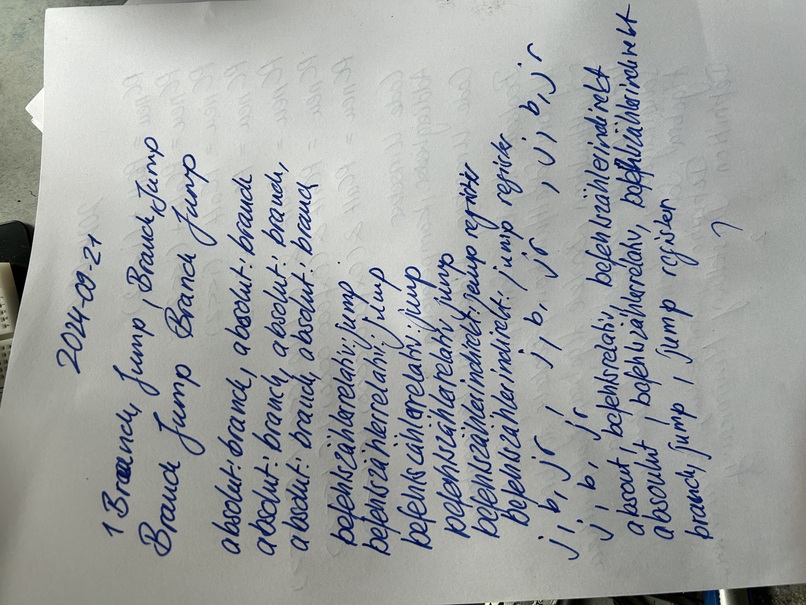

j, unbedingter Sprung

b*

jr

jal* Jump mit Speicherung PC+4

jalr Jump Regeister

beq Verzweigung falls gleich

bne Verzweigung falls ungleich

beqz* Verzweigung falls gleich

bnez* Verzweigung falls gleich

bgt* Verzweigung falls groesser

bge* Verzweigung falls groesser gleich

bgtz Verzweigung fals groesser

bgez Verzweigung falls groesser gleich

blt* Verzweigung falls kleiner

ble* Verzweigung falls kleiner gleich

bltz Verzweigung falls kleiner

blez Verzweigung falls kleiner gleich

nop Nulloperation, leere Anweisung

bge*

Befehlssatz = Instruction Set

Befehlsarten:

1. Datenbewegungsbefehle (Data Movement)

2. Arithmetisch-Logische Befehle (Integer Arithmeic and Logical)

3. Schiebe- und Rotationsbefehle (Shift, Rotate)

4. Multimediabefehle

5. Gleitkommabefehle (Floating-Point Instructions)

6. Programmsteuerbefehle (Control Transfer Instructions)

7. Systemsteuerbefehle (System Control Instructions)

8. Synchronisationsbefehle

Gleitkommabefehle (Floating-Point Instructions)

1. Bitfeldorientierte Multimediabefehle

2. Graphikorientierte Multimediabefehle

Datenbewegungsbefehle, auch: push, pop

Saturationsarithmetik: Zahlen"uberschreitungen werden auf die h"ochstwertigste bzw. niederwertigste Zahl abgebildet

Befehlsformate:

Opcode

Dreiaddressformat

Zweiaddressformat

Einaddressformat

Nulladdressformat

Lade/- und Speicherarchitektur (Load/Store Architecture)

Register-Speicher-Architektur

Speicher-Speicher-Architektur

Akkumalatoren-Architekturen

Stack- und Kellerarchitektur

Stackarchiktur: 8087, Intel

ATAM862 Atmel

Addressierungsarten:

Register und Unmittelbare Addressierungsarten

Klasse des Einstufigen Addressierung

Klasse der zweistufigen Addressierung

Datenaddressierung

Registeraddressierung

Unmittelbare Addressierung

Direkte oder absolute Addressierung

Registerindirekte ADdressierung

Registeraddressiernug mit Autoinkrement/Dekrement

Pr"ainkrement, Postinkrement

Pr"adekrement, Postdekrement

Registerindirekte Addressierung mit Verschiebung (Displacement)

Indizierte Addressierung

Indizierte Addressierung mit Verschiebung

Befehlsaddressierung

Befehlsrelativer Modus

Befehlsz"ahlerindirekt

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

- Big-Endian-Format

- Little-Endian-Format

- Datenformate

1. Einzelbit

2. Ganzzahl (Integer)

3. Gleitkomma

4. Multimedia

Ganzzahldatenformate:

- signed

- unsigned

- packed

- unpacked

- BCD-Zahlen (Binary Coded Decimals)

- ASCII

Bate

Halbwort

Wort

Doppelwort

Gleitkommadatenformate (IEEE-754-Standard)

Einfache Genauigkeit: 32 Bit

Doppelte Genauigkeit: 64 Bit

Erweiterte Genauigkeit: 80 Bit

f = (-1)^s * 1.m*2^(e-b)

biased - verschoben

b bias

m Mantissenanteil

b = 2^{ne-1}-1

p = 23, einfache

p = 52, doppelte

p = 63, erweiterte

Multimediaformate: 64 Bit breite W"orter

Bitfeldorientierte

Graphikorientierte

Befehlssatz

Datenbwegungsbefehle (Data Movement)

Arithmetisch-Logische-Befehle

Schiebe- und Rotationsbefehle

Multmediabefehle

Gleitkommabefehle

Programmsteuerbefehle

Systemsteuerbefehle

Synchronisationsbefehle

SWAP, TAS

Befehlsformate (instruction format)

Dreiaddressformat (3-Address Instruction Format), zwei Quelloperanden, ein Zieloperand

Zweiaddressformat

Einaddressformat

Nulladdressformat

Lade-/Speicherarchitektur (Load/Store Architecture)

Register-Register-Architektur

Register-Speicher-Architektur

Speicher-Speicher-Architektur

Akkumalatorarchitektur

Stack- oder Kellerarchitektur

Addressierungsart

Effektive Addresse

Effektive Addresse

Virtuelle Addresse

Physikalische Addresse

Datenaddressierungsarten

Registeraddressierung

Unmittelbare Addressierung

Direkte oder absolute Addressierung

Registerindirekte Addressierung

Registerindirekte Addressierung mit Autoinkrement/Autodekrement

Pr"ainkrement, Postinkrement, Pr"adekrement, Postdekrement

Registerindirekte Addressierung mit Verschiebung (Displacement)

Indizierte Addressierung

Indizierte Addressierung mit Verschiebung

Befehlsaddressierungsarten

Befehlsrelativer Modus

Befehlsindirekter Modus

MIS Register

$0 bis $31

$0 $zero 0 (read-only)

$1 $at reserviert f"ur den Assembler

$2 - $3 $v0 - $v1 R"uckgabewert von Funktionsaufrufen

$4 - $7 $a0 - $a3 Argumente f"ur den Funktionsauf

$8 - $15 $t0 - $t7 Tempor"are Variablen

$16 - $23 $s0 - $s7 Gesicherte Variablen

$24 - $25 $t8 - $t9 Tempor"are Variablen

$26 - $27 $k0 - $k1 Reserviert f"ur das Betriebssystem

$28 $gp Data Segment Pointer

$29 $sp Stack Pointer

$30 $fp Frame Pointer

$31 $ra Return Address

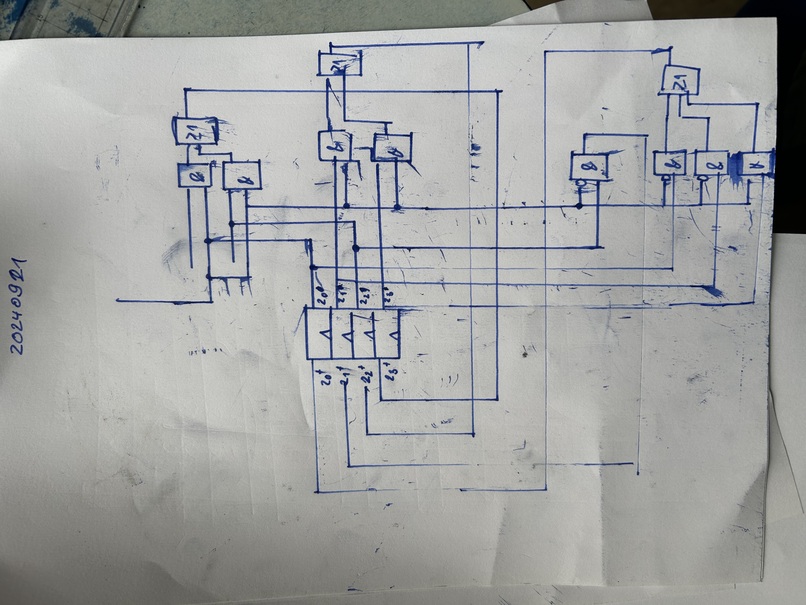

Einzyklus-Mikroarchitekur

Zustandselemente

Zustandselemente:

- PC

- Befehlsspeicher

- Registersatz

- Datenspeicher

Befehlsz"ahlerregister

Befehlsspeicher

Datenpfad

Befehlsholephase (Instruction Fetch - IF)

Zustandselmente

1. Befehlsz"ahler

2. Befehlsspeicher

3. Registersatz

4. Datenspeicher

Datenpfade f"ur die Daten (Nicht Befehle):

Also:

- Lesedaten brauchen keinen Eingabeport - warum auch? Aus ihnen wird gelesen

Stattdessen 5-Bit-Addresse (32-Bit-Register)

- Dann haben wir 3-Address-Befehle - also 2 Lesedaten

- Eine Schreibedaten: 32 Bit

- Ein Schreiberegister (Welches - 5 Bit)

- Einen CLK

- Ein WE (Write Enable)

Das ist oder war schon der Registersatz

Danach kommt die ALU und jetzt nicht direkt verbunden mit Registersatz, sondern mit Datenspeicher

Der Befehlsdekodierer bzw. die Steuereinheit hat Steuerleitung zu

- RegWrite - Registersatz - WE

- MemWrite f"ur Datenspeicher

- Keine Daten zu Lese-Daten und Lese-Register, diese sind immer frei

=> Das m"ussen wir uns so vorstellen, wie mit unseren Multiplexern im Operationswerk

Zun"achst mal das Wichtigste:

- Registersatz

- Datenspeicher

- ALU

- Steuereinheit

Der Datenspeicher ist wiederum mit dem Registersatz verbunden

Registersatz -> (Lese-Daten 1, Lese-Daten 2) -> ALU -> Datenspeicher

Multiplexer sind:

1. Vor ALU (Lese Daten 2)/F"ur Befehle, zum Berechnen der Adresse

2. Nach Datenspeicher: Entweder Datenspeicher oder ALU

Weil: Registersatz -> Datespeicher

Von Datenspeicher oder ALU kann das Ergebnis nach Regsistersatz

Registersatz -> (Lese-Daten 1, Lese-Daten 2) -> ALU/Datenspeicher -> Registersatz

Alles, was mit Befehlen im Operationswerk zu tun hat

1. Befehlsz"ahler

2. Befehlsspeicher

3. Vorzeichenerweiterung

4. 2x Addierer

Register-Satz - Lese-Daten 1 -> ALU -> Datenspeicher -> MUX

Register-Satz - Lese-Daten 1 -> ALU -> MUX

Register-Satz - Lese-Daten 1 -> ALU -> Datenspeicher -> MUX -> Registersatz - Schreibedaten

Register-Satz - Lese-Daten 1 -> ALU -> MUX -> Registersatz - Schreibedaten

Register-Satz - Lese-Daten 2 -> MUX -> ALU -> MUX

Register-Satz - Lese-Daten 2 -> MUX -> ALU -> Datenspeicher -> MUX

Normaler Befehlspfad ohne Verzweifung

Befehlsz"ahler -> Befehlsspeicher

Befehlsz"ahler -> Addierer +4 MUX -> Befehlsz"ahler.

Steuereinheit:

1. Befehlsdekodierer

2. Funktionsdekodierer

Befehlsdekodierer:

1. MemtoReg

2. MemWrite

3. Branch

4. ALUSrc

5. RegDst

6. RegWrite

7. ALUOp

Funktionsdekodierer: ALU Operation: 3 Bit

Funktionsdekodierer:

1. Ausgang: ALU Operation: 3 Bit

2. Eingang: Func - vom Befehl - 6 Bit

3. Eingang: ALUOp, 2 Bit vom Befehlsdekodierer

Befehlsdekodierer

Funktionsdekodierer

Registersatz

ALU

Datenspeicher

Befehlsspeicher

Befehlsz"ahler

Vorzeichenerweiterungseinheit

4 x MUX

1 x AND

2 x Addierer

1 x Bit Shifter

Befehlsdekodierer:

1. MemtoReg

2. MemWrite

3. Branch

4. ALUSrc

5. RegDst

6. RegWrite

7. ALUOp

Funktionsdekodierer:

1. Func

2. ALUOp

3. ALU Operation

Registersatz:

- Lese-Register 1

- Lese-Register 2

- Schreiberegister

- Schreibedaten

- WE

- Lese-Daten 1

- Lese-Daten 2

ALU:

- ALU-Ergebnis

- Null

AND:

- PCSrc

Datenspeicher:

- Addresse

- Schreibedaten

- WE

- Lesedaten

Befehlsspeicher:

- Leseaddresse

- Lesedaten

Befehlsz"ahler:

- PC (t+1)

- PC (t)

Alle Datenwege:

1. MemtoReg (Befehlsdekodierer)

2. MemWrite (Befehlsdekodierer)

3. Branch (Befehlsdekodierer)

4. ALUSrc (Befehlsdekodierer)

5. RegDst (Befehlsdekodierer)

6. RegWrite (Befehlsdekodierer)

7. ALUOp (Befehlsdekodierer)

8. Func (Funktionsdekodierer)

9. ALUOp (Funktionsdekodierer)

10. ALU Operation (Funktionsdekodierer)

11. Lese-Register 1 (Registersatz)

12. Lese-Register 2 (Registersatz)

13. Schreiberegister (Registersatz)

14. Schreibedaten (Registersatz)

15. WE (Registersatz)

16. Lese-Daten 1 (Registersatz)

17. Lese-Daten 2 (Registersatz)

18. ALU-Ergebnis (ALU)

19. Null (ALU)

20. PCSrc (AND)

21. Addresse (Datenspeicher)

22. Schreibedaten (Datenspeicher)

23. WE (Datenspeicher)

24. Lesedaten (Datenspeicher)

25. Leseaddresse (Befehlsspeicher)

26. Lesedaten (Befehlsspeicher)

27. PC (t+1) (Befehlsz"ahler)

28. PC (t) (Befehlsz"ahler)

Abgeschrieben, das war aus dem Blockschaltbild - aber allgemeiner Prozessor (OpenSource - und kann jeder verwenden):

ALUOp Func ALU Operanden

00 X 010 - add

X1 X 110 - sub

1X 100000 - add 010 - add

1X 100010 - sub 110 - sub

1X 100100 - and 000 - and

1X 100101 - or 001 - or

1X 101010 - slt 111 - set les than

Op-Code Reg-Write Reg-Dst ALU-Src Branch Mem-Write Mem-toReg ALU-Op

R-Typ 000000 1 1 0 0 0 0 10

lw 100011 1 0 1 0 0 1 00

sw 101011 0 X 1 0 1 X 00

beq 000100 0 X 0 1 0 X 01

Geographisch, von S"uden nach Norden und Westen nach Osten

Addierer, Befehlsz"ahler, Befehlsspeicher

MUX, Registersatz, Funktionsdekodierer, Befehlsdekodierer

Vorzeichenweiterung, Registersatz, Funktionsdekodierer, Befehlsdekodierer

2-Bit-Shifter, MUX, ALU

Addierer, Datenspeicher, AND

Oder als ganze Bl"ocke, von Westen nach Osten, S"uden nach Norden

Block 1:

Addierer, Befehlsz"ahler, Befehlsspeicher

Block 2:

MUX, Vorzeichenerweiterung

Regisersatz

Funktionsdekodierer, Befehlsdekodierer

Block 3

2-Bit-Shifter, Addierer, ALU

MUX, ALU, Datenspeiecher, MUX

AND

Verzweigungsbefehle:

1. Bedingt

2. Unbedingt

Zwei Quellregister werden verglichen

eq - equal

ne - not equl

gt - greater than

ge - greater than equal

lt - less than

le - less than equal

Zieladdresse:

- Angegeben durch 16-Bit-Verschiebewert

- der zum inkrementierten Befehlsz"ahler (PC+4) addiert wird

Unbedingte Spr"unge:

- absolut: branch

- befehlsz"ahlerrelativ: jump

- befehlsz"ahlerindirekt: jump register

Jump-And-Link: JAL - speichern zus"atzlich die Adresse es Befehls, der dem Sprungbefehl folgt

J (Jump)

JAL (Jump and Link)

Fall 1:

- Der im Befehlswort codierte unmittelbare Operand wird als Zahl im Zweierkomplement zum Befehlsz"ahler addiert

Fall 2:

- Der Operand ersetzt einen Teil, (Bits 0 bis 27) des aktuellen Befehlsz"ahlers

Opcode, unmittelbarer Operand (immidiate) I

Unmittelbarer Operand I

Der Operand I wird aus den 26 unteren Bits gewonnen und im Zweierkomplement interpretiert

Programmsegment: Wortgrenzen! => Zwei Stellen nach links verschieben

und anschlie"send addieren

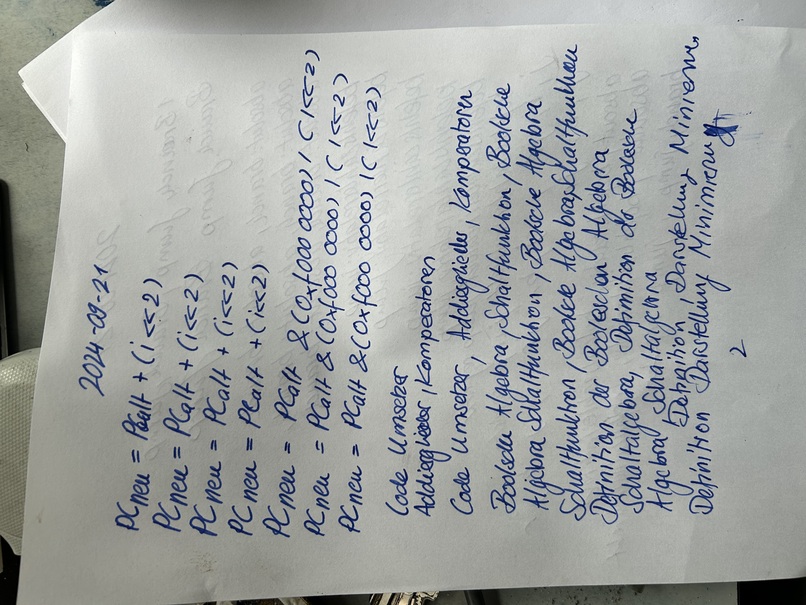

PC_neu = PC_alt + (I << I)

Im Fall 2: Ersetzen

PC_neu = PC_alt & 0xf0000000 | (I << 2)

Verzweigungsbefehle:

j, b*, jr unbedingter Sprung, befehlsz"ahlerrelativ, absoluter und befehlsz"ahlerindirekte Addressierung

jal* Jump mit Speicher von PC+4 im Register $ra

jalr Jump Register mit Speicherung von PC+4 im Register $ra

beq, bne Verzweigung fals REgister- oder Register-Operand gleich, oder ungleich

beqz*, bnez* Verzweigung falls Register oder oder ungleich 0

bgt*, bge* Gr"o"ser, Gleich

bgtz, bgez Gr"o"ser, gr"o"ser gleich Null

blt*, ble* Register-Register, Register-Operand kleiner oder kleiner gleich

bltz, blez Register kleiner oder kleiner gleich 0

nop Nulloperation

Mehrzuyklus - Zustandselemente:

- Befehlsz"ahler

- Befehlsspeicher

- Registersatz

- Datenspeicher

Datenpfad

Pipeline-Prinzip

Pipeline-Phase

Pipeline-Stufe

Pipeline-Register

Stufen:

1. Befehl holen

2. Befehl dekodieren

3. Operanden der ALU bereit stellen

4. Operation in der ALU ausf"uhren bzw. Speicherzugriff

5. Resultat in Architekturregister zur"uckschreiben

MIPS-Pipeline

1. Befehlsbereitsstellungsphase - IF-Phase - Instruction Fetch

2. Dekodier und Operandenbereitsstellungsphase (ID-Phase - Instruction Decode/Register Fetch)

3. Ausf"uhrungs oder EX-Phase (Execute/Address Calculation)

4. Speicherzugriffsphase - oder MEM-Phase (Memory Access)

5. Resultatspeicher oder WB-Phase (Write Back)

WB

MEM

EX

ID

IF

WB, MEM, EX, ID, IF

Ir, PC+4

Ai1, Ai2, Rt, Im, PC+4

Ao, Sv, Rt, Jta

Ar, Lv, Rt

Pipeline-Konflikte

- Datenkonflikte

- Steuerflusskonflikte

- Struktur und Ressourenkonflikte

Superpipelining

Parallelverarbeitung

Superpipelining: Um Frequenz zu Erh"ohen, noch mehr Stufen

UltraSPARC T1 - Superpipelining

Parallalverarbeitung:

Very Long Instruction Word - VLIW

Parallele - Befehlsausf"uhrung

1. Statisches Scheduling

1.1. In-order issue in-order completion

1.2. Very Long Instructon Word - VLIW-Prozessor

2. Dynamisches:

2.1. Out-of-order issue Out of-order completion

2.2. Out-of-order Execution OOE-Prozessor

In-Order-Execution-Pipeline: IOE-Prozessor

Out-Of-Order-Execution-Pipeline:

Sprungvorhersage: Dynamisch, statisch

Sprungziel-Cache (Branch Target Cache - BTC)

Statische Sprungvorhersagen, durch die Hardware:

- Predict always not taken

- Predict always taken

- Predict backward taken, forward not taken

Dynamische Sprungvorhersagen:

Ein- und zwei-Bit-Pr"adiktor (Seite 172 - immer abmalen)

Predikt Taken -> Predict Taken

Predict taken -> predict not taken

NT und T

predict strongly aken, predict weakle taken, p. weakly not taken ...

Immer abmahlen Seite 172/173

Korrelations-Pr"adiktor Seite 173

Auswendig:

Auswendig:

lb, lbu: laden eines Bytes

lh, lhu: Laden eines halbwortes

lw: Laden eines Wortes

ld*

la*

li*

sb

sh

sw

sd*

addi, addu, addiu

sub

mult, multu

div, divu

and, andi

or, ori

xor, xor

rem*

abs*

neg*

Lade und Speicherarchitektur

Speicher-speicherarchitektur

stack und Kellerarchitektur

Akkumulatorarchitektur

... FEHLT eines (Register Speicherarchitektur?)

Datenbewegungsbefehle

arithmetisch logische Befehl

Schiebe und Rotationsbefehle

Multimediabefehle

Gleitkommabefehle

systemsteuerbefehle

Programmsteuerbefehle

Byte

Halbwort

Wort

Doppelwort

Einzelbit

Ganzzahl

Gleitkomma

Multimedia

Signed

Unsigned

Packed

Unpacked

BCD

ASCII

ieee-754-std

f = (-1)^s*1.m*2^(e-b)

b: bias

e: exponent

s: Vorzeichen

m: mantisse

direkte Addressierung

Indirekte Addressierung

Absolute Addressierung

Immidiate

Direktwert

Indirekte Addressierung mit Verschiebung

indirkte Addressierung mit Autoinkrement/dekrement

Indizierte Addresierung

Indizierte Addressierung mit Verschiebung

Displacemenet

Steuereinheit

1.) Befehlsdekodierer

2.) Funktionsdekodierer

MemToReg

memWrite

Branch

ALU-Src

RegDst

RegWrite

ALU-OP

Befehlsdekodierer

RegDst

RegWrite

ALU-Op

ALU-Src

MemToReg

MemWrite

Branch

Funktionsdekodierer

Func

ALU-Op

ALU-Operation

Befehlsekodierer

Funktionsdekodierer

Registersatz

ALU

datenspeicher

Befehlsspeicher

Befehlszaehler

Vorzeichenerweiterungseinheit

4 x MUX

1 x AND

2 x Addierer

1 x 2 Bit Shifter

Register:

Lese-Register-1

Lese-Register-2

Schreiberegister

Lese-Daten-1

Lese-Daten-2

Schreibedaten

WE

Speicher

Addresse

Lesedaten

Schreibedaten

We

ALU:

ALU

AND:

PC-Src

Befehlszaehler:

PC (t)

PC (t+1)

Befehlsspeicher

Lesedaten

Schreibedaten

ALU-Op Func ALU-Operation

00 x 010 - add

x1 x 110 - sub

1x 100 - 000 010 - add

OpCode RegDst RegWrite Branch ALU-Src MemToReg MemWrite ALU-Op

r-typ 000 000 1 1 0 0 0 0 10

Verzweigungsbefehle

1.) Bedingt

2.) Bedingt

eq - equal

ne - not equal

gt - greater than

ge - greater than equal

lt - less than

le - less than equal

1.) Absolut

2.) Befehlssrelativ

3.) ... lernen nachgucken weiss nicht genau

Branch

Jump

PC_neu = PC_alt + (i << 2)

PC_neu = PC_alt & 0xf000 0000 | (I << 2)

Nachgucken

jb, jb*, jr

jal, jalr

beq, bne

beqz*, bnez*

ble*, blt*

blez, bltz

bgt*, bge*

bgtz, bgez

Befehlsspeicher

Befehlszaehler

Registersatz

Datenspeicher

Stackarchitektur: 8087, Intel ATAM 862, Atmel

1.) Befehl holen, instruction fetch

2.) Befehl dekodieren, instruction decode/register fetch

3.) Befehl ausfuehren, Execute Address Calculation

4.) Speicherzugriffsphase, Mem Memory Access

5.) WB Resultatsspeicherphase

IF, ID, EX, MEM, WB

1.) VLIW = very long instruction

2.) OOE Out Of Order Issue Out of Order Execution

3.) In Order Issue in Order Completion

1.) Ein bit Praediktor

1.1.) Predict Taken, Not Taken

1.2.) Predict Strongly, weakly Taken Not Taken

Inhalt, Kapitel

Schalnetze

Schaltwerke

Komplexe Schaltwerke

Aufbau und Funktionsweise eines Computers

Schaltnetze

Boolsche Algebra

Definition der Booleschen Algebra

Schaltalgebra ein Modell der Booleschen Algebra

Schaltfunktionen

Definition

Darstellung

Minimierung

Analyse von Schaltnetzen

Synthese von Schaltnetzen

Wort - Glieder??

Kodierglieder

Schaltnetzentwurf fuer die 8421-BCD- zu sieben Segment Umsetzumsetzung

Schaltnetzentwurf fuer einen Addresskodierer

Komperatoren

Multiplexer

Addierer

Zahlendarstellung und zweierkomplement

Addierer/subtrahierer

ALU

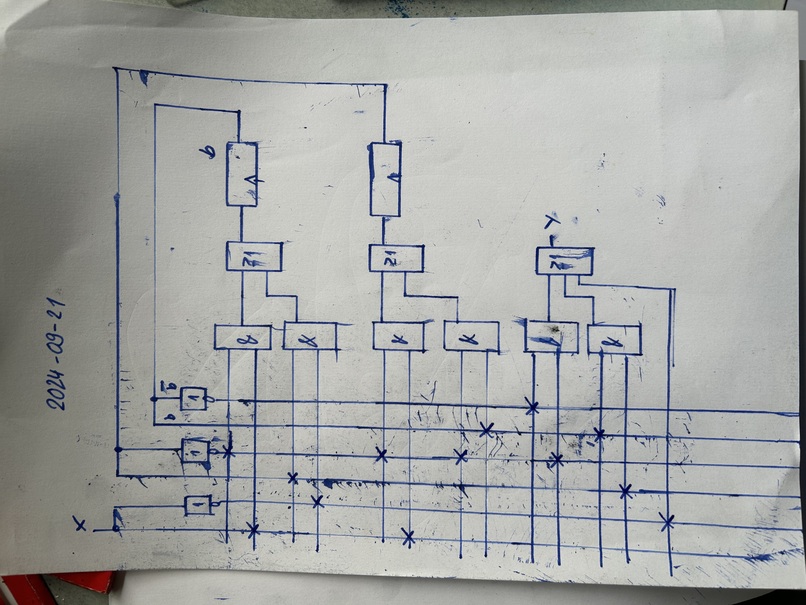

Programmierbare Logikbausteine

PROM

EPROM

PAL

PLA

Schaltwerke

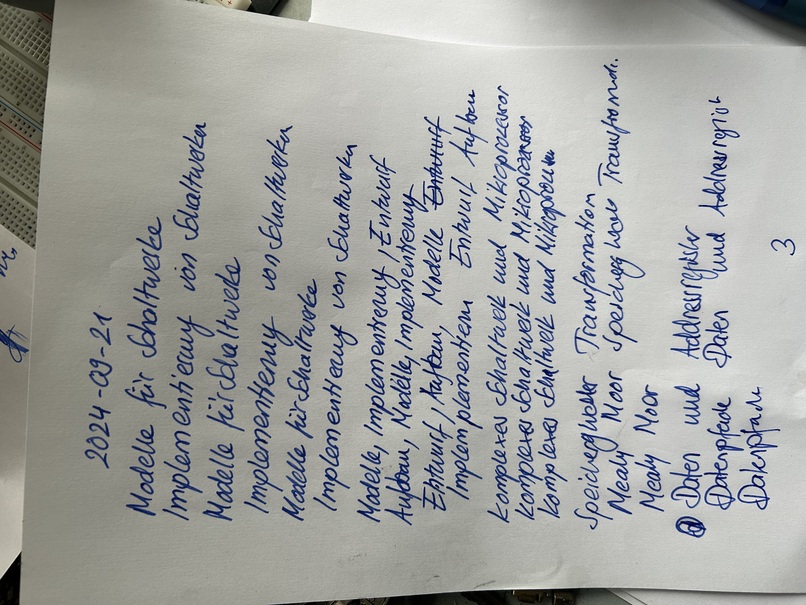

Entwurf von Schaltwerken

Implementierung von Schaltwerken

Synthese von Schaltwerken

Analyse von Schaltwerken

Aufbau Komplexer Schaltwerke

Speichergliedr

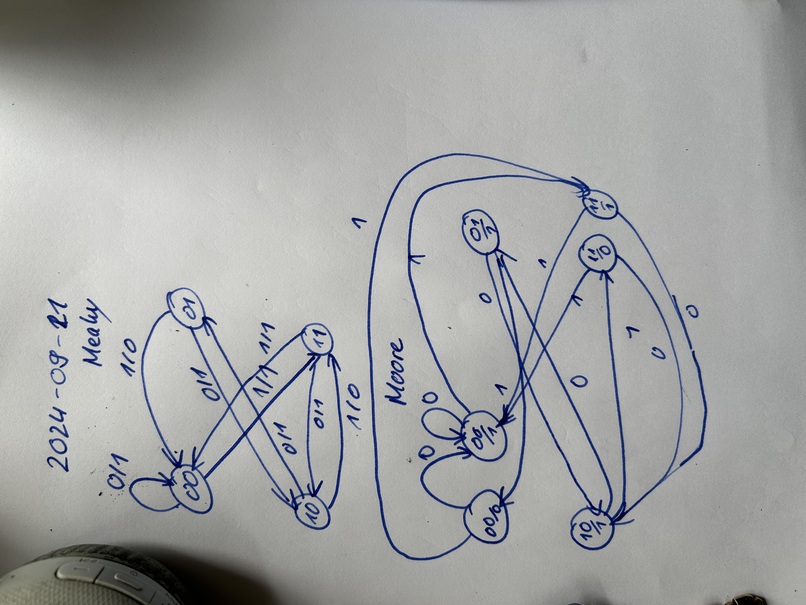

Transformation mealy und moore

Komplexe schaltwerke

Entwurf komplexer Schaltwerk

RTL-Notation

ASM-Diagramme

Aufbau ud Funktionsweise eines computers

Beispiel einsen Zaehler

Loesung mit komplexen Moore Schaltwerk

Loesung mit komplexen Mealy schaltwerk

Moore Steuerwerk als konventionelles Schalwerk

Moore Steuerwerk mit HotOne Kodierung

mealy Steuerwerk als konventielles Schaltwerk

Mealy Steuewerk mit HoOne Kodierung

Mikroprogrmmiertes Steuerwerk

Aufbau und Funktionsweise eines Computers

Erweiterung komplexer Schaltwerke

Komponenten eines Computers

rechenwerk

Leitwerk

Speicher

Ein und Ausgabe

Unterprogramme, Unterbrechungen Interruptes

Interne und externe Daten

Rechenwerk

Registersatz

ALU

Arithmetische Operationen

Logische Operationen

Schiebemultiplexer

Steuerwerk

Hier fehlen ein paar Sachen, genauer machen, vom Wortlaut

Schaltnetze: sind elektronische Schaltungen, die Spannungen als logische Variablen 0 und 1 interpretieren

Schaltnetz: Definition DIN 44300/93

Schaltfunktion: DIN 44300/87

boolsche Algebra, Schaltalgebra

Eingangsvektor, Ausgangsvektor

Eingangsvariablen, x0, x1, ..., xn

Eingangsvektor

Schaltnetz Ausgangsetor

Boolsche Algebra, Schaltalgebra

f:{0,1}^m->{0,1}^n

Schaltfunktion, Vektorfunktion

Schaltalgebra ein Boolschen Algebra

Boolsche Algbra ist eine Algebraische Struktur

Schaltalgbra ist Boolesche Algbra ueber der Menge {0,1}

1.) Menge B={0,1}

2.) Verknuepfungen

wedge, vee

3.) Es gelten die gesetze der Boolschen Algebra

Assoziativgesetz

Distributivgesetz

Kommutivgesetz

Absorbtionsgesetz

neutrales element

inverses Element

De Morgan

Neutralitaet?

AND - Konjunktion

OR - Dijunktion

Transfer

Antivalenz

Inhibition

Aequivalenz

Null

Eins

fehlt was

Komperator, Schaltfunktion, Rechenelement: DIN 40700

Kodierer: zuordnung des Zeichen eines Zeichenvorrats zu dem Zeichen eines anderen zeichenvorrats

Dekodierer: Kodierer, mit mehreren ein und Ausgaengen, bei denen fuer jede Kombinition von Eingangssignalen immer nur je ein Ausgang das Signal 1 annimmt

kodierer: DIN44300/118

Dekodierer: diN 44300/121

Addierer

S = A XOR B XOR C

U = A AND B OR (A OR B) AND C

PLHS 18P8

b a x b a y 0 0 0 0 0 0 1 1 0 0 1 1 1 1 2 0 1 0 1 0 1 3 0 1 1 0 0 0 4 1 0 0 0 1 1 5 1 0 1 1 1 0 6 1 1 0 1 0 1 7 1 1 1 0 0 1 b a x b 1 0 0 1 1 2 0 1 0 1 5 1 0 1 1 6 1 1 0 1 b a x a 1 0 0 1 1 4 1 0 0 1 5 1 0 1 1 b a x y 0 0 0 0 1 1 0 0 1 1 2 0 1 0 1 4 1 0 0 1 6 1 1 0 1 7 1 1 1 1 b a x b Gruppe 1: 1 0 0 1 1 2 0 1 0 1 Gruppe 2: 5 1 0 1 1 6 1 1 0 1 b a x a Gruppe 1: 1 0 0 1 1 4 1 0 0 1 Gruppe 2: 5 1 0 1 1 b a x y Gruppe 0: 0 0 0 0 1 Gruppe 1: 1 0 0 1 1 2 0 1 0 1 4 1 0 0 1 Gruppe 2: 6 1 1 0 1 Gruppe 3: 7 1 1 1 1 b a x b Gruppe 1: 1 0 0 1 1 2 0 1 0 1 Gruppe 2: 5 1 0 1 1 6 1 1 0 1 1:5 - 0 1 2:6 - 1 0 b <= (not a and x) or (x and not x) b a x a Gruppe 1: 1 0 0 1 1 4 1 0 0 1 Gruppe 2: 5 1 0 1 1 1:5 - 0 1 4:5 1 0 - a <= (not a and x) or (b and not a) b a x y Gruppe 0: 0 0 0 0 1 Gruppe 1: 1 0 0 1 1 2 0 1 0 1 4 1 0 0 1 Gruppe 2: 6 1 1 0 1 Gruppe 3: 7 1 1 1 1 0:1 0 0 - 0:2 0 - 0 0:4 - 0 0 2:6 - 1 0 4:6 1 - 0 6:7 1 1 - 0:1 0 0 - 6:7 1 1 - 0:2 0 - 0 4:6 1 - 0 0:4 - 0 0 2:6 - 1 0 0:1 0 0 - 6:7 1 1 - 0:2:4:6 - - 0 0 1 2 4 6 7 0:1 - - 6:7 - - 0:2:4:6 - - - - y <= (not b and not a) or (b and a) or (not x) a <= (not a and x) or (b and not a) b <= (not a and x) or (x and not x) y <= (not b and not a) or (b and a) or (not x)

bash

#!/bin/bash

if [[ "$1" == "David" && "$2" == "Vajda" ]]

then

echo "Das bin ich"

elif [[ "$1" == "Vajda" && -z "$2" ]]

then

echo "Das koennte ich sein"

else

echo "Hallo Welt"

i=0

while [ $i -lt 10 ]

do

echo "Hallo zum $(($i+1))"

i=$(($i+1))

done

A=(a b c d)

A+=(e f g h)

i=0

while [ $i -lt 8 ]

do

echo "${A[$i]}"

i=$(($i+1))

done

for s in "${A[@]}"

do

echo "$s"

done

/bin/bash "$0" "David" "Vajda"

/bin/bash "$0" "Vajda"

fi

Hallo Welt Hallo zum 1 Hallo zum 2 Hallo zum 3 Hallo zum 4 Hallo zum 5 Hallo zum 6 Hallo zum 7 Hallo zum 8 Hallo zum 9 Hallo zum 10 a b c d e f g h a b c d e f g h Das bin ich Das koennte ich sein

;; Das scheint funktioniert zu haben, aus dem Kopf

.include "m8def.inc"

ldi r16, 0xff

out DDRB, r16

ldi r16, 0x00

out PORTB, r16

end: rjmp end

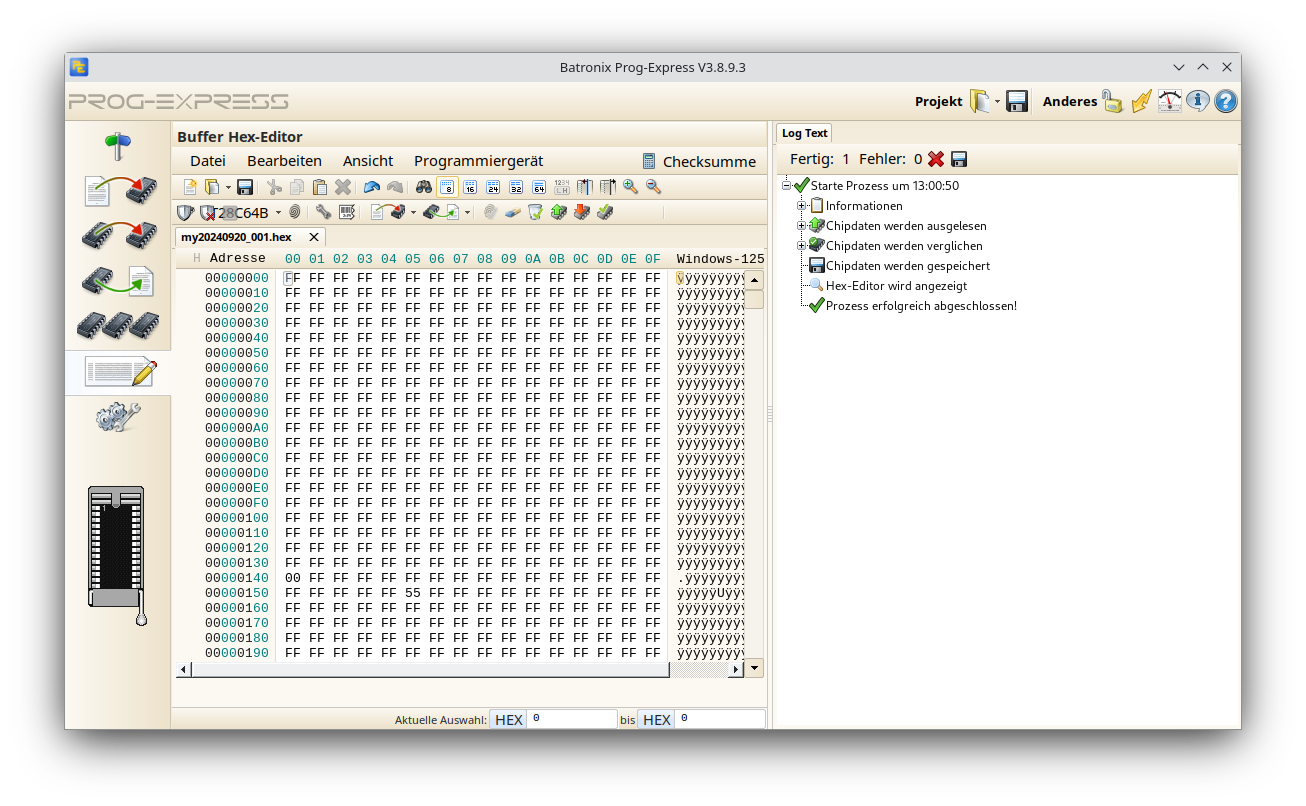

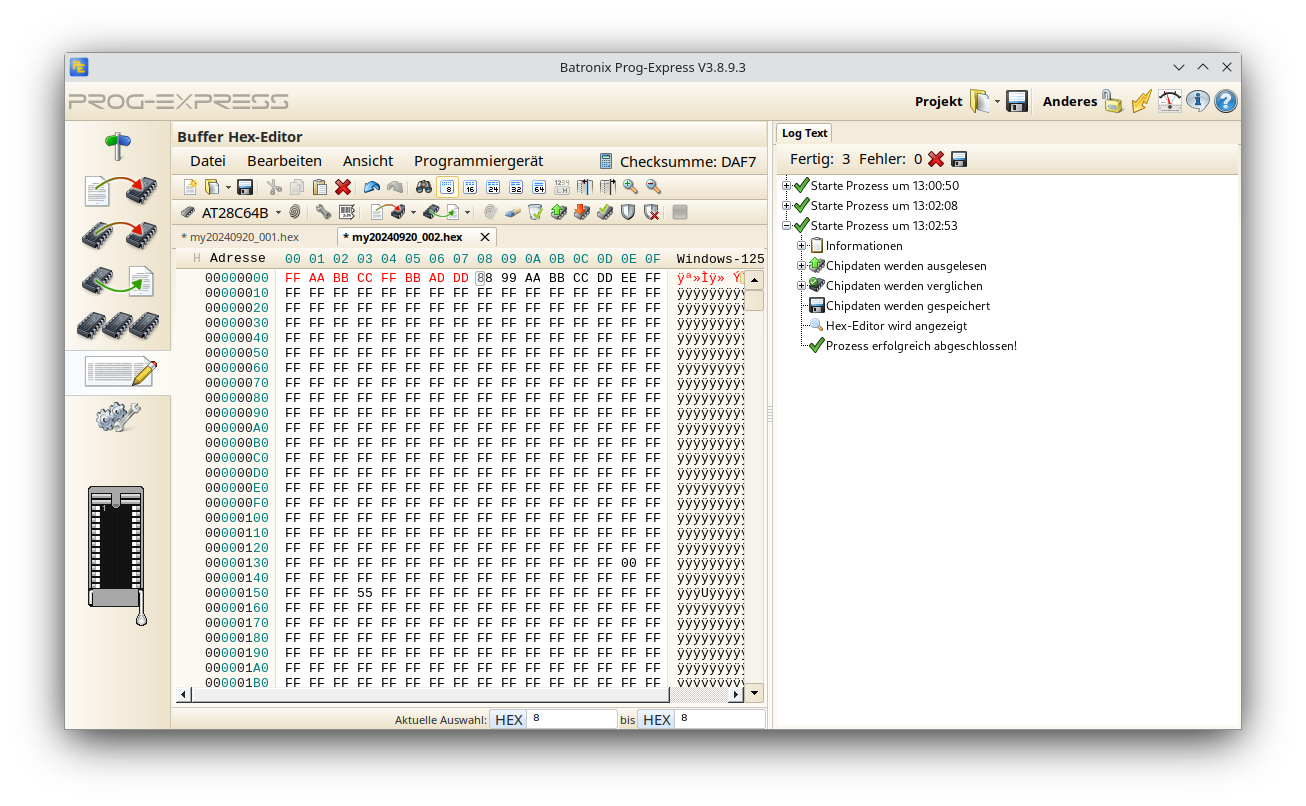

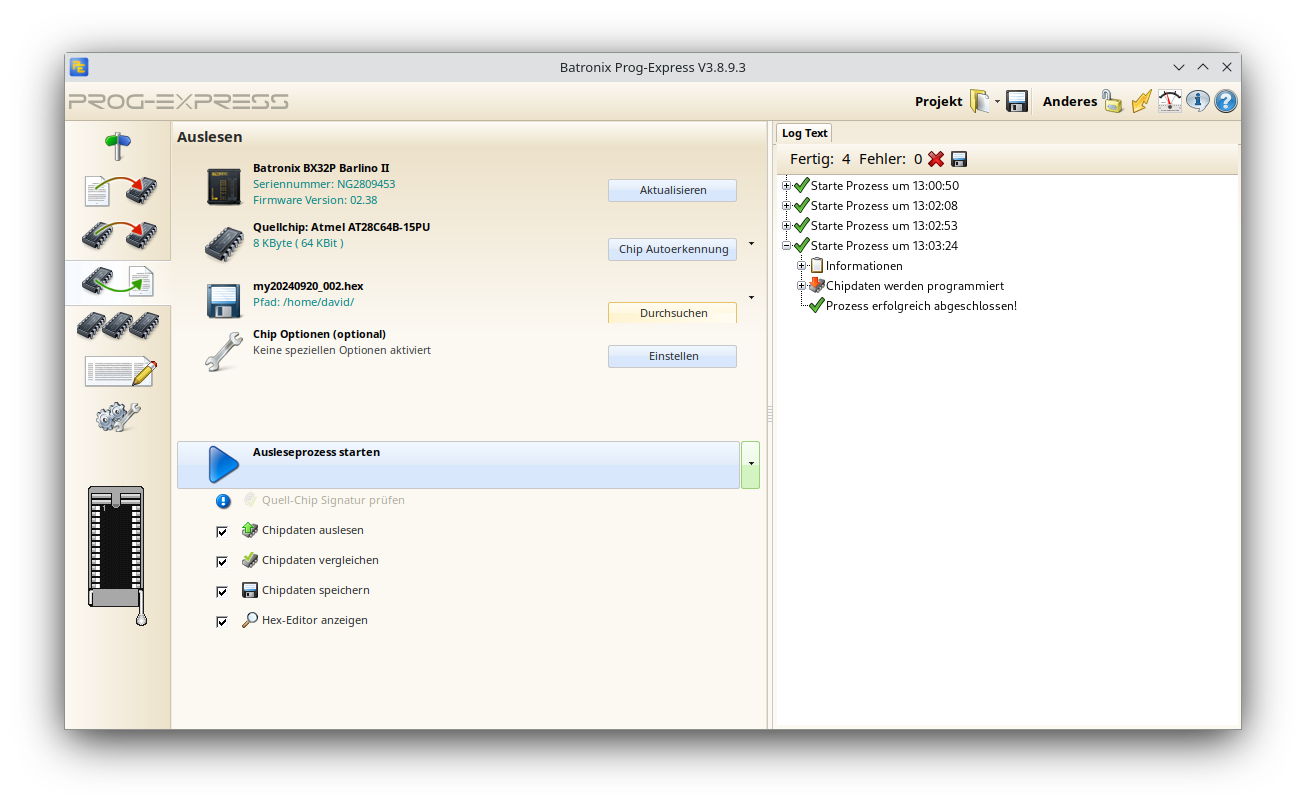

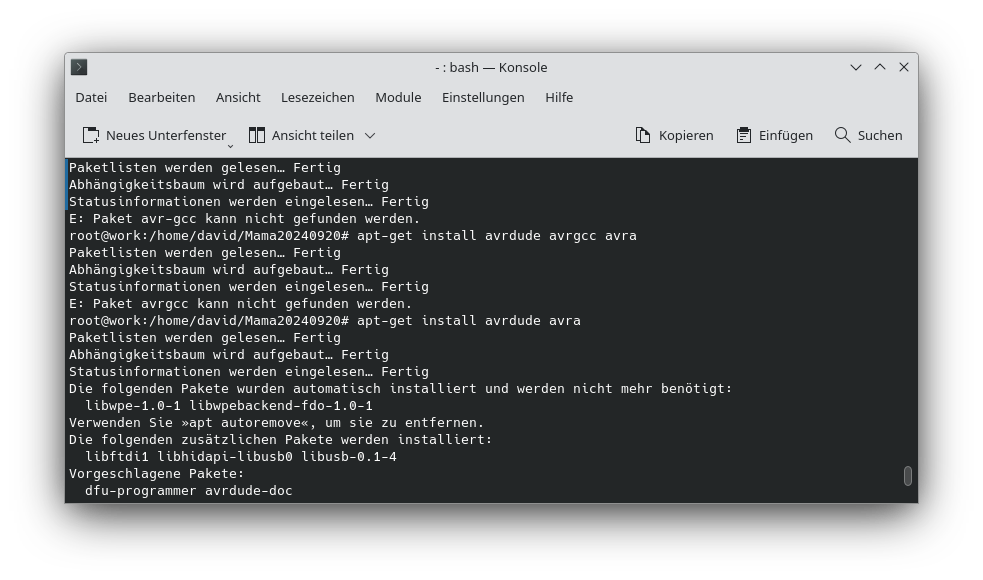

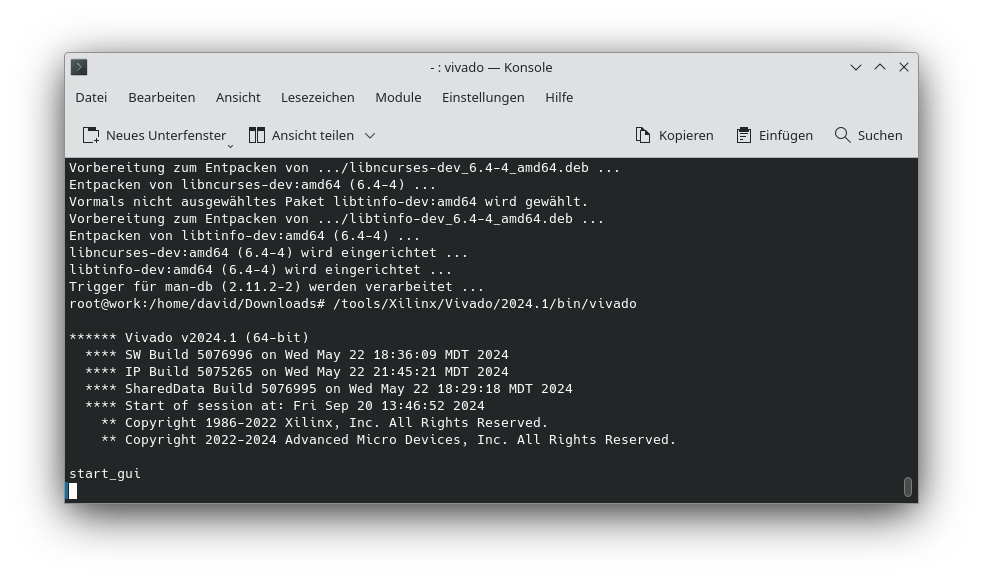

; david@work:~$ avra m820240921.asm

; david@work:~$ avrdude -c stk500 -p atmega8 -U flash:w:m820240921.hex -P /dev/ttyUSB0

.include "m8def.inc"

ldi r16, 0xff

out DDRB, r16

ldi r16, 0x00

todoagain:

com r16

out PORTB, r16

com r16

ldi r17, 0xff

slowmotion1:

dec r17

ldi r18, 0xff

slowmotion2:

dec r18

;ldi r19, 0xff

;slowmotion3:

; dec r19

; cpi r19, 0x00

; brne slowmotion3

cpi r18, 0x00

brne slowmotion2

cpi r17, 0x00

brne slowmotion1

inc r16

rjmp todoagain

end: rjmp end

und:

.include "m8def.inc"

ldi r16, 0xff

out DDRB, r16

ldi r16, 0x01

todoagain:

com r16

out PORTB, r16

com r16

ldi r17, 0xff

slowmotion1:

dec r17

ldi r18, 0xff

slowmotion2:

dec r18

;ldi r19, 0xff

;slowmotion3:

; dec r19

; cpi r19, 0x00

; brne slowmotion3

cpi r18, 0x00

brne slowmotion2

cpi r17, 0x00

brne slowmotion1

rol r16

mov r21, r16

andi r21, 0b10000000

ror r21

ror r21

ror r21

ror r21

ror r21

ror r21

ror r21

ror r21

or r16, r21

rjmp todoagain

end: rjmp end