Nächste Seite: Matrizenmultiplikation Aufwärts: 2024-11-28 Vorherige Seite: Ripple Carry Chain Adder

-- (C) David Vajda

-- Ripple Carry Chain Adder / Subtrahierer / Volladdierer

-- 2024-11-28

library ieee;

use ieee.std_logic_1164.all;

entity fulladder20241128 is

port (

a: in std_logic;

b: in std_logic;

c: out std_logic;

s: in std_logic;

t: out std_logic

);

end;

architecture behaviour of fulladder20241128 is

begin

c <= a xor b xor s;

t <= (a and b) or ((a or b) and s);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarrychainadder20241128 is

port (

a3, a2, a1, a0: in std_logic;

b3, b2, b1, b0: in std_logic;

c3, c2, c1, c0: out std_logic;

s: in std_logic;

t: out std_logic

);

end;

architecture behaviour of ripplecarrychainadder20241128 is

component fulladder20241128

port (

a: in std_logic;

b: in std_logic;

c: out std_logic;

s: in std_logic;

t: out std_logic

);

end component;

signal s3, s2, s1, s0: std_logic;

begin

fa3: fulladder20241128 PORT MAP (a=>a3, b=>b3, c=>c3, s=>s3, t=>t);

fa2: fulladder20241128 PORT MAP (a=>a2, b=>b2, c=>c2, s=>s2, t=>s3);

fa1: fulladder20241128 PORT MAP (a=>a1, b=>b1, c=>c1, s=>s1, t=>s2);

fa0: fulladder20241128 PORT MAP (a=>a0, b=>b0, c=>c0, s=>s, t=>s1);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarrychainadder20241128testbench is

port (

c3, c2, c1, c0: out std_logic;

t: out std_logic

);

end;

architecture behaviour of ripplecarrychainadder20241128testbench is

component ripplecarrychainadder20241128

port (

a3, a2, a1, a0: in std_logic;

b3, b2, b1, b0: in std_logic;

c3, c2, c1, c0: out std_logic;

s: in std_logic;

t: out std_logic

);

end component;

signal a3, a2, a1, a0: std_logic;

signal b3, b2, b1, b0: std_logic;

signal s: std_logic;

begin

rfa: ripplecarrychainadder20241128 PORT MAP (a3=>a3, a2=>a2, a1=>a1, a0=>a0, b3=>b3, b2=>b2, b1=>b1, b0=>b0, c3=>c3, c2=>c2, c1=>c1, c0=>c0, s=>s, t=>t);

a3 <= '0' after 0 ns, '0' after 10 ns;

a2 <= '1' after 0 ns, '0' after 10 ns;

a1 <= '0' after 0 ns, '0' after 10 ns;

a0 <= '1' after 0 ns, '0' after 10 ns;

b3 <= '0' after 0 ns, '0' after 10 ns;

b2 <= '0' after 0 ns, '0' after 10 ns;

b1 <= '1' after 0 ns, '0' after 10 ns;

b0 <= '1' after 0 ns, '0' after 10 ns;

s <= '0' after 0 ns, '1' after 10 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity com20241128 is

port (

x3, x2, x1, x0: in std_logic;

y3, y2, y1, y0: out std_logic

);

end;

architecture behaviour of com20241128 is

begin

y3 <= not x3;

y2 <= not x2;

y1 <= not x1;

y0 <= not x0;

end;

library ieee;

use ieee.std_logic_1164.all;

entity neg20241128 is

port (

b3, b2, b1, b0: out std_logic;

a3, a2, a1, a0: in std_logic;

t: out std_logic

);

end;

architecture behaviour of neg20241128 is

component com20241128

port (

x3, x2, x1, x0: in std_logic;

y3, y2, y1, y0: out std_logic

);

end component;

component ripplecarrychainadder20241128

port (

a3, a2, a1, a0: in std_logic;

b3, b2, b1, b0: in std_logic;

c3, c2, c1, c0: out std_logic;

s: in std_logic;

t: out std_logic

);

end component;

signal c3, c2, c1, c0: std_logic;

signal d3, d2, d1, d0: std_logic;

signal s: std_logic;

begin

d3 <= '0';

d2 <= '0';

d1 <= '0';

d0 <= '0';

s <= '1';

com: com20241128 PORT MAP (x3=>a3, x2=>a2, x1=>a1, x0=>a0, y3=>c3, y2=>c2, y1=>c1, y0=>c0);

add: ripplecarrychainadder20241128 PORT MAP (b3=>d3, b2=>d2, b1=>d1, b0=>d0, a3=>c3, a2=>c2, a1=>c1, a0=>c0, s=>s, t=>t, c3=>b3, c2=>b2, c1=>b1, c0=>b0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity sub20241128 is

port (

a3, a2, a1, a0: in std_logic;

b3, b2, b1, b0: in std_logic;

c3, c2, c1, c0: out std_logic;

t: out std_logic

);

end;

architecture behaviour of sub20241128 is

component ripplecarrychainadder20241128

port (

a3, a2, a1, a0: in std_logic;

b3, b2, b1, b0: in std_logic;

c3, c2, c1, c0: out std_logic;

s: in std_logic;

t: out std_logic

);

end component;

component neg20241128

port (

b3, b2, b1, b0: out std_logic;

a3, a2, a1, a0: in std_logic;

t: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

signal s: std_logic;

begin

neg: neg20241128 PORT MAP (a3=>a3, a2=>a2, a1=>a1, a0=>a0, b3=>x3, b2=>x2, b1=>x1, b0=>x0);

add: ripplecarrychainadder20241128 PORT MAP (b3=>b3, b2=>b2, b1=>b1, b0=>b0, a3=>x3, a2=>x2, a1=>x1, a0=>x0, c3=>c3, c2=>c2, c1=>c1, c0=>c0, s=>s, t=>t);

s <= '0';

end;

library ieee;

use ieee.std_logic_1164.all;

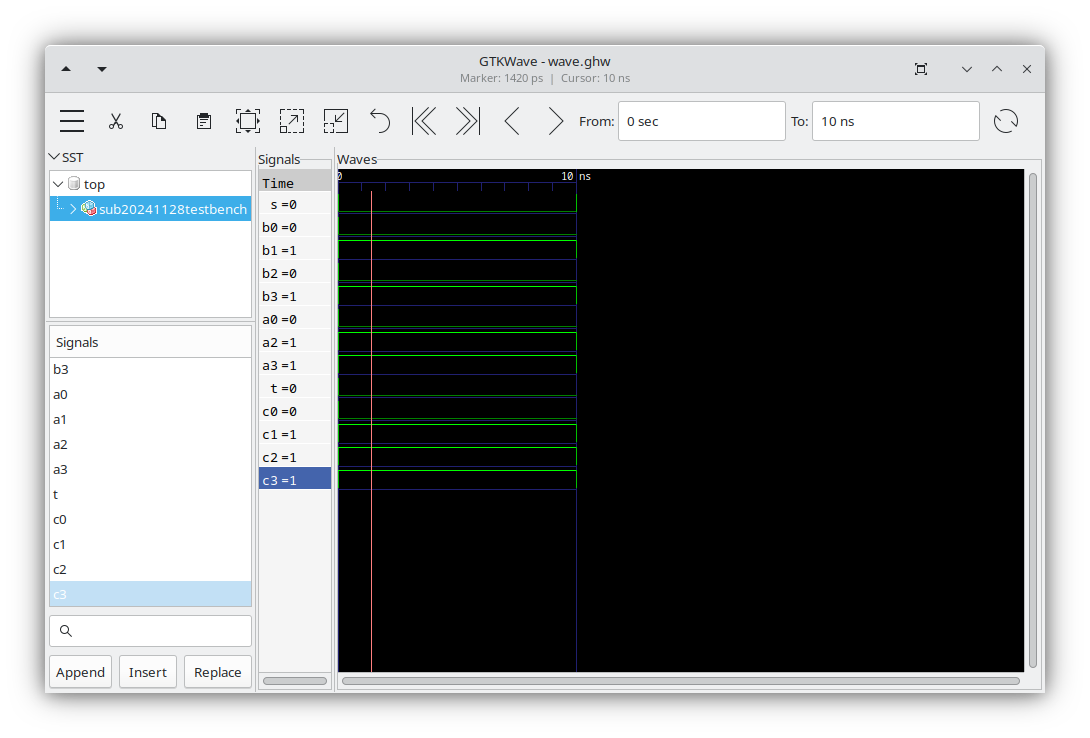

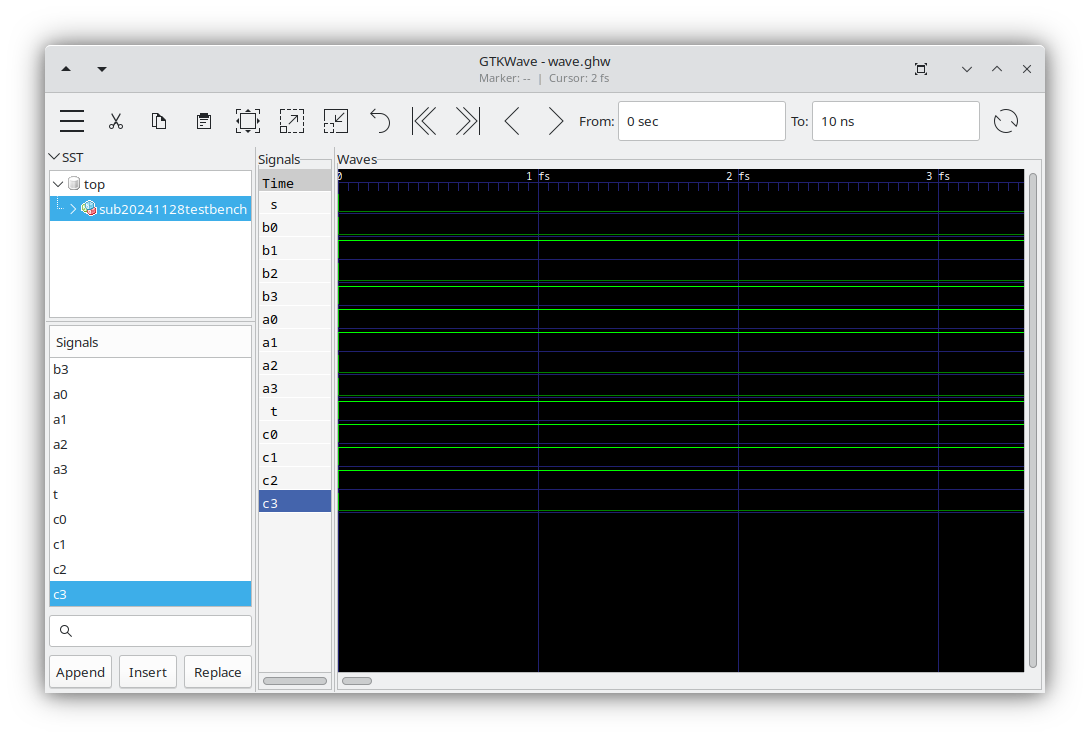

entity sub20241128testbench is

port (

c3, c2, c1, c0: out std_logic;

t: out std_logic

);

end;

architecture behaviour of sub20241128testbench is

component sub20241128

port (

a3, a2, a1, a0: in std_logic;

b3, b2, b1, b0: in std_logic;

c3, c2, c1, c0: out std_logic;

t: out std_logic

);

end component;

signal a3, a2, a1, a0: std_logic;

signal b3, b2, b1, b0: std_logic;

signal s: std_logic;

begin

sub: sub20241128 PORT MAP (a3=>a3, a2=>a2, a1=>a1, a0=>a0, b3=>b3, b2=>b2, b1=>b1, b0=>b0, c3=>c3, c2=>c2, c1=>c1, c0=>c0, t=>t);

a3 <= '0' after 0 ns, '0' after 10 ns;

a2 <= '0' after 0 ns, '0' after 10 ns;

a1 <= '1' after 0 ns, '0' after 10 ns;

a0 <= '1' after 0 ns, '0' after 10 ns;

b3 <= '1' after 0 ns, '0' after 10 ns;

b2 <= '0' after 0 ns, '0' after 10 ns;

b1 <= '1'after 0 ns, '0' after 10 ns;

b0 <= '0' after 0 ns, '0' after 10 ns;

s <= '0' after 0 ns, '1' after 10 ns;

end;

|