Nächste Seite: binary20251113.txt Aufwärts: Übungen Vorherige Seite: Übungen

1.) Rechne die Zahl in binaer Darstellung in eine Dezimale Darstellung um

1010110011011000b 44248d

2.) Rechne die Zahl in dezimal darstellung in eine Binaerdarstellung um

4397 0001000100101101

3.) Addiere die drei Zahlen schriftlich

17542

+ 54861

+ 46924

-----------------

119327

4.) Subtrahiere die letzten drei Zahlen schriftlich von der ersten schriftlich

1004

- 2238

- 11564

- 12902

-----------------

-25700

5.) Rechne die Zahl ins zweier komplement um, mit 8 Bit - und subtrahiere diese zahl von der ersten und rechne das Ergebnis nach dezimal

35 -57 = -22

00100011 11000111 = 11101010

6.) Multipliziere die zwei Zahlen schriftlich

12665*861 = 10904565

7.) Dividiere die zwei Zahlen schriftlich

36828/25999 = 1

8.) Errechne x Logarithmisch mit dem Taschenrechner

3419^x = 625972695

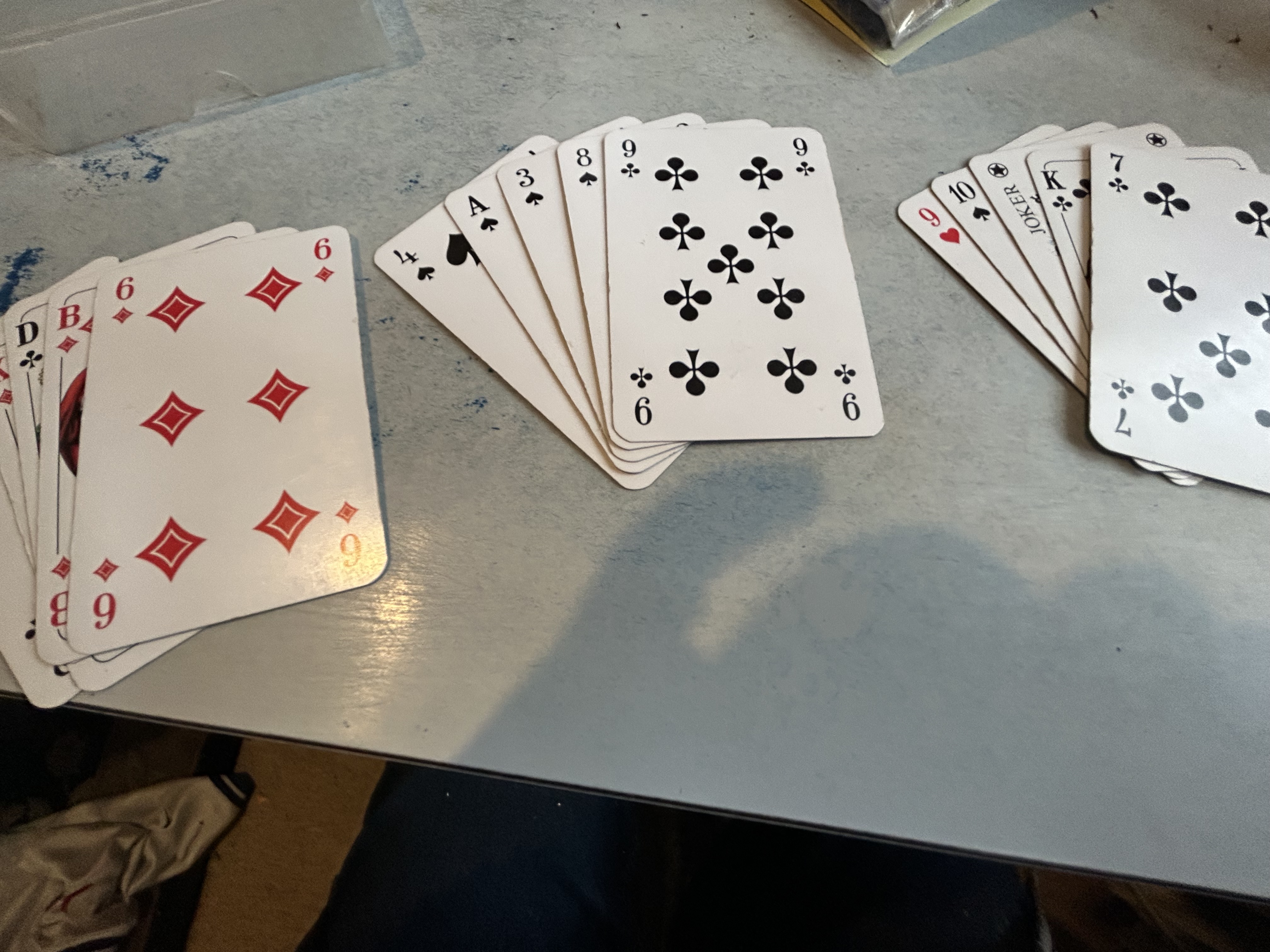

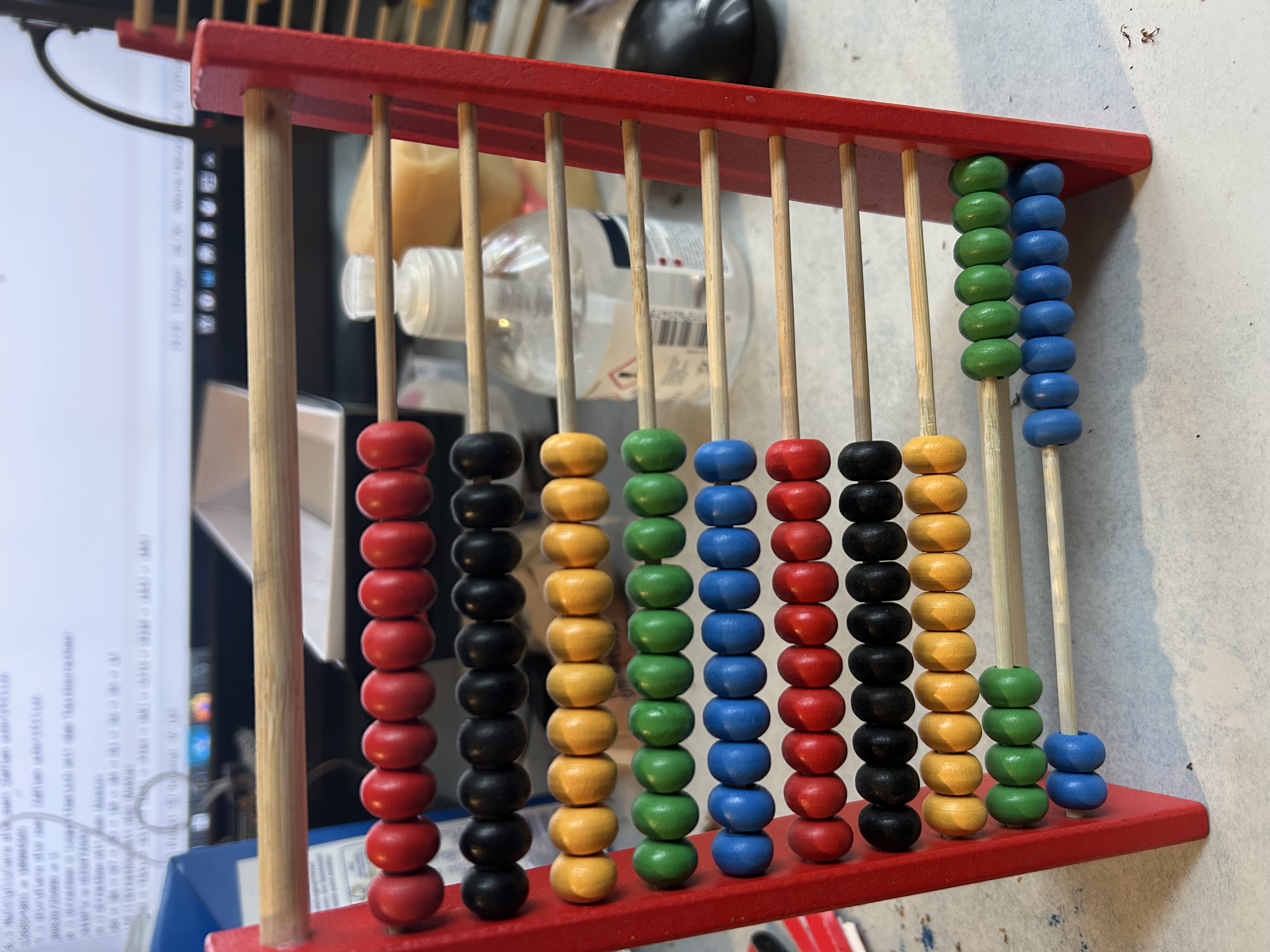

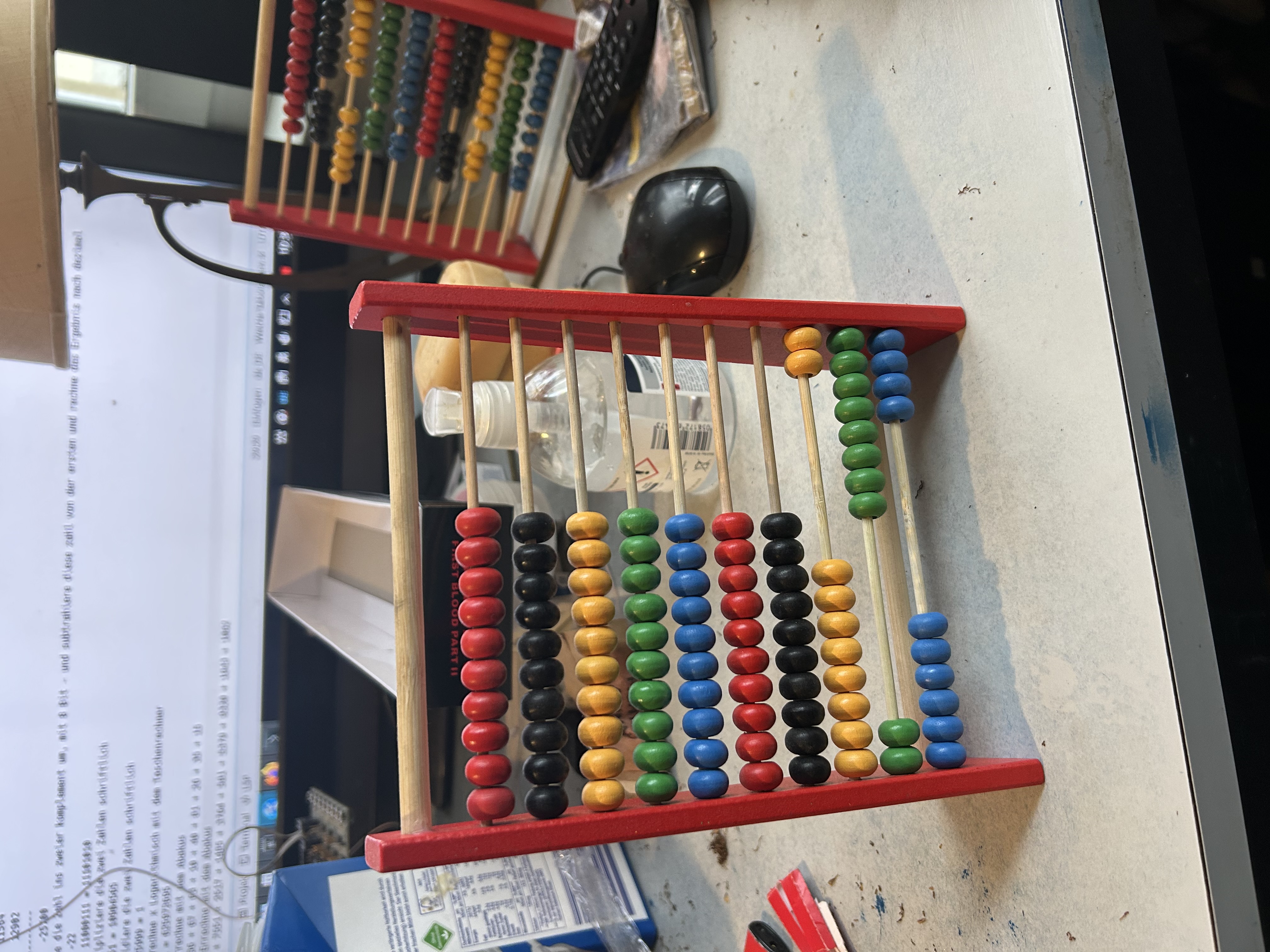

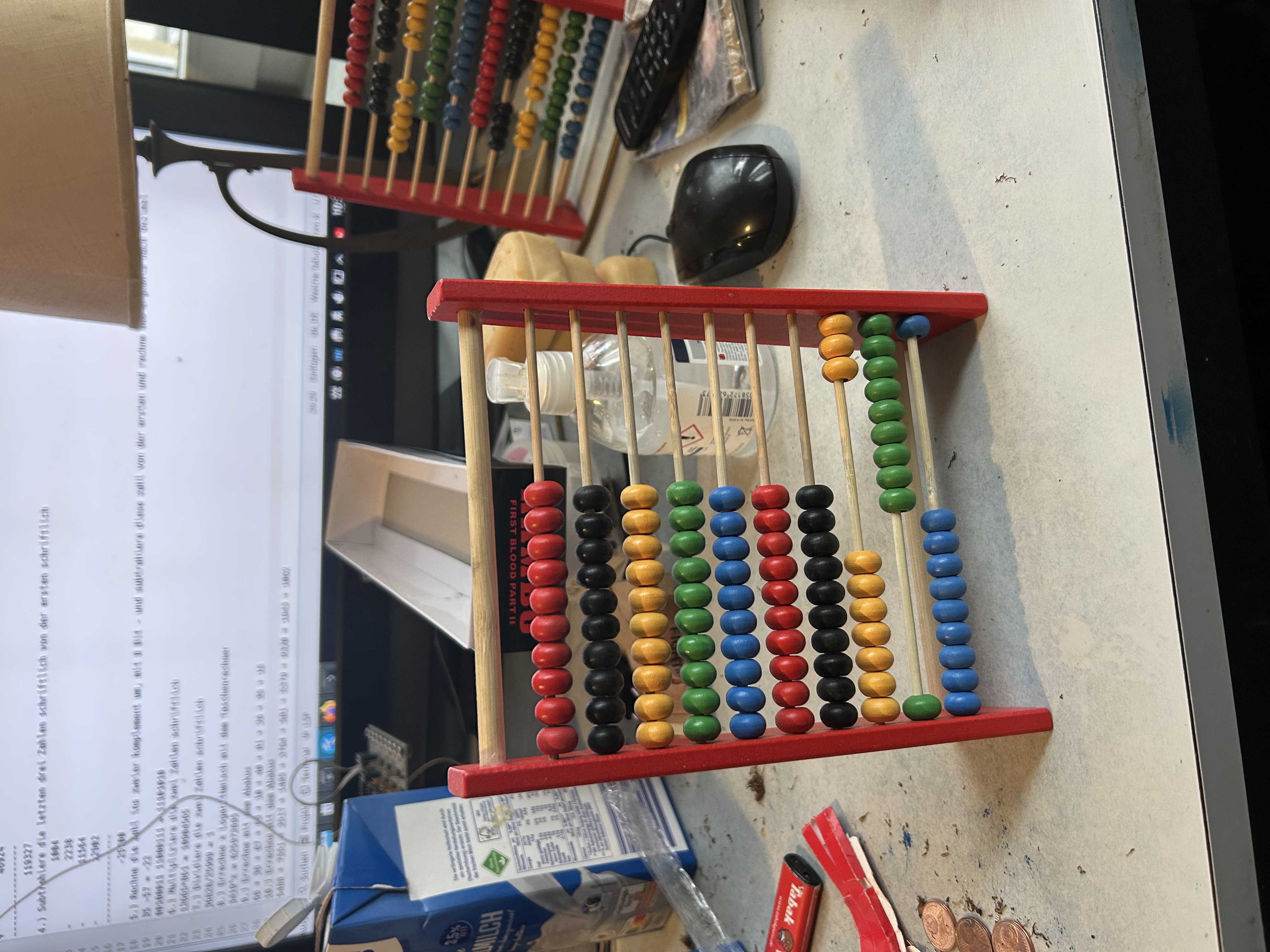

9.) Errechne mit dem Abakus

68 + 36 + 67 + 63 + 10 + 40 + 81 + 26 + 35 + 15

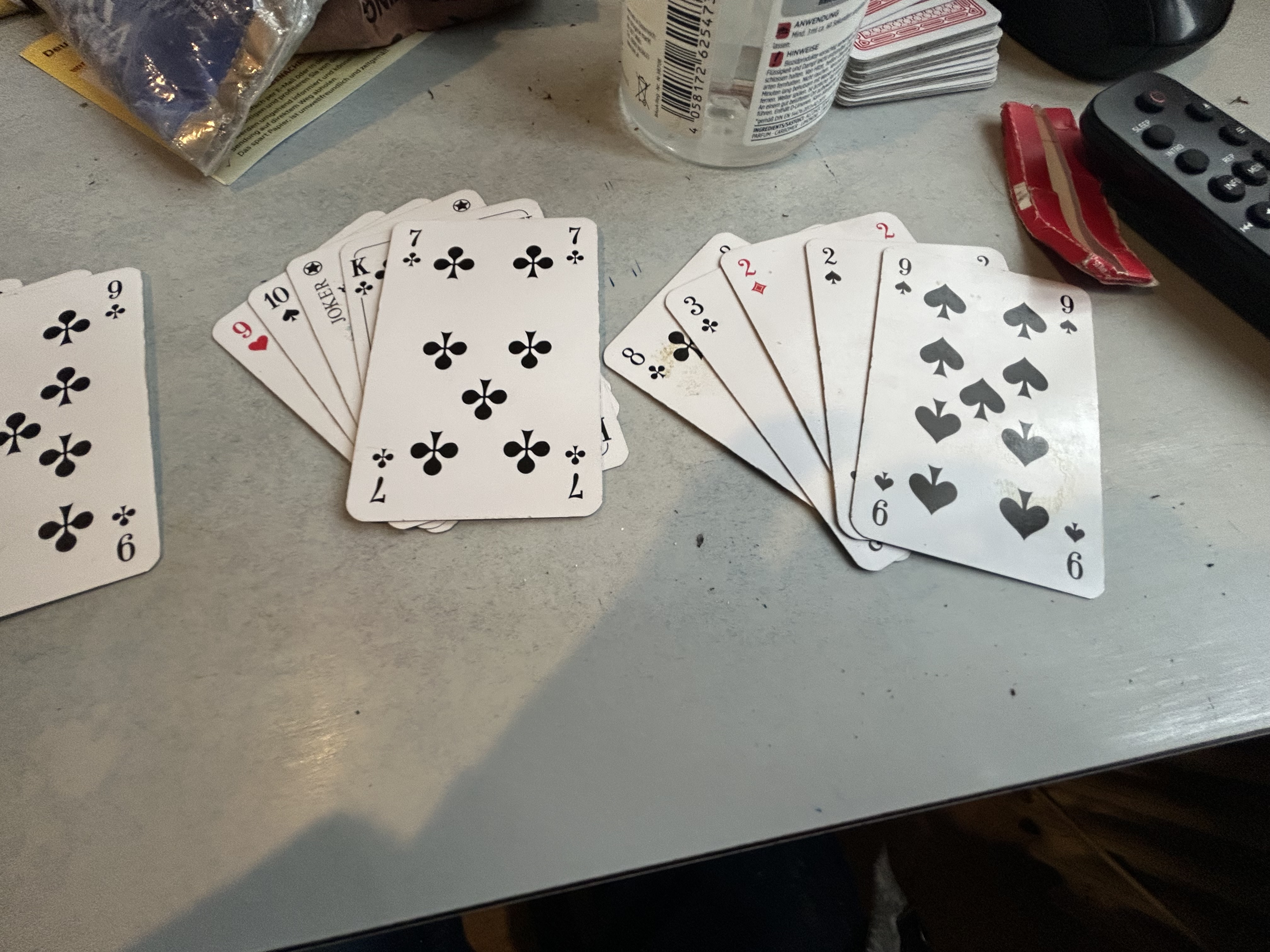

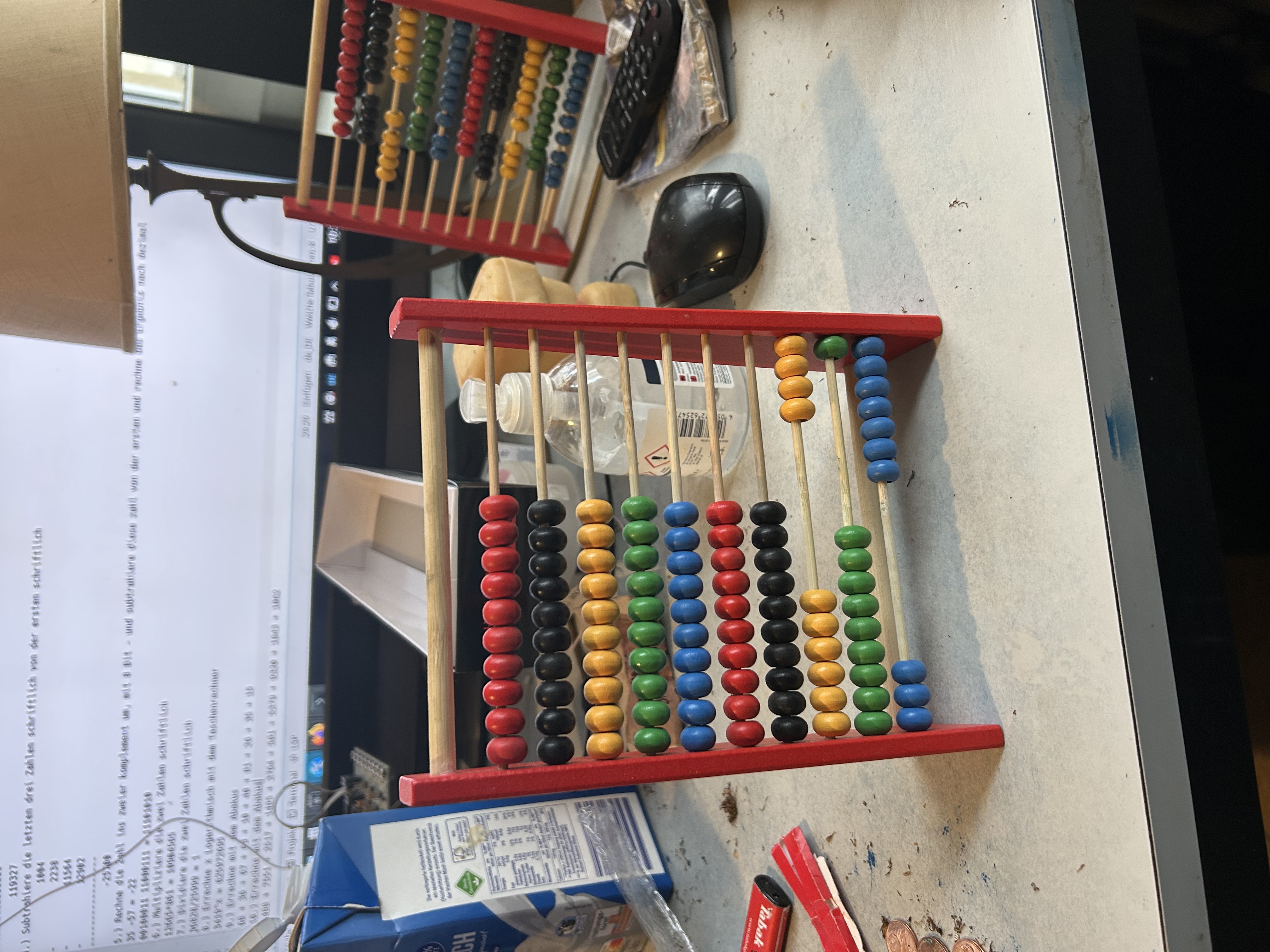

10.) Errechne mit dem Abakus

5488 + 7551 + 2517 + 1485 + 3764 + 581 + 5379 + 9320 + 1843 + 1062

|