Nächste Seite: m820250116extint.asm Aufwärts: Übungen Vorherige Seite: index20250111.html

<html>

<head><title>David Vajda</title></head>

<body>

<style>

ul {

list-style-image: url("Tux32.png");

list-style:none;

background-color: yellow;

}

li {

color:black;

background-image: url("Tux32.png");

background-repeat: no-repeat;

background-color: pink;

text-decoration: none;

/*background: #eee;*/

border: 1px solid #ccc;

padding:20px 30px;

margin: 20px;

/*display:block;*/

/*width: 20%;*/

float: left;

}

li:hover {

color:black;

background-image: url("Tux32.png");

background-repeat: no-repeat;

background-color: white;

text-decoration: none;

/*background: #eee;*/

border: 1px solid #ccc;

padding:20px 30px;

margin: 20px;

/*display:block;*/

/*width: 20%;*/

float: left;

}

a {

color: white;

text-shadow: 1px 1px 2px black, 0 0 25px blue, 0 0 5px darkblue;

font-family: "Times New Roman", Times, serif;

text-decoration: none;

}

a:hover {

color: deepskyblue;

text-shadow: 1px 1px 2px black, 0 0 25px blue, 0 0 5px darkblue;

font-family: "Times New Roman", Times, serif;

text-decoration: none;

}

.divA0 {

/*Ab dieser Stelle ist es abgeschrieben https://verpex.com/blog/website-tips/css-shapes-the-ribbon*/

--s: 50px; /* the ribbon size */

--d: 20px; /* the depth */

--c: 20px; /* the cutout part */

padding: 0 calc(var(--s) + var(--d)) var(--d); /* we need some padding so the text doesn't overlap the ribbon part */

background:

conic-gradient(at left var(--s) bottom var(--d),

#0000 25%,#0008 0 37.5%,#0004 0) 0 /50% no-repeat,

conic-gradient(at right var(--s) bottom var(--d),

#0004 62.5%,#0008 0 75%,#0000 0) 100%/50% no-repeat;

clip-path: polygon(0 var(--d), var(--s) var(--d),var(--s) 0,calc(100% - var(--s)) 0,calc(100% - var(--s)) var(--d),100% var(--d),calc(100% - var(--c)) calc(50% + var(--d)/2),100% 100%,calc(100% - var(--s) - var(--d)) 100%,calc(100% - var(--s) - var(--d)) calc(100% - var(--d)),calc(var(--s) + var(--d)) calc(100% - var(--d)),calc(var(--s) + var(--d)) 100%,0 100%,var(--c) calc(50% + var(--d)/2));

/*background-color: #CC333F; *//* the main color */

/*Bis zu dieser Stelle ist es abgeschrieben https://verpex.com/blog/website-tips/css-shapes-the-ribbon*/

clear: both;

font-size: 64px;

color: white;

background-color: pink;

font-family: 'Brush Script MT', cursive;

position: fixed;

z-index: 4; width: fit-content;

}

.divA1 {

width: 100%;

clear: both;

padding-top: 8%;

position: relative;

}

.divA2 {

width: 100%;

clear: both;

background-color: lightyellow;

}

.divA3 {

width: 100%;

clear: both;

background-color: lightgrey;

z-index: 0;

}

.divA4 {

width: 100%;

clear: both;

background-color: lightblue;

}

.divB1 {

width: 20%;

float: left;

margin: 5%;

}

.divB2 {

width: 100%;

float: left;

}

.divB3 {

width: 100%;

float: left;

}

.divB4 {

width: 100%;

float: left;

}

.divC3 {

width: 128px;

float: left;

margin: 5%;

}

.divPornHub {

background-color: black;

}

.divFacebook {

background-color: lightgrey;

}

.appbuttonimg {

width: 80%;

margin: 10%;

}

</style>

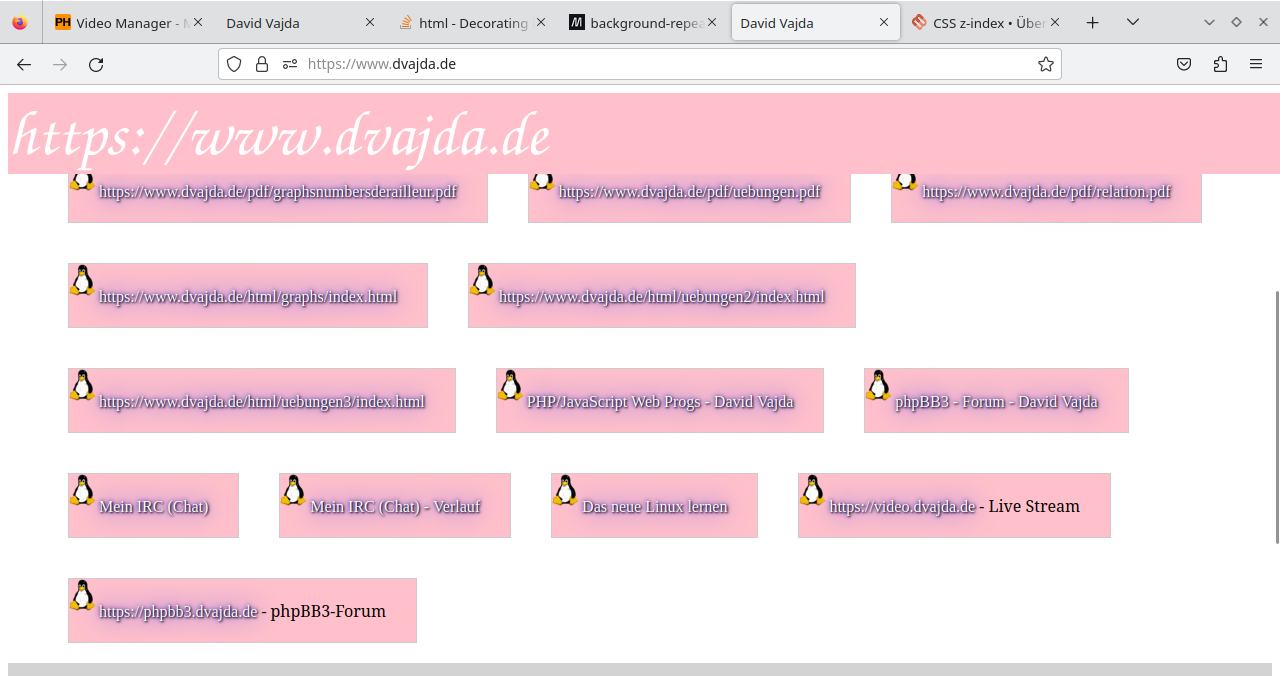

<div class="divA0">

https://www.dvajda.de

</div>

<div class="divA1">

<div class="divB1"><button type="button"><a href="./squirrelmail/"><img class="appbuttonimg" src="./sm_logo.png"></button></div>

<div class="divB1"><button type="button"><a href="./nextcloud/"><img class="appbuttonimg" src="./nextcloud.png"></button></div>

<div class="divB1"><button type="button"><a href="./phpBB3/"><img class="appbuttonimg" src="./phpbb3.jpeg"></button></div>

</div>

<div class="divA2">

<ul>

<li><a href="./../pdf/graphsnumbersderailleur.pdf">https://www.dvajda.de/pdf/graphsnumbersderailleur.pdf</a></li>

<li><a href="./../pdf/uebungen.pdf">https://www.dvajda.de/pdf/uebungen.pdf</a></li>

<li><a href="./../pdf/relation.pdf">https://www.dvajda.de/pdf/relation.pdf</a></li>

<li><a href="./../html/graphs/index.html">https://www.dvajda.de/html/graphs/index.html</a></li>

<li><a href="./../html/uebungen2/index.html">https://www.dvajda.de/html/uebungen2/index.html</a></li>

<li><a href="./../html/uebungen3/index.html">https://www.dvajda.de/html/uebungen3/index.html</a></li>

<li><a href="./../wwwprogs/list.html">PHP/JavaScript Web Progs - David Vajda</a></li>

<li><a href="./../phpBB3/">phpBB3 - Forum - David Vajda </a></li>

<li><a href="./../irc20240913/index.php">Mein IRC (Chat) </a></li>

<li><a href="./../irc20240913/irc.php">Mein IRC (Chat) - Verlauf </a></li>

<li><a href="./../html/uebungen2/node61.html"> Das neue Linux lernen </a></li>

<li><a href="https://video.dvajda.de">https://video.dvajda.de</a> - Live Stream</li>

<li><a href="https://phpbb3.dvajda.de">https://phpbb3.dvajda.de</a> - phpBB3-Forum</li>

</ul>

</div>

<div class="divA3">

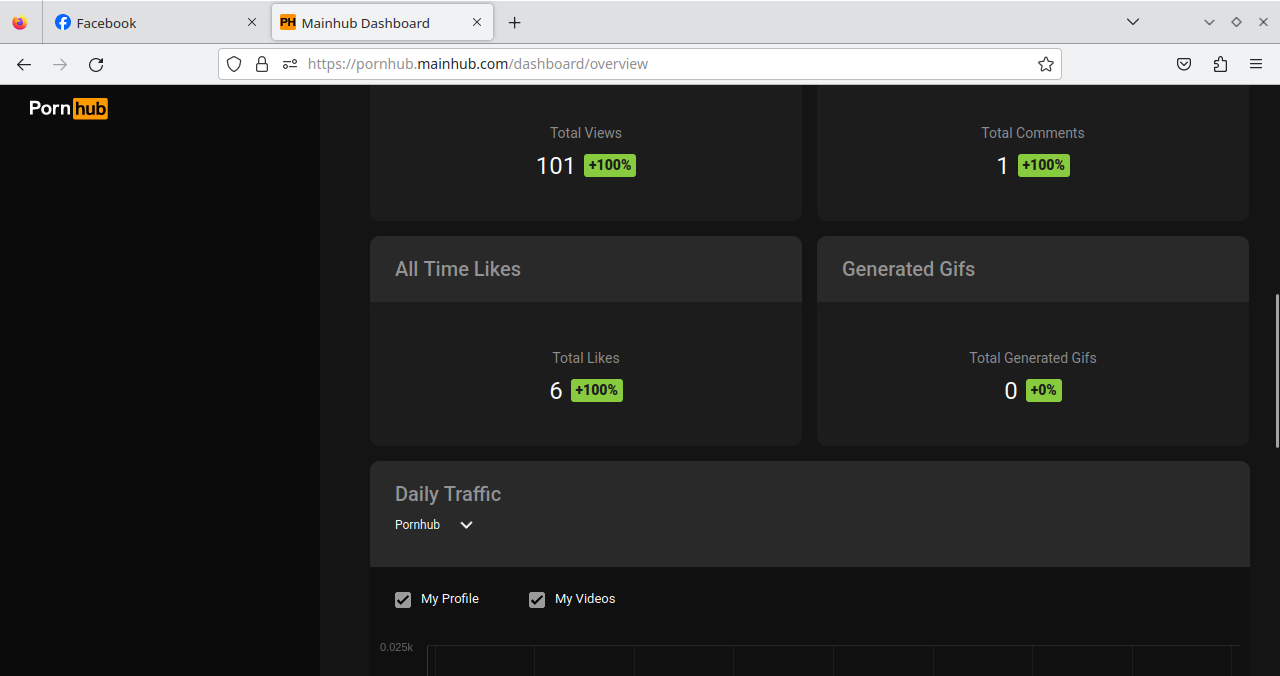

<div class="divC3"><a href="https://de.pornhub.org/model/2f2c1e5"><div class="divPornHub"><img src="pornhub_logo_straight.svg"></div>pornhub</a></div>

<div class="divC3"><a href="https://www.facebook.com/davevajda1983"><div class="divFacebook"><img src="FB-f-Logo__blue_58.png"></div>facebook</a></div>

<div>

<div class="divA4">

<address>

Written by <a href="mailto:david@dvajda.de">David Vajda</a><br>

Marienburgerstrasse 7<br>

D-72072, Germany<br>

</address>

</div>

</body></html>

|