Code: Alles auswählen

library ieee;

use ieee.std_logic_1164.all;

entity mycounter is

port

(

q0, q1, q2, q3: inout bit;

clk: inout bit

);

end;

entity FA is

port

(

a, b: in bit;

c: out bit;

uin: in bit;

uout: out bit

);

end;

entity ripple_carry_adder is

port

(

a0, a1, a2, a3: in bit;

b0, b1, b2, b3: in bit;

c0, c1, c2, c3: out bit;

uin: in bit; -- carry in

uout: out bit -- carry out

);

end;

entity my_rs_latch is

port

(

r, s: in bit;

q1, q2: inout bit

);

end;

entity clock_state_controlled_rs_latch is

port (

s, r: in bit;

c: inout bit;

q1, q2: inout bit

);

end;

entity clock_state_controlled_d_latch is

port (

d: in bit;

c: inout bit;

q1, q2: inout bit

);

end;

entity ms_d_flip_flop is

port (

d: in bit;

q: inout bit;

c: inout bit

);

end;

entity reg is

port

(

d0, d1, d2, d3: in bit;

q0, q1, q2, q3: inout bit;

c: inout bit

);

end;

architecture Behavioral of my_rs_latch is

begin

q1 <= (not r) nor q2;

q2 <= (not s) nor q1;

end Behavioral;

architecture Behavioral of clock_state_controlled_rs_latch is

component my_rs_latch

port

(

r, s: in bit;

q1, q2: inout bit

);

end component;

signal s1, r1: bit;

begin

r1 <= r and c;

s1 <= s and c;

rs: my_rs_latch port map (r=>r1, s=>s1, q1=>q1, q2=>q2);

end Behavioral;

architecture Behavioral of clock_state_controlled_d_latch is

component clock_state_controlled_rs_latch

port

(

r: in bit;

s: in bit;

q1, q2: inout bit;

c: inout bit

);

end component;

signal notd: bit;

begin

notd <= d;

rs: clock_state_controlled_rs_latch port map (r=>d, s=>notd, q1=>q1, q2=>q2, c=>c);

end Behavioral;

architecture Behavioral of ms_d_flip_flop is

component clock_state_controlled_d_latch

port

(

d: in bit;

q1, q2: inout bit;

c: inout bit

);

end component;

signal notc, d1: bit;

begin

dlatch1: clock_state_controlled_d_latch port map (d=>d, q1=>d1, c=>c);

notc <= not c;

dlatch2: clock_state_controlled_d_latch port map (d=>d1, q1=>q, c=>c);

end Behavioral;

architecture Behavioral of reg is

component ms_d_flip_flop is

port

(

d: in bit;

q: inout bit;

c: inout bit

);

end component;

begin

bit1: ms_d_flip_flop port map (d=>d0, q=>q0, c=>c);

bit2: ms_d_flip_flop port map (d=>d1, q=>q1, c=>c);

bit3: ms_d_flip_flop port map (d=>d2, q=>q2, c=>c);

bit4: ms_d_flip_flop port map (d=>d3, q=>q3, c=>c);

end;

architecture Behavioral of FA is

begin

c <= a xor b xor uin;

uout <= (a and b) or ((a or b) and uin);

end;

architecture Behavioral of ripple_carry_adder is

component FA

port

(

a, b: in bit;

c: out bit;

uin: in bit;

uout: out bit

);

end component;

signal u0, u1, u2: bit;

begin

fa1: FA port map (a => a0, b => b0, c => c0, uin => uin, uout => u0);

fa2: FA port map (a => a1, b => b1, c => c1, uin => u0, uout => u1);

fa3: FA port map (a => a2, b => b2, c => c2, uin => u1, uout => u2);

fa4: FA port map (a => a3, b => b3, c => c3, uin => u2, uout => uout);

end;

architecture Behavioral of mycounter is

component ripple_carry_adder

port

(

a0, a1, a2, a3: in bit;

b0, b1, b2, b3: in bit;

c0, c1, c2, c3: out bit;

uin: in bit; -- carry in

uout: out bit -- carry out

);

end component;

component reg

port

(

d0, d1, d2, d3: in bit;

q0, q1, q2, q3: inout bit;

c: inout bit

);

end component;

signal a0, a1, a2, a3 : bit; -- addierer Eingang1

signal b0, b1, b2, b3 : bit; -- addierer Eingang2

signal c0, c1, c2, c3 : bit; -- addierer Ausgang

signal uin, uout: bit;

begin

a0 <= '1';

a1 <= '0';

a2 <= '0';

a3 <= '0';

uin <= '0';

myreg : reg port map (d0 => c0, d1 => c1, d2 => c2, d3 => c3, q0 => b0, q1 => b1, q2 => b2, q3 => b3, c => clk);

rpcadd: ripple_carry_adder port map

(

a0 => a0, a1 => a1, a2 => a2, a3 => a3,

b0 => b0, b1 => b1, b2 => b2, b3 => b3,

c0 => c0, c1 => c1, c2 => c2, c3 => c3,

uin => uin, uout => uout

);

q0 <= c0;

q1 <= c1;

q2 <= c2;

q3 <= c3;

end;

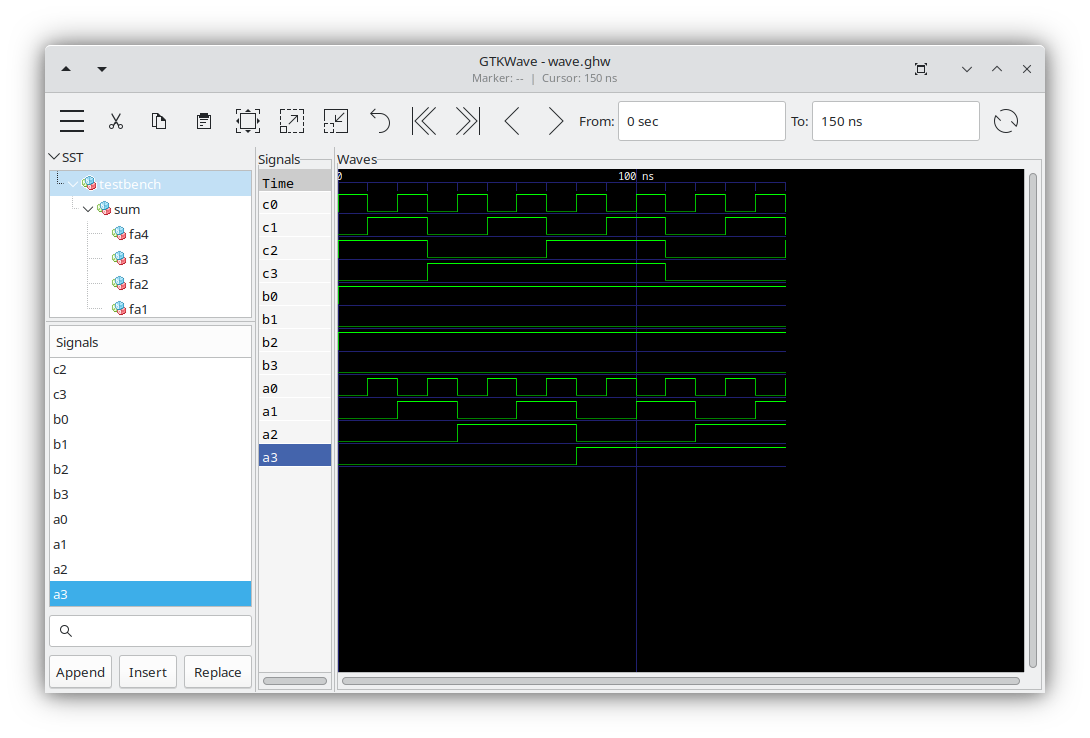

entity testbench is

end entity testbench;

architecture behave of testbench is

component ripple_carry_adder

port

(

a0, a1, a2, a3: in bit;

b0, b1, b2, b3: in bit;

c0, c1, c2, c3: out bit;

uin: in bit; -- carry in

uout: out bit -- carry out

);

end component;

signal a3, a2, a1, a0 : bit;

signal b3, b2, b1, b0 : bit;

signal c3, c2, c1, c0 : bit;

signal uin : bit;

signal uout : bit;

begin

sum: ripple_carry_adder port map (

a3 => a3, a2 => a2, a1 => a1, a0 => a0,

b3 => b3, b2 => b2, b1 => b1, b0 => b0,

c3 => c3, c2 => c2, c1 => c1, c0 => c0,

uin => uin, uout => uout

);

uin <= '0';

b3 <= '0' after 0 ns;

b2 <= '1' after 0 ns;

b1 <= '0' after 0 ns;

b0 <= '1' after 0 ns;

a0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

a1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

a2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

a3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end architecture behave;