Nächste Seite: Re: MIPS auf Xilinx Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: MIPS auf Xilinx

apt-get install gtkwaves

Gut. Dann - müssen wir entsprechend übersetzen

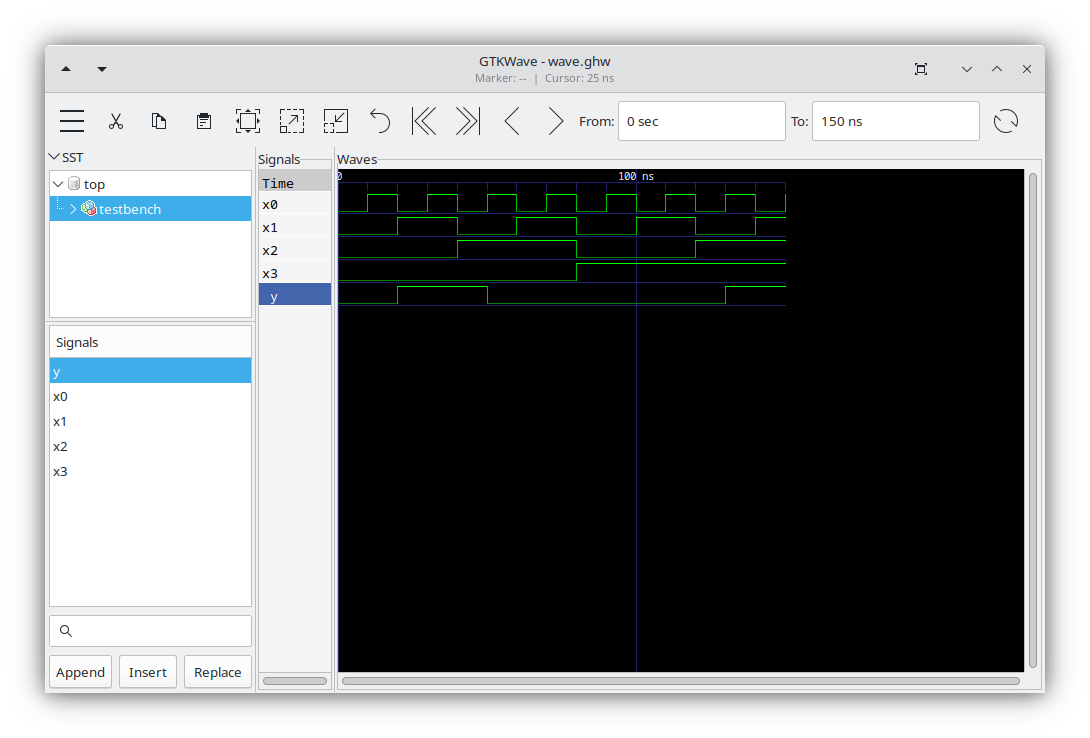

ghdl -a meinschaltnetz0027b.vhdl ghdl -r testbench --wave=wave.ghw gtkwave wave.ghw

Die die Superklasse nennen. Wir haben natürlich bei der Schaltung, ein Ding, was alles umgibt. Und das ist eine

architecture/entity/compont, die einen Namen hat. In dem Falle, testbench Ich zeige das mal

entity testbench is

end entity testbench;

architecture behave of testbench is

component meinschaltnetz0027

port

(

x3, x2, x1, x0: in bit;

y: out bit

);

end component;

signal x3, x2, x1, x0: bit;

signal y: bit;

begin

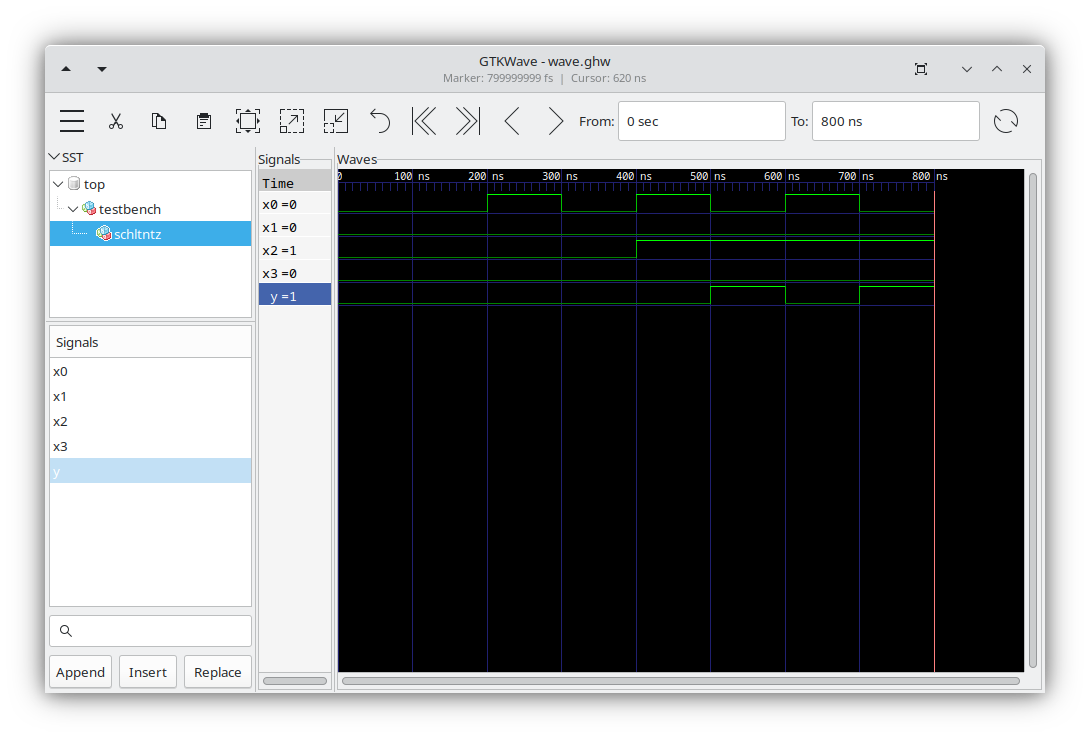

schltntz: meinschaltnetz0027 port map (y=>y, x3=>x3, x2=>x2, x1=>x1, x0=>x0);

x0 <= '0' after 100 ns, '1' after 200 ns, '0' after 300 ns, '1' after 400 ns, '0' after 500 ns, '1' after 600 ns, '0' after 700 ns, '0' after 800 ns;

x2 <= '1' after 400 ns;

end architecture behave;

Der Unterschied besteht darin, dass es die Möglichkeit mit einem 'clk' gibt. Also, das ist nicht schwer zu verstehen

Zunächst, brauchen wir erst mal

angebracht\\

\\

es geht aber auch anders und ich w"urde mal sagen, bequemer\\

\\

N"amlich mit \\

\begin{verbatim}

after

Wir könnnen eingeben,

x0 <= '0' after 100 ns, '1' after 200 ns, '0' after 300 ns, '1' after 400 ns, '0' after 500 ns, '1' after 600 ns, '0' after 700 ns, '0' after 800 ns;

Dann ändert sich der Wert von ist auf dem Bild zu sehen. \\

\\

\\

Keine Sorge, f"ur alle, die sich wundern, warum ich if's sagte. die kann ich schon unterscheiden - das ist f"ur alle, die ihren ersten Blick jemals auf VHDL Codes geworfen haben und sich denken - wow ein IF - ich sage so - sie weisen entsprechend der abgefragten eingangssignale ein m"ogliches Netz zu\\

\\

Es geht auch anders - indem sie alles als eine Schaltung hinschreiben. Das meinte ich ja nur.}

\section{ Re: MIPS auf Xilinx FPGA}

Jetzt habe ich hier noch bisher, die \begin{verbatim} jetzt.}

\section{ Re: MIPS auf Xilinx FPGA}

\begin{verbatim}

-- Ok, das sieht schon mal besser aus - und jetzt gucken wir uns die Wahrheitstafel an.

entity meinschaltnetz0027 is

port

(

y: out bit;

x3, x2, x1, x0: in bit

);

end;

architecture verhaltenknf of meinschaltnetz0027 is

begin

y <= (not x3 and not x2 and x1) or

(x3 and x2 and x1) or

(not x3 and x2 and not x1 and not x0) or

(x3 and x2 and x0);

end;

--architecture verhaltendsnf of meinschaltnetz0027 is

--begin

-- y <= (x3 or x2 or not x1) and

-- (not x3 or not x2 or not x1) and

-- (x3 or not x2 or x1 or x0) and

-- (not x3 or not x2 or not x2);

--end;

entity testbench is

end entity testbench;

architecture behave of testbench is

component meinschaltnetz0027

port

(

x3, x2, x1, x0: in bit;

y: out bit

);

end component;

signal x3, x2, x1, x0: bit;

signal y: bit;

begin

schltntz: meinschaltnetz0027 port map (y=>y, x3=>x3, x2=>x2, x1=>x1, x0=>x0);

--x0 <= '1' after 0 ns, '0' after 100 ns, '1' after 200 ns, '0' after 300 ns, '1' after 400 ns, '0' after 500 ns, '1' after 600 ns, '0' after 700 ns, '0' after 800 ns, '1' after 900 ns, '0' after 1000 ns;

--x1 <= '1' after 0 ns, '0' after 400 ns, '1' after 800 ns;

--'0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1',

--'0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1',

--'0', '0', '0', '0', '1', '1', '1', '1', '0', '0', '0', '0', '1', '1', '1', '1',

--'0', '0', '0', '0', '0', '0', '0', '0', '1', '1', '1', '1', '1', '1', '1', '1',

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 15´0 ns;

end architecture behave;