Nächste Seite: Re: Aufgaben und Übungen, Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: Aufgaben und Übungen,

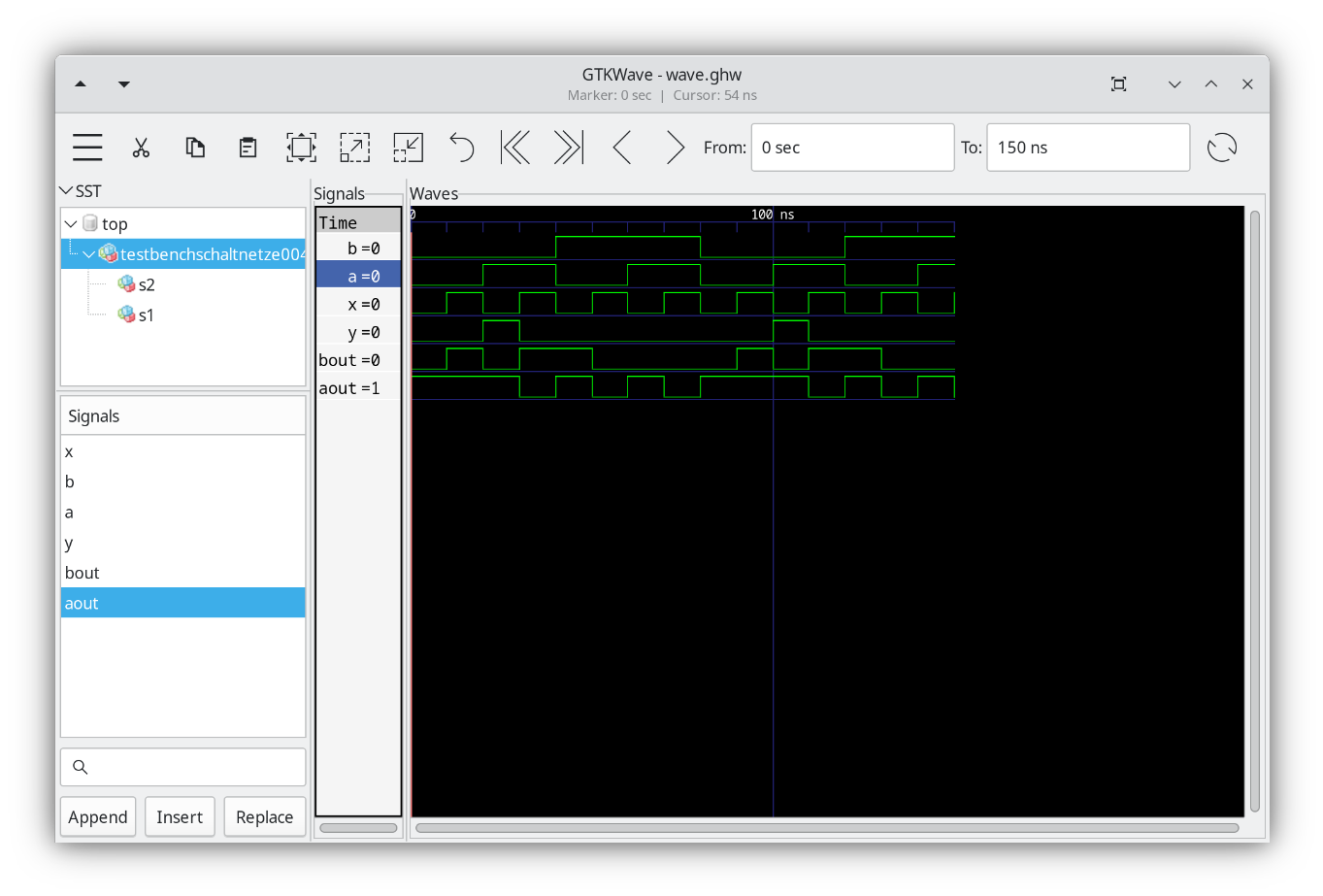

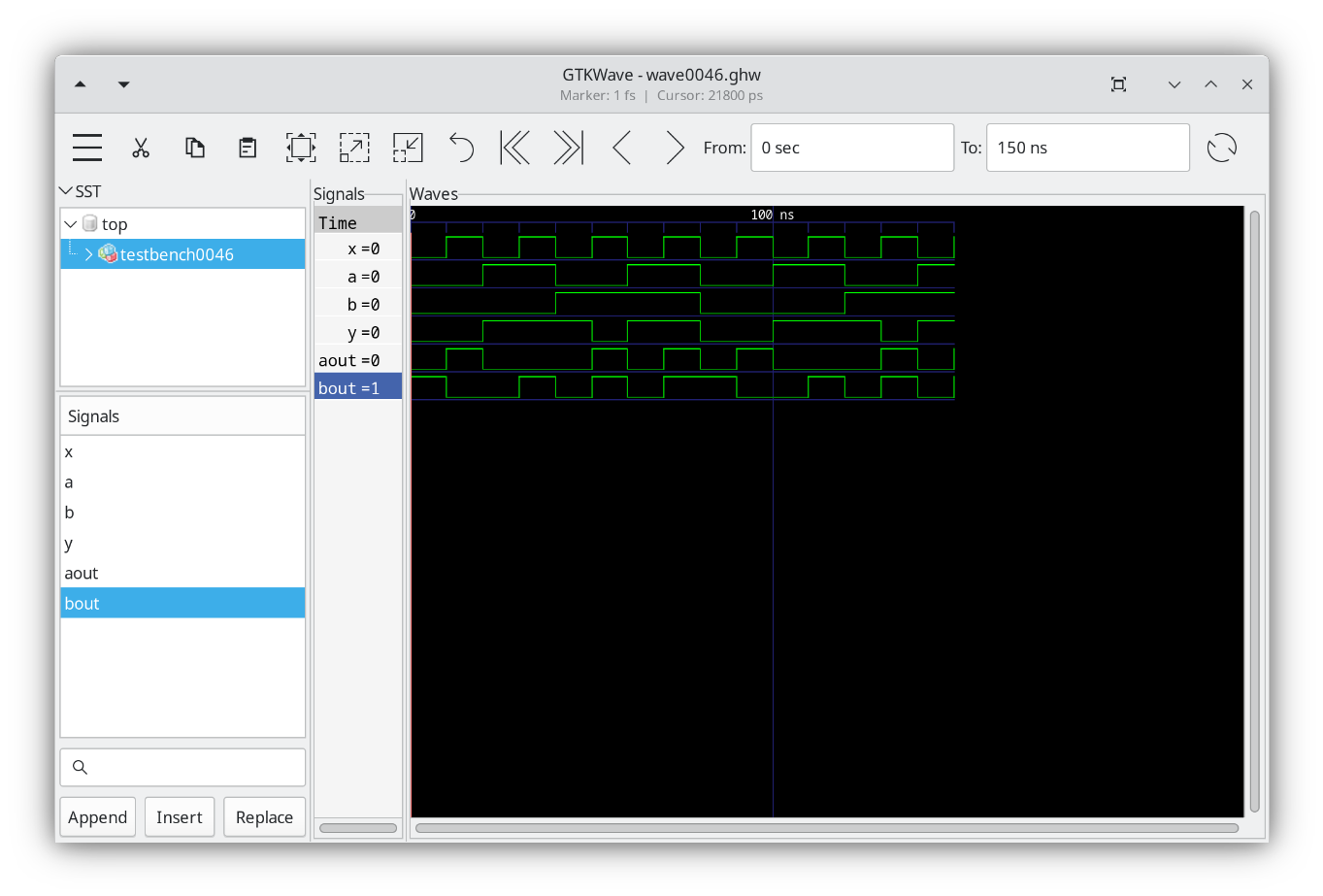

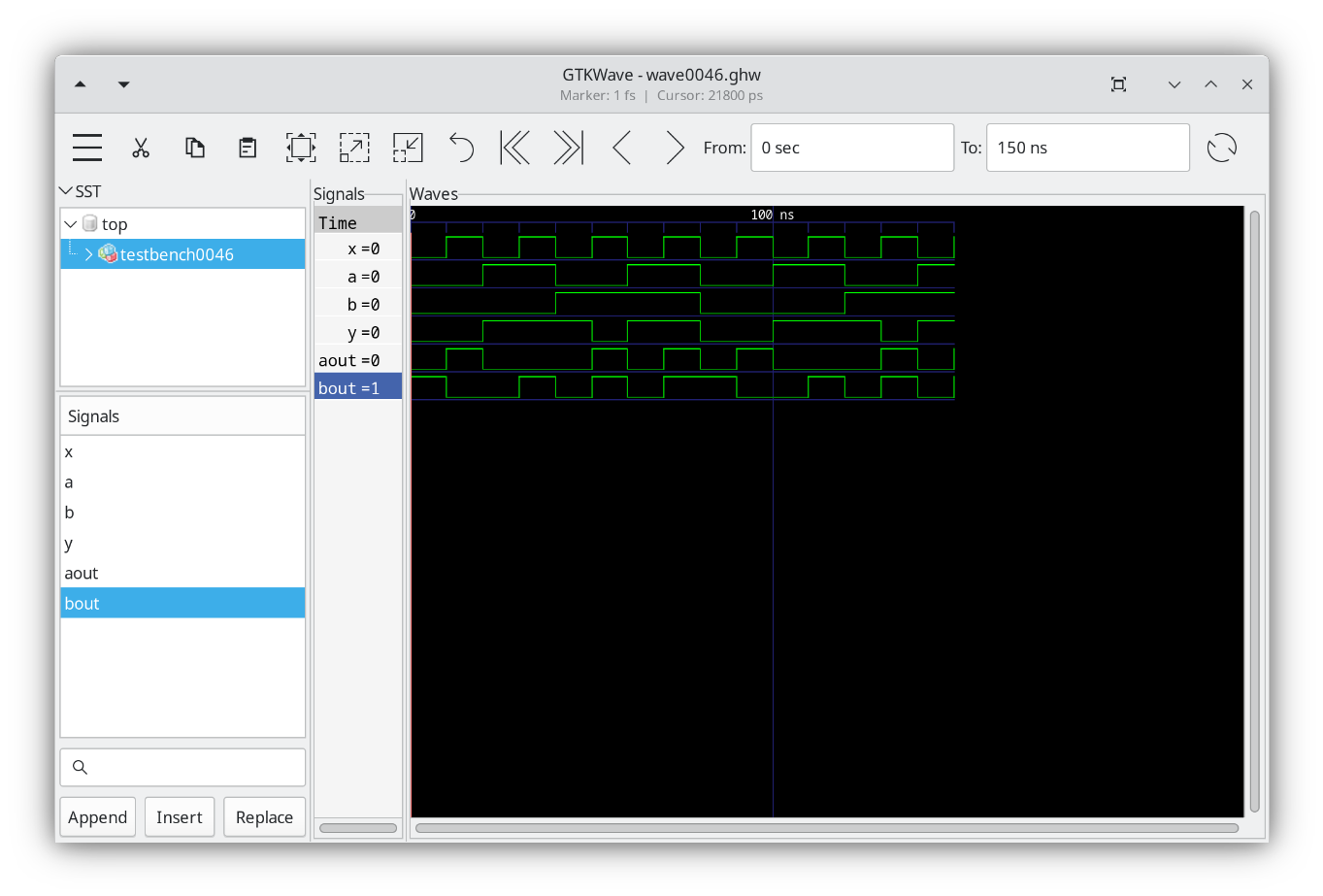

library ieee; use ieee.std_logic_1164.all; entity ausgangsschaltnetz0042 is port ( a, b, x: in std_logic; y: out std_logic ); end; architecture verhalten of ausgangsschaltnetz0042 is begin y <= (b and not a and not x); end; library ieee; use ieee.std_logic_1164.all; entity uebergangsschaltnetz0042 is port ( a, b, x: in std_logic; aout, bout: out std_logic ); end; architecture verhalten of uebergangsschaltnetz0042 is begin bout <= (not x) or (not b and a); aout <= (not a) or (b and x) or (not b and not x); end;

https://www.youtube.com/watch?v=5S3O4NBc8ko">https://www.youtube.com/watch?v=5S3O4NBc8ko</URL>\\

\\

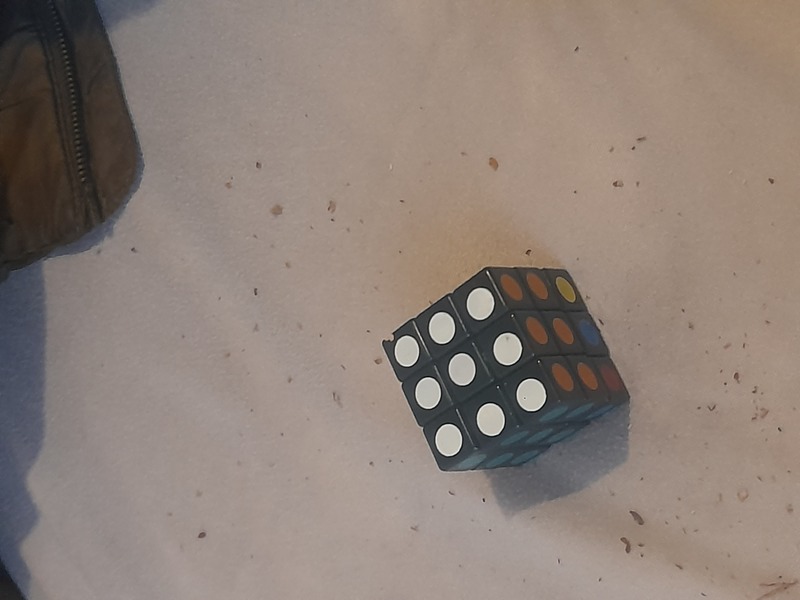

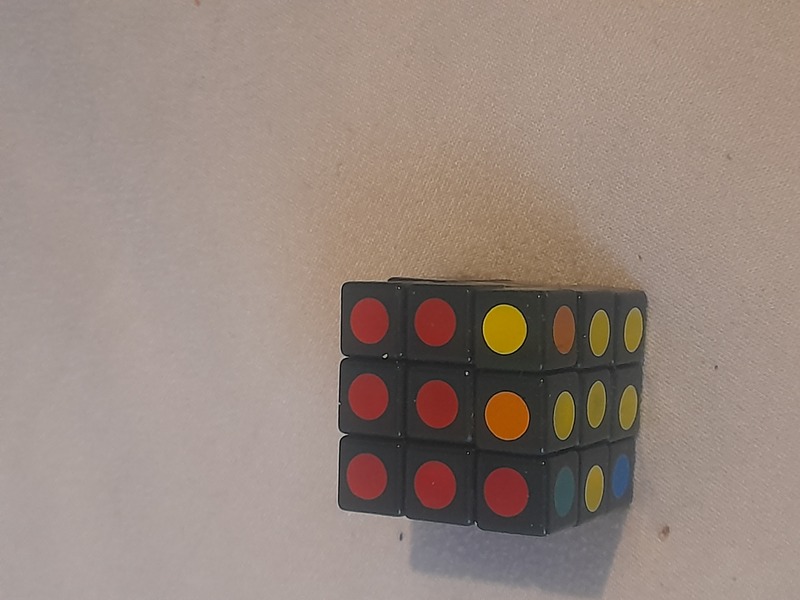

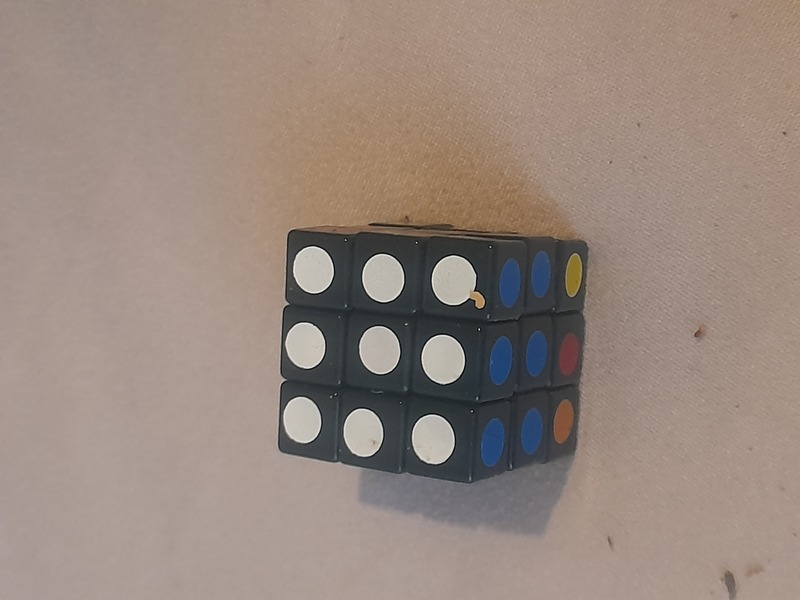

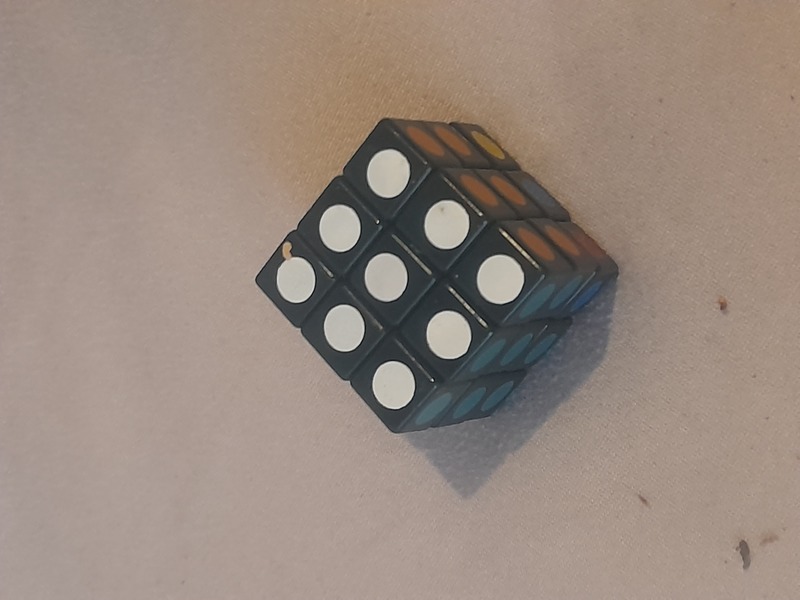

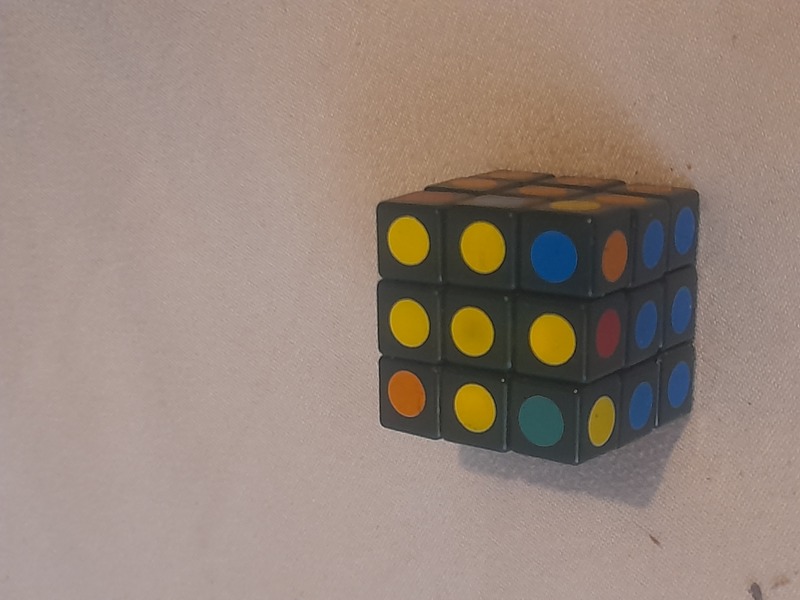

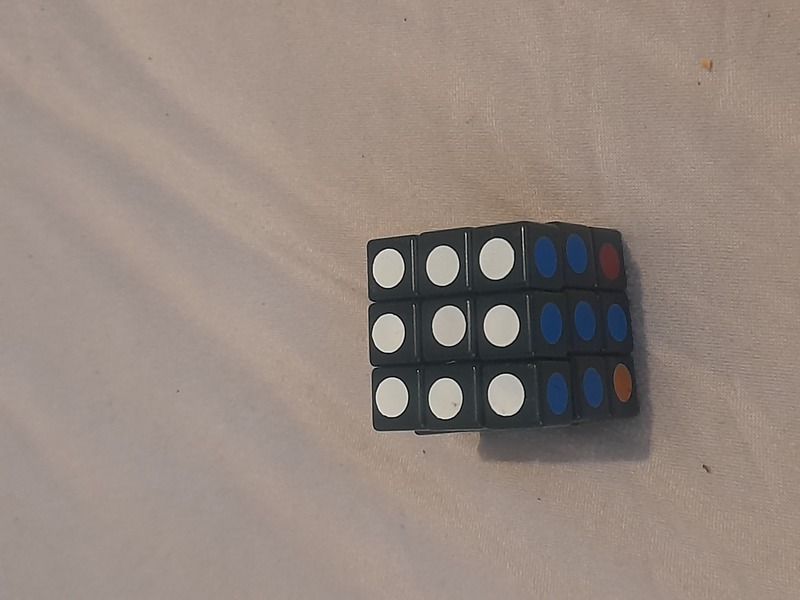

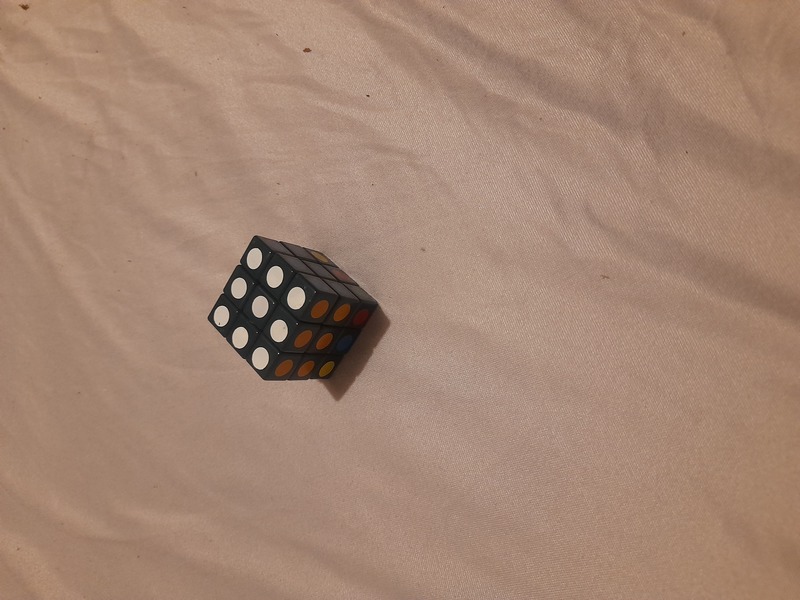

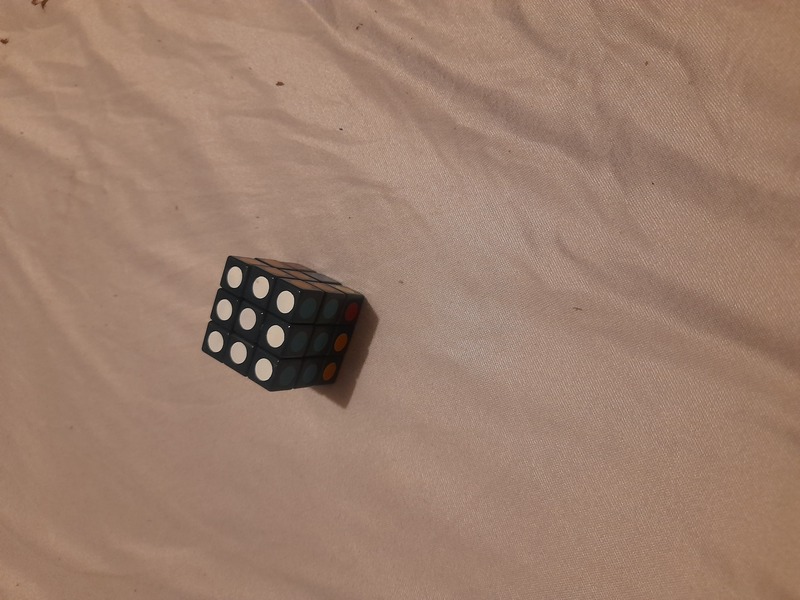

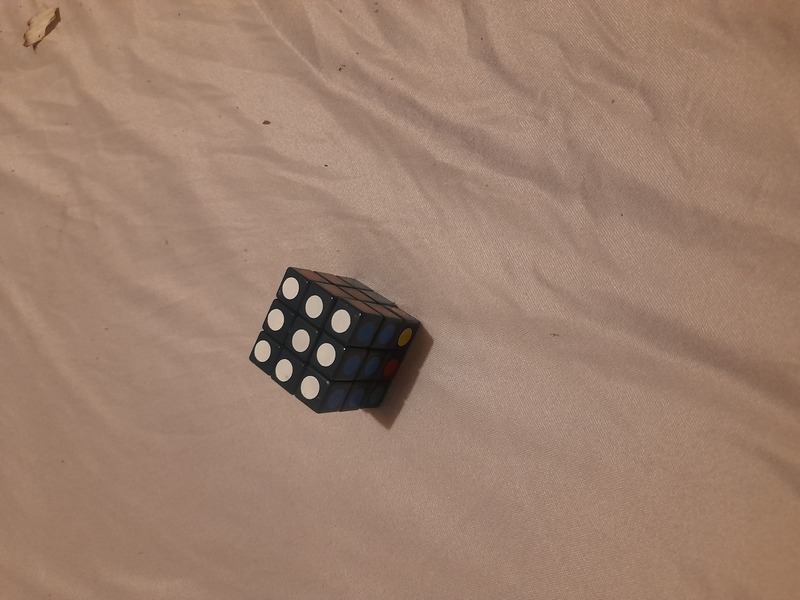

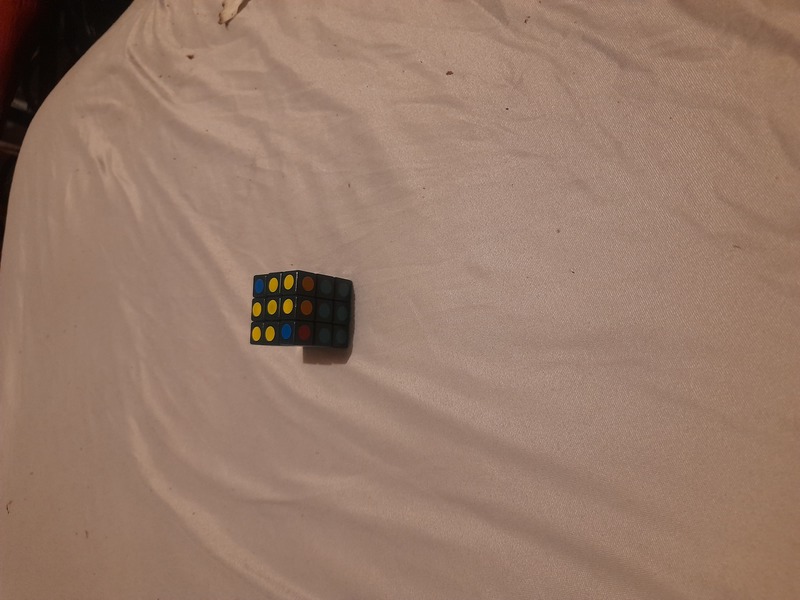

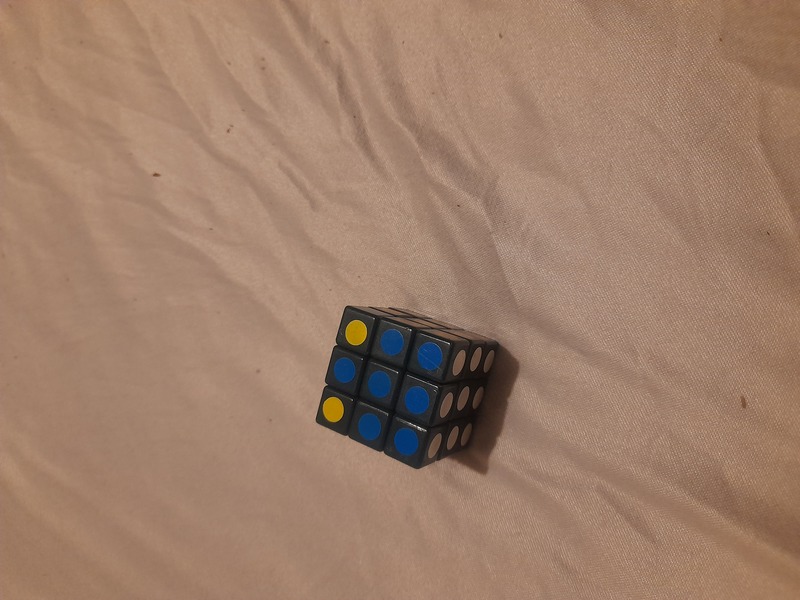

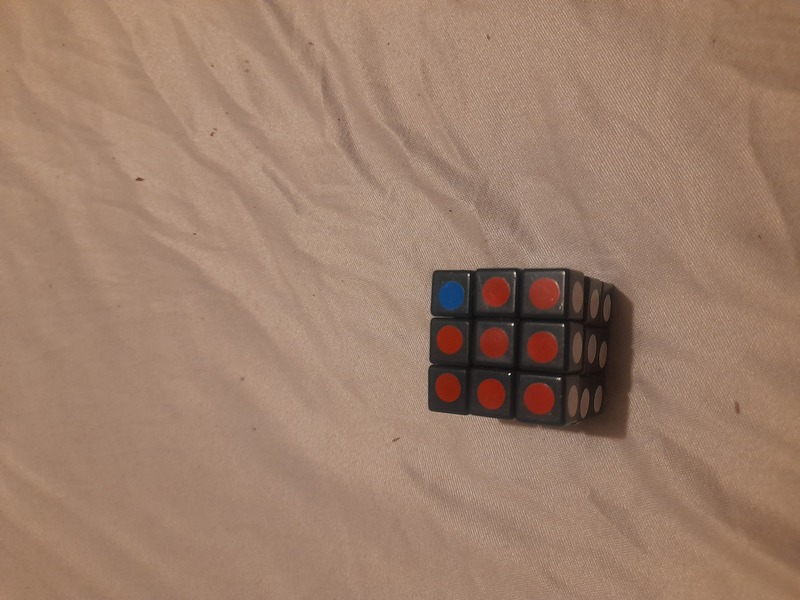

Ich empfehle ihnen dringend - diese Folge von youtube Videos zum L"osen des Rubik Cubes- damit wird es ganz simpel - ganz simpel - ich poste die Ergebnisse auf meiner Homepage.\\

\\

Nat"urlich werde ich die Abfolge Schritt f"ur Schritt auswendig lernen. Ich werde sie niederschreiben und auswendig lernen. Es nat"urlich in den aller seltensten F"allen 1:1. Trotzdem stimmen die Schritte - ich lerne sie auswendig und "ube sie Part f"ur Part

\\

Es gibt verschiedenste Parts - der erste ist das weisse Kreuz.\\

\\

Ich lerne es auswendig und "ube es \\

\\

Ich lerne so oder so weiter auch andere Sachen - ich denke, im Normalfall ist das angebracht - auch, etwas anderes zu tun, zum Beispiel weiter auswendig zu lernen, anderes. In dem Falle habe ich es mit nahe zu einem Anlauf

1894 &

\begin{verbatim}

lb, lbu

lh, lhu

lw

ld*

la*

li*

sb

sh

sw

sd*

add, addi, addiu

sub

mult, multu

div, divu

and, andi

or, ori

xor, xori

not*, abs*, neg*, rem*

Datenbewegungsbefehle

arithmetisch logische Befehle

Schiebe und Rotationbsbefehle

Gleitkommabefehle

Multimediabefehle

Programmsteuerbefehle

Systemsteuerbefehle

Synchronisationsbefehle

Dreiaddressformat

Zweiaddressformat

Einaddressformat

Nulladdressformat

Lade- und Speicherarchitektur

Register- Speicherarchitektur

Speicher- Speicherarchitektur

Akkumulatorarchitektur

Stack- und Kellerarchitektur

Stackarchitektur: 8087, Intel, ATM 862 Atmel

Little-Endian, Big-Endian

Einzelbit

Ganzzahl

Gleitkomma

Multimedia

signed

unsigned

packed

unpacked

bcd

ascii

byte

halbwort

wort

doppelwort

ieee-754-std

f = (-1)\^s * 1.m * 2\^(e-b)

32: einfach

64: doppelt

80: erweitert

Absolute Addressierung

Unmittelbare Addressierung

Registeraddressierung

Direkte Addressierung

Indirekte Addressierung

Indirekte Addressierung mit Autoinkrement/Dekrement

Indirekte Addressierung mit Verschiebung

Indizierte Addressierung

Indizierte Addressierung mit Verschiebung

Steuereinheit

1.) Befehlsdekodierer

2.) Funktionsdekodierer

MemToReg

MemWrite

Branch

ALU-Src

ALU-Op

RegDst

Regwrite

Befehlsdekodierer

Funktionsdekodierer

ALU

Registersatz

Datenspeicher

Befehlsspeicher

Befehlsz"ahler

4 x MUX

1 x AND

2 x Addierer

1 x 2 Bit Shifter

Befehlsdekodierer

- MemTorReg

- MemWrite

- Branch

- ALU-Src

- RegDst

- RegWrite

Funktionsdekodierer

- Func

- ALU-Op

- ALU-Operation

ALU

- Ergebnis

- Null

AND:

- PCSrc

Registersatz

- Lese-Daten-1

- Lese-Daten-2

- Schreibedaten

- Lese-Register-1

- Lese-Register-2

- Schreiberegister

- WE

Datenspeicher

- Addresse

- Lesedaten

- Schreibedaten

- WE

Befehlsz"ahler

- PC (t)

- PC (t+1)

Befehlsspeicher

- Leseaddresse

- Lesedaten

Func ALU-Op ALU-Operation

00 x 010 - add

x1 x 110 - sub

1x 100 000 - add 010 - add

OpCode RegDst RegWrite Branch ALU-Src MemToReg MemWrite ALU-Op

r-typ 000 000 1 1 0 0 0 0 10

Verzweigungsbefehle

1.) Bedingt

2.) Unbedingt

Absolut: Branch

Befehlsz"ahlerrelativ: Jump

Befehlsz"ahlerindirekte: Jump Register

eq - equal

ne - not equal

gt - greater than

ge - greater than equal

lt - less than

le - less than equakl

JAL: Jump And Link: Speichern zuns"atzlich die Addresse die dem Sprungbefehl folgt

PC_neu = PC_alt + (i << 2)

PC_neu = PC_alt \& 0xf000 0000 | (i << 2)

j, b*, jr

jal

jalr

beq, bne

beqz*, bnez*

blt*, ble*

bltz, blez

bgt*, bge*

bgtz, bgez

Mehrzyklus Zustandselemente

- Befehlsz"ahler

- Befehlsspeicher

- Registersatz

- Datenspeicher

Pipeline-Prinzip

Pipleline-Stufe

Pipeline-Register

1.) Datenkonflikte

2.) Steuerflusskonflikte

3.) Struktur und Ressourcenkonflikte

1.) Befehl holen

2.) Befehl dekodieren

3.) Operanden der ALU bereitstellen

4.) Operation in der ALU ausf"uhren

5.) Operanden in Architekturregister zur"uckschreiben

1.) IF - Instruction Fetch

2.) ID - Instruction Decode / Register Fetch

3.) EX - Execute Address Calculation

4.) MEM - Memory Access

5.) WB - Write Back

1.) Statisches Schedeling: VLIW - Prozessor: In Order Issue In Order Completion

2.) Dynamisches Scheduling: OOE-Prozessor: Out Of Order Issue Out Of Order Completion

1.) Statisches Sprungvorhersage

1.1.) Predict Always Not Taken

1.2.) Predcit Always Taken

1.3.) Predict Backward Taken/Forward Not Taken

2.) Dynamisch: 1 oder 2 Bit Pr"adiktor

2.1.) Taken / Not Taken

2.2.) Strongy/Weakly Taken/Not Taken

Schaltnetze

Schaltwerke

Komplexe Schaltwerke

Aufbau und Funktionsweise eines Computers

Schaltnetze

Boolesche Algebra

Definition der Booleschen Algebra

Schaltalgebra ein Modell der Booleschen Algebra

Schaltfunktion

Definition

Darstellung

Minimierung

Analyse von Schaltnetzen

Synthese von Schaltnetzen

Kodierer

Schaltnetzentwurf f"ur 8421-BCD zu Siebensegment Umsetzung

Schaltnetzentwurf f"ur den Addresscodierer

Addierglieder

Halbaddierer

Volladdierer

Paralleladdierer

Komperatoren

Multiplexer

ALU

Zahlendarstellung und Zweierkomplement

Addierer/Subtrahierer

Schaltnetze mit Programmierbaren Bausteien

ROM

PROM, EPROM

PAL

PLA

Laufzeiteffekte in Schaltnetzen

Schaltwerke

Modelle f"ur Schaltwerke

Implementierung von Schaltwerken

Synthese von Schaltwerken

Analyse von Schaltwerken

Operationswerk und Mikroprozessor

Speicherglieder

Transformation Mealy und Moore Automat

Schaltwerke mit Bin"arkodierten Zustand

Komplexe Schaltwerke

Aufbau Komplexer Schaltwerke

Entwurf Komplexer Schaltwerke

RTL-Notation

ASM-Diagramme

Zustandsboxen

Entscheidungsboxen

Bedingte Ausgangsboxen

ASM-Block

...

Beispiel 1en Z"ahler

L"osung mit Komplexen Moore-Schaltwerk

L"osung mit Komplexen Mealy Schaltwerk

Aufbau und Funktionsweise des Operationswerks

Mealy-Steuerwerk als Konventionelles Schaltwerk

Mealy-Steuerwerk mit Hotone-Kodierung

Moore-Steuerwerk als konventionelles Schaltwerk

Moore-Steuerwerk mit Hot-One-Kodierung

Mikroprogrammierte Steuerwerke

Aufbau und Funktionswese des Computers

Elemente beim Computer

Rechenwerk

Leitwerk

Speicher

Ein und Ausgaben

Boolesche Algebra, Schaltfunktion

Boolesche Algebra, Schaltfunktionen

Boolesche Algebra, Schaltfunktionen

Boolesche Algebra, Schaltfunktionen

Boolesche Algebra, Schaltfunktionen

Boolesche Algebra, Schaltfunktionen

Boolesche Algebra, Schalftunktionen

Definition der Boolesche Algebra

Schaltalgebra ein Modell der Booelschen Algebra

Definition der Booleschen Algebra

Schaltalgebra ein Modell der Booleschen Algebra

Definition der Booleschen Algebra

Schaltalgebra ein Modell der Booleschan Algebra

Definition der Booleschen Algebra

Schaltalgebra ein Modell der Booleschen Albgebra

Definition, Darstellung, Minimierung

Definition, Darstellung, Minimierung

Definition, Darstellung, Minimierung

Definition, Darstellung, Minimierung

Schaltnetzentwurf f"ur die 8421-BCD-zu Sieben Segment Umsetzung

Schaltnetzentwurf f"ur den Addresskodierer

Schaltnetzentwurf f"ur die 8421-BCD-zu Sieben Segment Umsetzung

Schaltnetentwurf d"u den Addresskodierer

Modelle f"ur Schaltwerke

Implementierung f"ur Schaltwerke

Modelle f"ur Schaltwerke

Implementierung f"ur Schaltwerke

Modelle, Implementierun

Modelle, Implementierung

Modelle, Implementierung

Modelle, Implementierung

Modelle, Implementierung

Modelle, Implementierung

Modelle f"ur Schaltwerke

Implementierung f"ur Schaltwerke

Modelle f"ur Schaltwerke

Implementierung f"ur Schaltwerke

Modelle f"ur Schaltwerke

Implementierung f"ur Schaltwerke

Modelle f"ur Schaltwerke

Implementierung f"ur Schaltwerke

Komplexes Schaltwerke und Mikroprozessor

Speicherglieder

Komplexe Schaltwerk und Mikroprozessor

Speicherglieder

Komplexes Schaltkwer und Mikroprozessor

Speicherglieder

Komplexes Schaltwerk und Mikroprozessor

Speicherglieder

Transformation Mealy und Moore Automat

Schatwerke mit Bin"arkodierten Zustand

Transformation Mealy und Moore Automat

Schaltwerke mit Bin"arkodierten Zust"and

Transformation Mealy und Moore Automat

Schaltwerke mit Bin"arcodierten Zustand

Entwurf von Schaltwerken

Aufbau Komplexer Schaltwerke

Entwurf von Schaltwerken

Aufbau Komplexer Schaltwerke

Entwurf von Schaltwerken

Aufbau Komplexer Schaltwerke

Entwurf von Schaltwerken

Aufbau Komplexer Schaltwerke

RTL-Notation, ASM-Diagramme

RTL-Notation, ASM-Diagramme

RTL-Notation, ASM-Diagramme

RTL-Notation, ASM-Diagramme

Konstruktionsregeln f"ur Operationswerke

Entwurf des Steuerwerks

Konstruktionsregeln f"ur Operationswerke

Entwurf des Steuerwerks

Konstructionsregeln f"ur Operationswerke

Entwurf des Steuerwerks

Konstructionsregeln f"ur Operationswerke

Entwurf des Steuerswerk

L"osung, L"osung, L"osung, L"osung

L"osung mit, L"osung mit, L"osung mit L"osung mit

L"osung mit Komplexen Moore-Schaltwerk

L"osung mit Komplkexen Mealy Schaltwerke

L"osung mit Komplexen Moore-Schaltwerk

L"osung mit Komplexen Meakly Schaltwerke

L"osung mit Komplexen Moore-Schaltwerk

L"osung mit Komplexen Mealy Schaltwerk

Moore-Steuerwerk

Mealy Steuerwerk

Moore Steuerwerk

Mealy Steuewrk

Moore Steuerwerk

Mealy Steuerwerk

Moore Steuerwerk mit Hot-One Kodierung

Moore als als Konventionelles Schaltwerk

Hot One Konventionell komplex

Hot One Konventionell komplex

Hot One Konventionell Komplex

Hot One Konventionell Komplexe

Moore Steuerwerk als konventionelles schaltwerk

Moore Steuerwerk mit Hot One Codierung

Moore Steuwerk als konventionelels Schaltwerk

Moore Steuwerk mit Hot One Codierung

HotOne, Mikprogroprommierung, Komplex, Konvetionell

Konventionell, Komplex HotOne Mikorpogrammiert

Erweiterung komplexer Schaltwerke

Erweiterung komplexer Schaltwerke

Erweiterung komplexer Schaltwerke

Erweiterung komplexer Schaltwerke

Erweiterung komplexer Schaltwerke

Erweiterung komplexer Schaltwerke

Aufbau und Funktionsweise eines Computers

Erweiterung komplexer Schaltwerke

Aufbau und Funktionsweise eines Computers

Erweiterung komplexer Schaltwerke

Aufbau und Funktionsweise eines computers

Erweiterung komplexer Schaltwerke

Komponenten eines Computers

Kompoentnen eines Computers

Komponenten eines Computers

Komponenten eines Computers

Komponenten eines Computers

Erweiterung komplexer Schaltwerke

Komponenten eines Computers

erweiterung komplexer Schaltwerke

Komponenten eines Computers

Erweiterung komplexer Schalwerke

Komponennten eines Computers

erweiterung, Komponente, Erweiterung, Komponente, Erweiterung ,Kompjnente

Interene und Externe Busse

Interne und Externe Busse

Interne und Externe Buss

UInterne und Externe Busse

Interne und Externe Busse

Interne und Externe Busse

Prozessorregsiter

Prozessorregister

Prozessorregister

Prozessorregister

Interne und Externe Busse

Prozessorregister

Interne und Externe Busse

Prozessoregister

Interne und Externe Busse

Prozessoreguister

Erweiterung komplexer Schaltwerke

Komponenten eines Computers

Interne und Extrene Busse

Prozessorregister

erweiterung komplexer Schaltwerke

Komponenten eines Computers

Interne und Externe Busse

Prozessoregsiter

Erweiterung komplexer Schaltwerke

Erweiterung komplexer Schaltwerke

Erweiterung komplexer Schaltwerke

Rechenwerk

Leitwerk

Rechenwerk

Leitwerk

Rechenwerk

Leitwerke

Aufbau und Funktionsweise eines Compteters

Erweiterung komplexer Schaltwerke

Komponenten eines Computers

Prozessoregister

Interne und Externe Busse

Rechenwerk

Leitwerk

Aufbau und Funktionsweise eines computers

Erweiterung komplexer Schaltwerke

Komponetnen eines Computers

Prozessoregsiter

Interne und Externe Busse

Rechenwerk

Leitwerke

Schaltnetze

Schaltwerke

Komplexe Schaltwerke

Aufbau und Funktionsweise eines Computers

Schaltnetze

Boolesche Algebra

Definition der Booleschen Algebra

Schaltalgebra ein Modell der Booleschen Algebra

Schaltfunktion

Definition

Darstellung

Minimierung

Analyse von Schaltnetzen

Synthese von Schaltnetzen

Kodierer

Schaltnetzentwurf f"ur den 8421-BCD-zu Siebensegment Umsetzung

Schaltnetzentwurf f"ur den Addresskodierer

Addierglieder

Halbaddierer

Volladdierer

Paralleladdierer

Komperatoren

Multiplexer

ALU

Zahlendarstellung und Zweierkomplement

Addierer/Subtrahierer

Schaltnetze Programmierbare Bausteinen

Schaltwerke

Modelle f"ur Schaltwerke

Implementierung f"ur Schaltwerke

Synthese von Schaltwerken

Analyse von Schaltwerke

Konstruktionsregeln f"ur Operationswerke

Speicherglieder

Transformation Mealy und Moore Automat

Bin"arcodierte Schaltwerke

Komplexe Schaltwerke

Aufbau komplexer Schaltwerke

Entwurf komplexer Schaltwerke

RTL-Notation

ASM-Diagramme

Zustandsboxen

Entscheidungsboxen

Bedingte Ausgangsboxen

ASM-Block

Konstruktionsregeln f"ur Operationswerke

...

Beispiel 1en Z"ahler

L"osung mit komplexen Moore Schaltwerk

L"osung mit komplexen Mealy Schaltwerk

Operationswerk

Mealay Steuerwerk als konventionelles Schaltwerk

Mealy Steuerwerk mit Hot One Kodierung

Moore Steuwerk als konventionelles Schaltwer

Moore Steuerwerk mit HotOne Kodierung

Mikroprogrammierte Steuerwerk

Aufbau und Funktionsweise eines Computers

Erweiteurng komplexer Schaltwerke

Komponenten eines Computers

Rechenwerk

Leitwerk

Speicher

Ein und Ausgaben

Interne und Externe Busse

Prozessorregister

Rechenwerk

Leitwerk

Unterprogramme, Stckpointer, Unterbrechungen, Interrupts

DIN44300

DIN4430/93

DIN4430/87

DIN4430/93: Schaltnetz

DIN4430/87: Schaltfunktion

Gesetze

- Distributivgesetz

- Assoziativgesetz

- Kommutativgesetz

- Absorbtionsgesetz

- Dualit"atsprinzip

- Neutrale Elemnte

- Inverse Elemente

Verkn"upfung

- NAND, NOR

- Disjunktion, Konjunktion

- Antivalenz, "Aquivalenz

- Null, Eins

- Invers

- Komplement

- Inhibition, Transfer

Wahrheitstafel

Schaltplan

Schaltzeichen

Funktionsgleichung

KV-Diagramm

Bin"ares Entscheidungsdiagramm

DIN40700

Kodierer Blat 43 oder so

Kodierer: Ordnen einem Zeichensatz ein Elemente eines anderen Zeichensatzes zu

Schaltfunktion: Vektorfunktion

f:{0,1}\^n -> {0,1}\^m

Eingangsvektor

Schaltnetz

Ausgangsvektor

Eingangsvariablen: x1, x2, ..., xn

Volladdierer Funktion

S = A XOR B XOR C

U = (A AND B) AND (A OR B) AND C

DIN40700: Das sind die einzelnen Schaltelemente

DIN44300: Das sind die Schaltfunktion, Schaltnzeichen und so weiter

"U = (A AND B) OR (A OR B) AND C

"U = (A AND B) OR (A OR B) AND C

"U = (A AND B) OR (A OR B) AND C

"U = (A AND B) OR (A OR B) AND C

AND, OR, OR, AND

AND OR OR AND

AND OR OR AND

AND OR OR AND

"U = (A AND B) OR (A OR B) AND C

"U = (A AND B) OR (A OR B) AND C

"U = (A AND B) OR (A OR B) AND C

"U = (A AND B) OR (A OR B) AND C

"U = (A AND B) OR (A OR B) AND C

DIN44300

DIN44300

DIN44300

DIN44300

Schaltnetze: Elektronische Schaltungen, die Spannungen als logische Variablen 0 und 1 interpretieren

Schaltnetze: Elektronische Schaltungen, die Spannungen als logische Variablen 0 und 1 interpretieren

Schaltnetze: Elektronische Schaltugnen, die Spannungen als logische Variablen 0 und 1 interpretieren

Boolesche Algebra, Schaltalgebra

Boolesche Algebra, Schaltalgebra

Boolesche Algebra, Schaltalgebra

Boolesche Algebra, Schaltalgebra

Verkn"upfungsglieder, Schaltfunktion, Vektorfunktion

Verkn"upfungsglieder, Schatlfunktion, Vektorfunktio bn

Verkn"upfungsglieder, Schaltfunktion, vektorfunktion

Verkn"upfungsglieder, Schaltfunktion, Vektorrfunktion

F:{0,1}\^n -> {0,1}\^m

F:{0,1}\^n -> {0,1}\^m

F:{0,1}\^n -> {0,1}\^m

F:{0,1}\^n -> {0,1}\^m

Schaltnetz: DIN44300/93

Schaltnetz: DIN44300/93

Schaltnetz: DIN44300/93

Schaltnetz: DIN44300/93

Schaltnetz: DIN44300/93

Schaltplan

Funktionstabelle

Funktionsgleichung

Schaltalgebra

schaltplatn

Funktionstabelle

Funktionslgeichung

Schaltalgebra

Schaltplatn

Funktionstabelle

funktionsgleichung

Schaltalgebra

Schaltplan

Funktionstabelle

Funktionsgleichung

Funktionstaeblle

Funktiosnsgleichung

Kommutativ, Assoziativ, Distributiv, Absorbtion

Kommutativ, Assoziativ,k Distributiv, Absorption

Kommutativ, Assoziativ, Distributiv, Absorption

Kommutativ, Assoziativ, Distrbutiv, Absorbtion

Kommutativ, Assoziativ, Distributiv, Absorbtion

Kommutativ, Assoziativ, Distributiv Absorbition

Kommutativ, Assoziativ, Distributiv Absorption

Neutrales Element, komplement"ares Element

eutrales Element, Komplemenet"ares Elemente

Neutrales Element, Komplement"ares Element

Neutrales Element Komplement"ares Element

Dualit"atsprinzip De Morgansche Regeln

Dualit"atsprinzip De Morgansche Regeln

Kommutativ, Assoziativ, Distributiv, Absorobtiobn, Neuetrales Elemetn, Komplement"ares SElement, Dualtit"atsprunzip De Morgansche Regeln

DIN44300/87: Schaltfunktion

DIN44300/87: Schaltfunktion

DIN44300/87: Schaltfuntkion

DIN44300/87: Schaltfunnktion

Schaltnetz, Schalftunktion

Schaltnetz, Schaltfunktion

Schaltnetz, Schalffunktion

Schaltetz: DIN44300/93

Schalftunktion DIN44300/87

Disjunktion, Konjunktion

Disjunktion, Konjunktion

Disjunktion, Konjunktion

Disjunktion, Konjunktion

Disjunktion, Konjunktion

Inhibition, Transfer

Inhibition, Transfer

Inhibition, Transfer

Inhibition, Transfer

Inhibtion, Transfer

Inhibition, Transfer

NOR, NAND

NOR, NAND

NOR, NAND

NOR NAND

"Aquivalenz

Antivalenz

"Aquivalenz, Antivalenz

"Aquivalenz Antivalenz

Null, Eins

Null, Eins

Null, Eins

Null, Eins

Null, eins

Implikation

Implikation

Implikation

Transfer, Inhibition, Implikation

Transfer, Inhibition, Implikation

Grundverk"upfung: DIN40700

Grundverk"unpfung: DIN40700

Grundverk"unpfung: DIN40700

"U = (A AND B) OR (A OR B) AND C

AND OR OR AND

AND OR OR AND

AND OR OR AND

AND OR OR AND

"U = (A AND B) OR (A OR B) AND C

"U = (A AND B) OR (A OR B) AND C

"U = (A AND B) OR (A OR B) AND C

PLHS18P8

PLHS18P8

PLHS18P8

PLHS18P8

PAL16L8

PAL16L8

PAL16L8

18 16

18 16

18 16

PLHS

PLHS

PLHS

P L

P L

P L

8 8 88 88 8

GAL 20 V 10

PLV

PLV

PLV

PLV

PLV

20 18 16

20 18 16

20 18 16

20 18 16

8 10

8 10

8 10

PAL 16L8

GAL 20V10

PLHS 18P8

5 Bit 32 Bit 5 Bit 32 Bit 5 Bit 32 Bit 5 Bit 32 Bit 5 Bit 32 Bit 5 Bit 32 Bit r-typ Befehle r-typ Befehle r-typ Befehle r-typ Befehle r-typ Befehle r-typ Befehle r-Typ Befehle r-typ befehle: add, sub, and, or, slt r-typ Befehle: add, sub, and, or, slt r-typ Befehle: add, sub, and, or, slt r-typ Befehle: add, sub, and, or, slt r-typ Befehle: add, sub, and, or, slt r-typ Befehle: add, sub, and, or, slt rt-Feld rs-Feld rt-Feld, rs-Feld rt-Feld, rs-Feld rt-Feld, rs-Feld rt-Feld, rs-Feld rt-Feld, rs-Feld ALU-Op, 00, x1, 1x ALU-Op, 00, x1, 1x ALU-Op, 00, x1, 1x ALU-Op: 00 addition ALU-Op: x1 subtraction ALU-Op: 1x Func Feld ALU-Op: 00 addition x1: subtratkion 1x func feld 00 addition x1 subtratkoin 1x func feld 00 addition x1 subtration 1x func feld Func 4 0 4 2 4 4 func 4 0 4 2 4 4 Func 4 0 4 2 4 4 Func 4 0 4 2 4 4 Func 4 0 4 2 4 4 Func 4 0 4 2 4 4 4 5 5 2 Func 4 0 4 2 4 4 4 5 5 2 Func 4 0 4 2 4 4 4 5 5 2 Func 4 0 4 2 4 4 4 5 5 2 add sub and or slt add sub and or slt add sub and or slt add sub and so slt 4 0 4 2 4 4 4 5 5 2 4 0 4 2 4 4 4 5 5 2

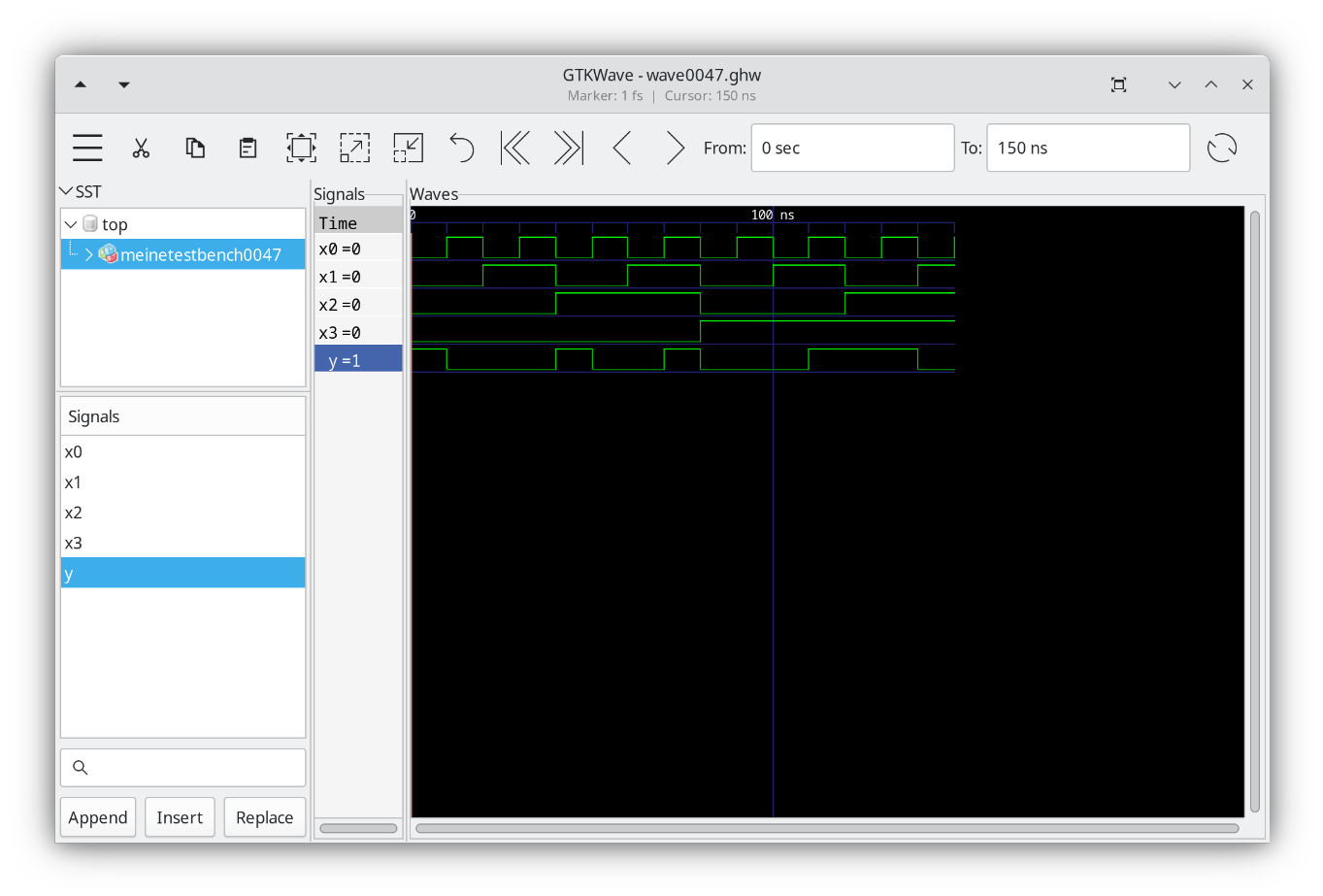

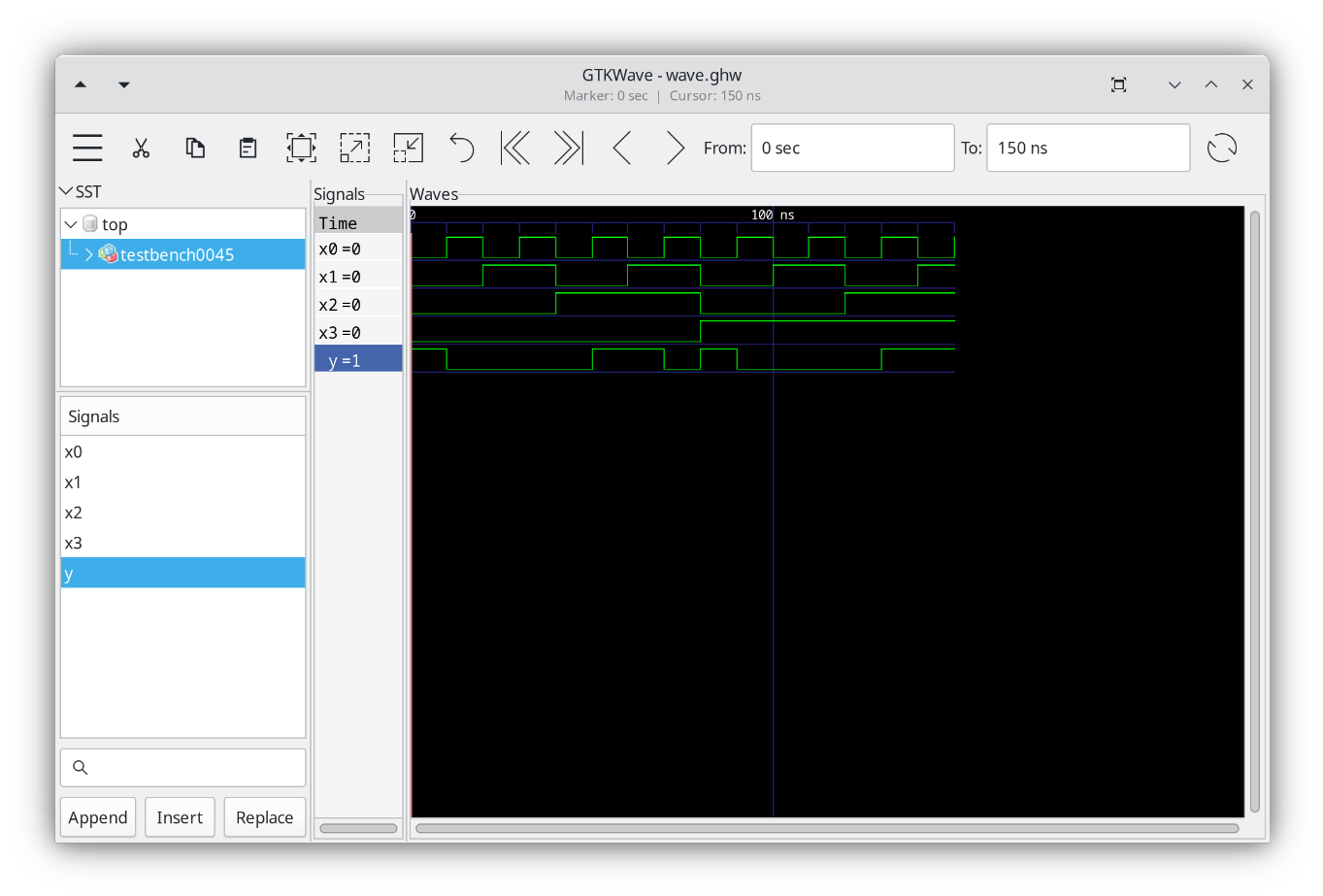

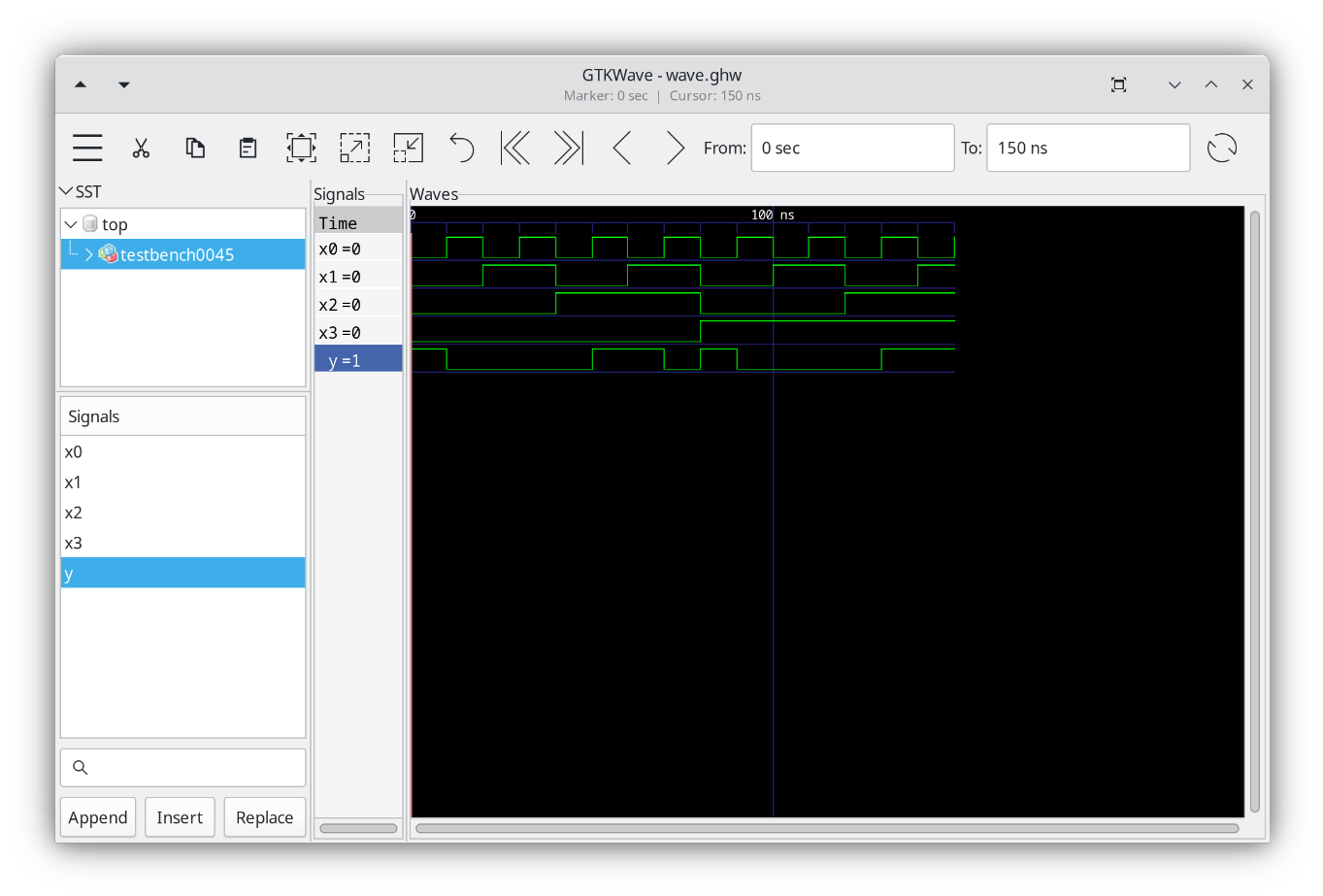

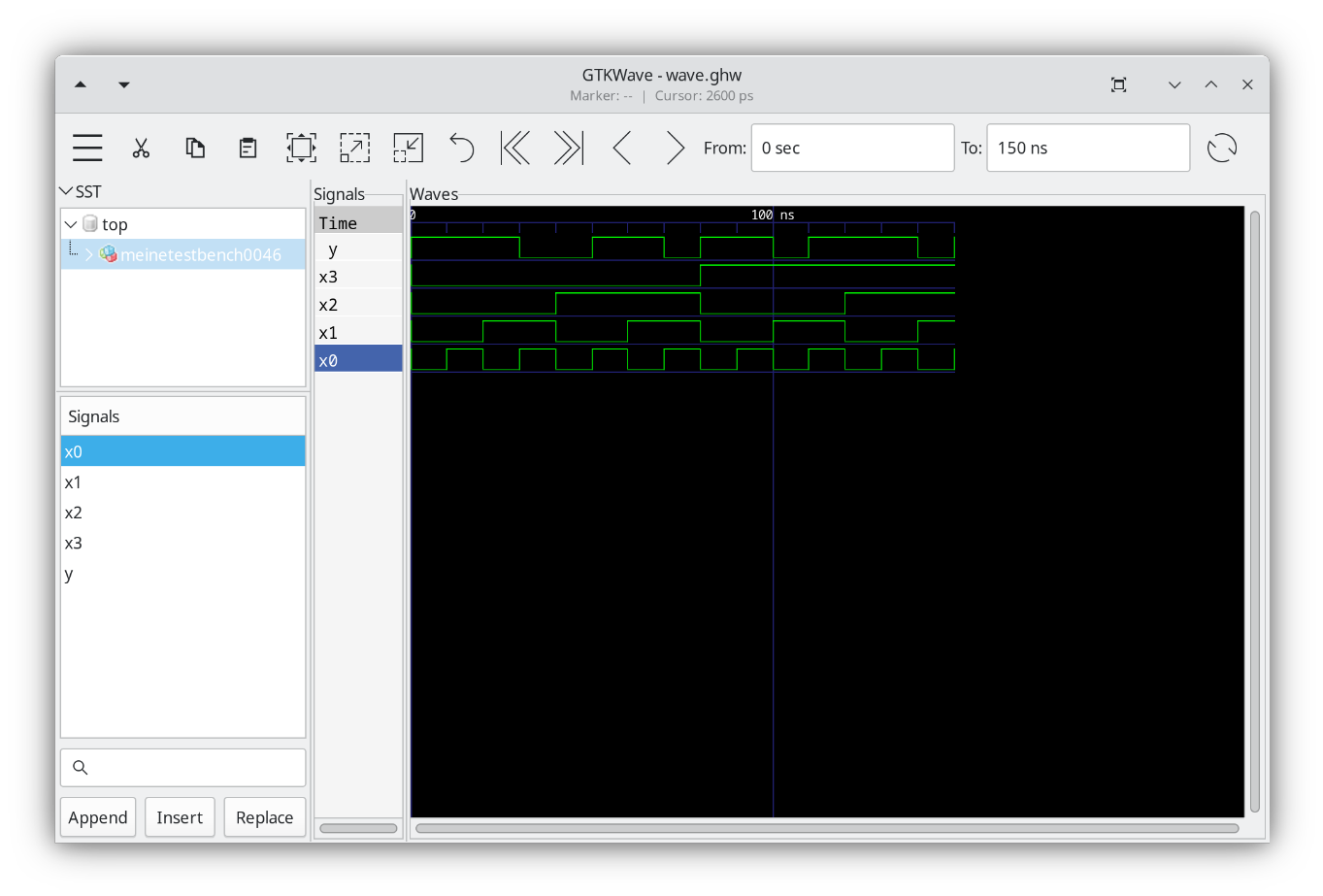

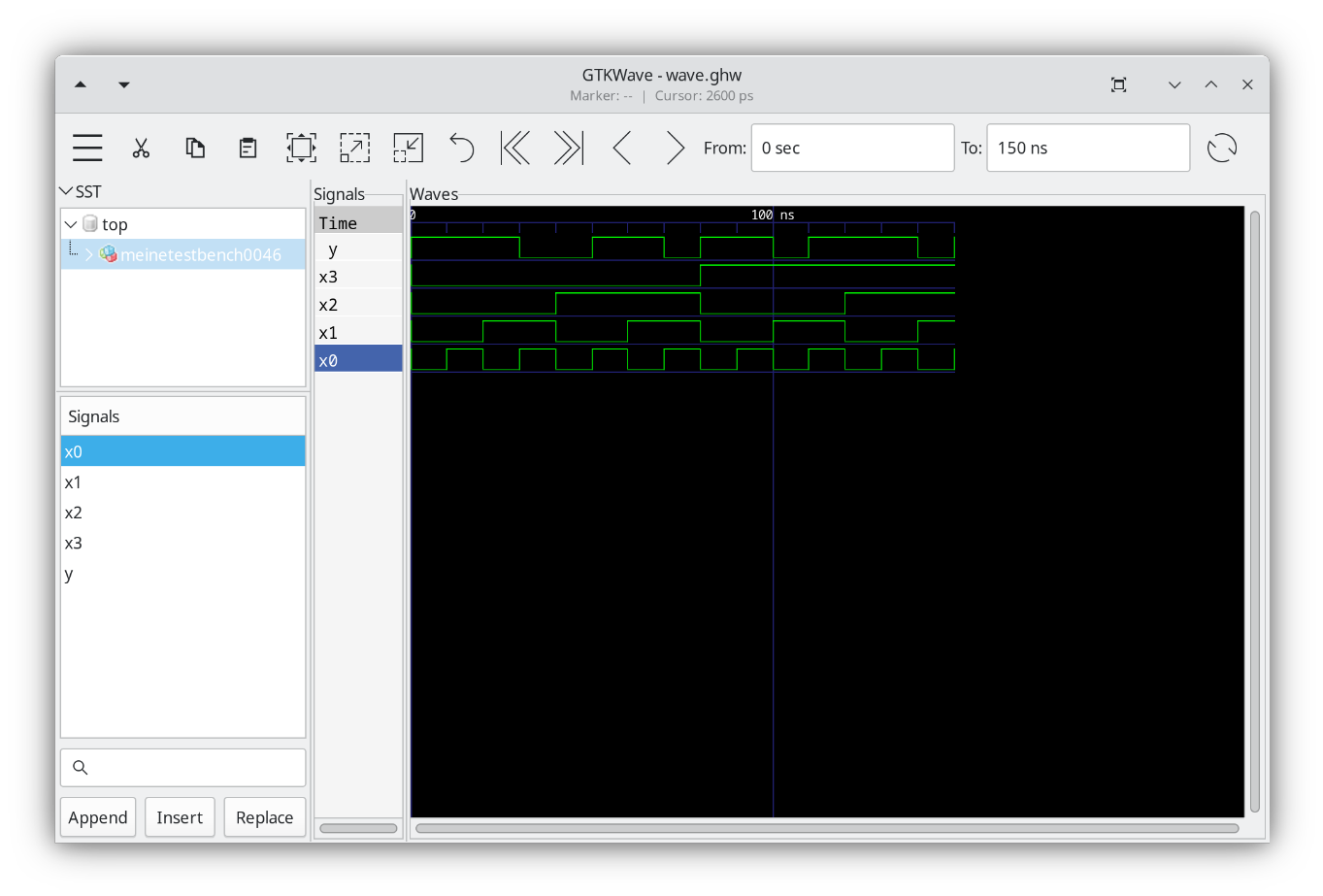

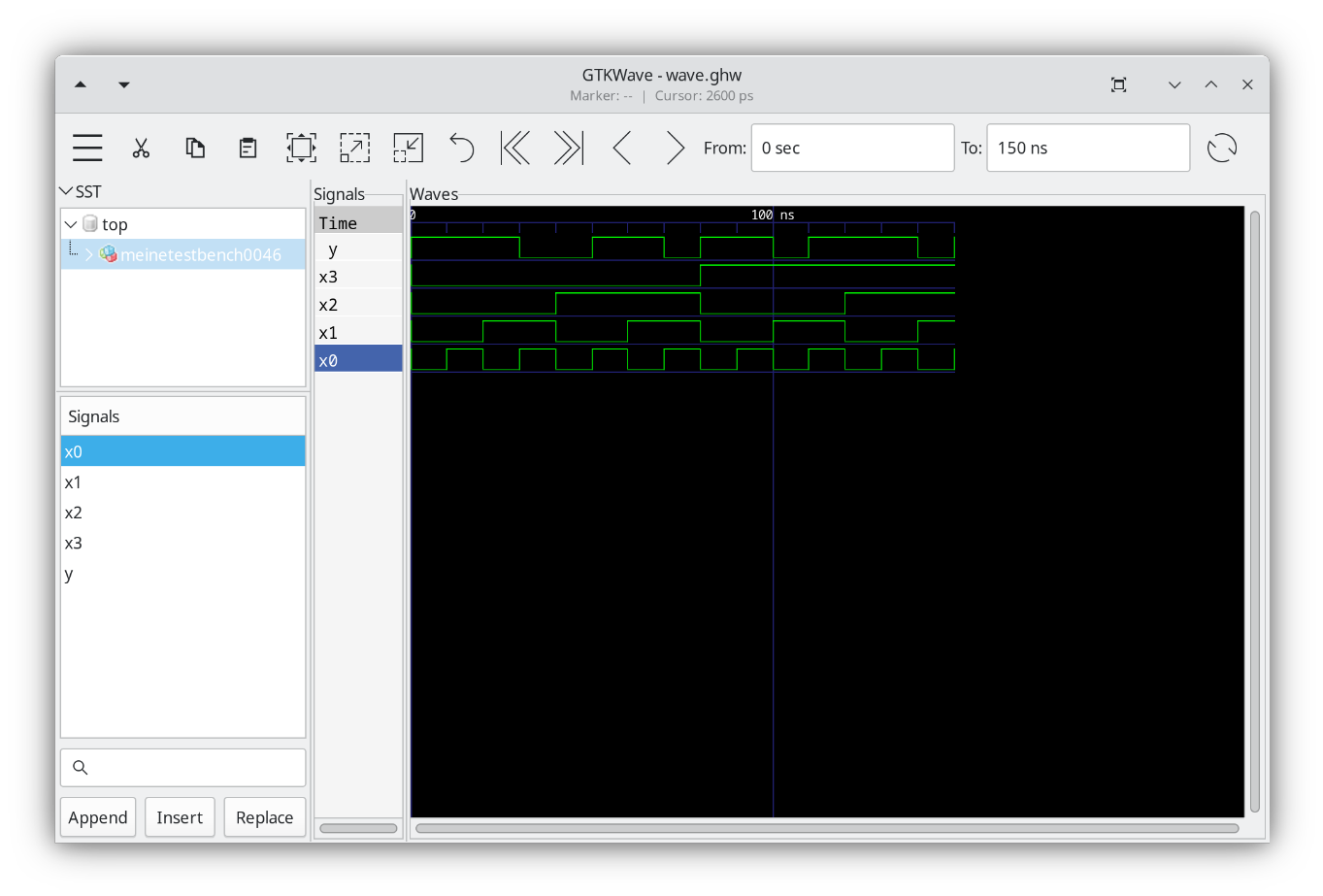

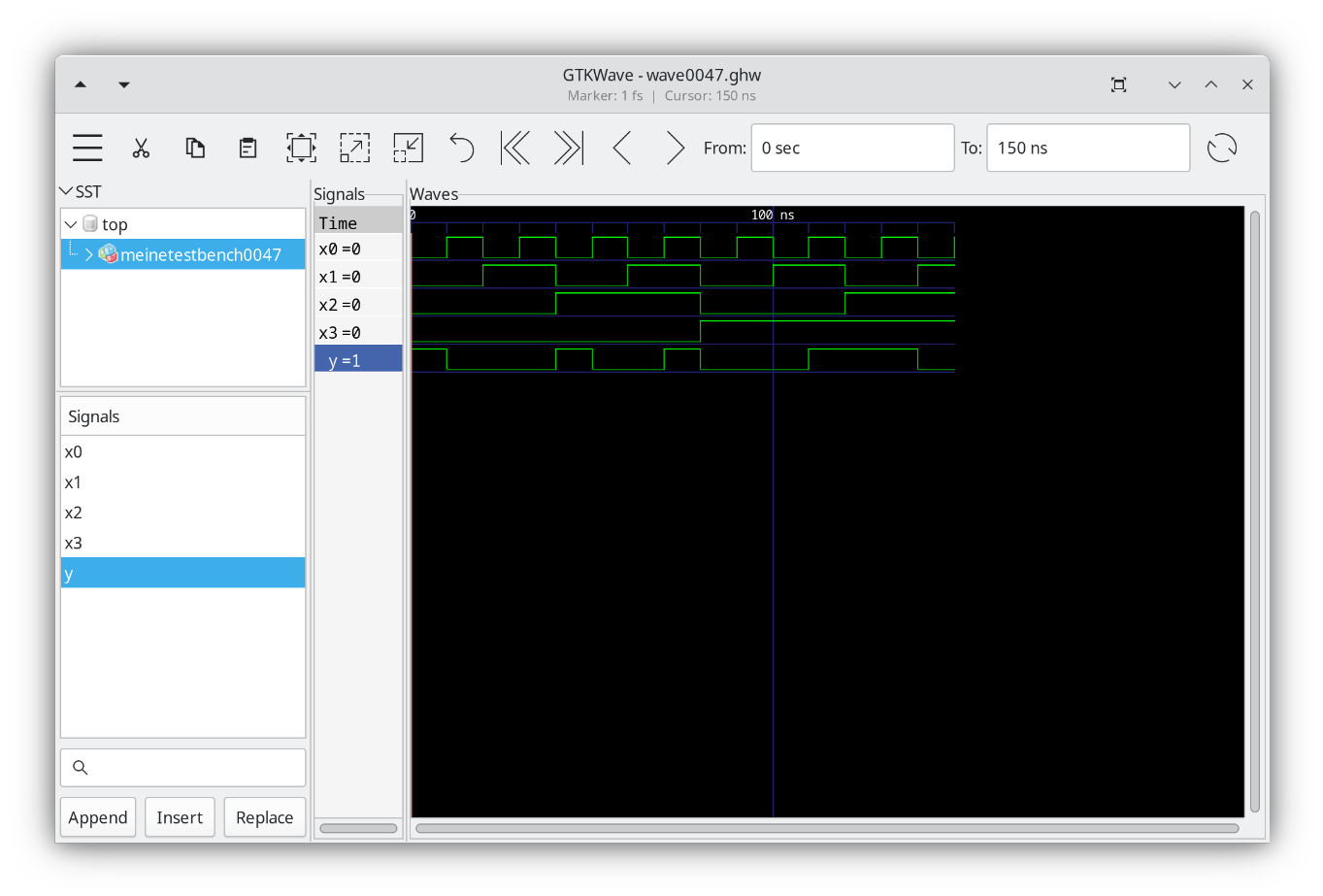

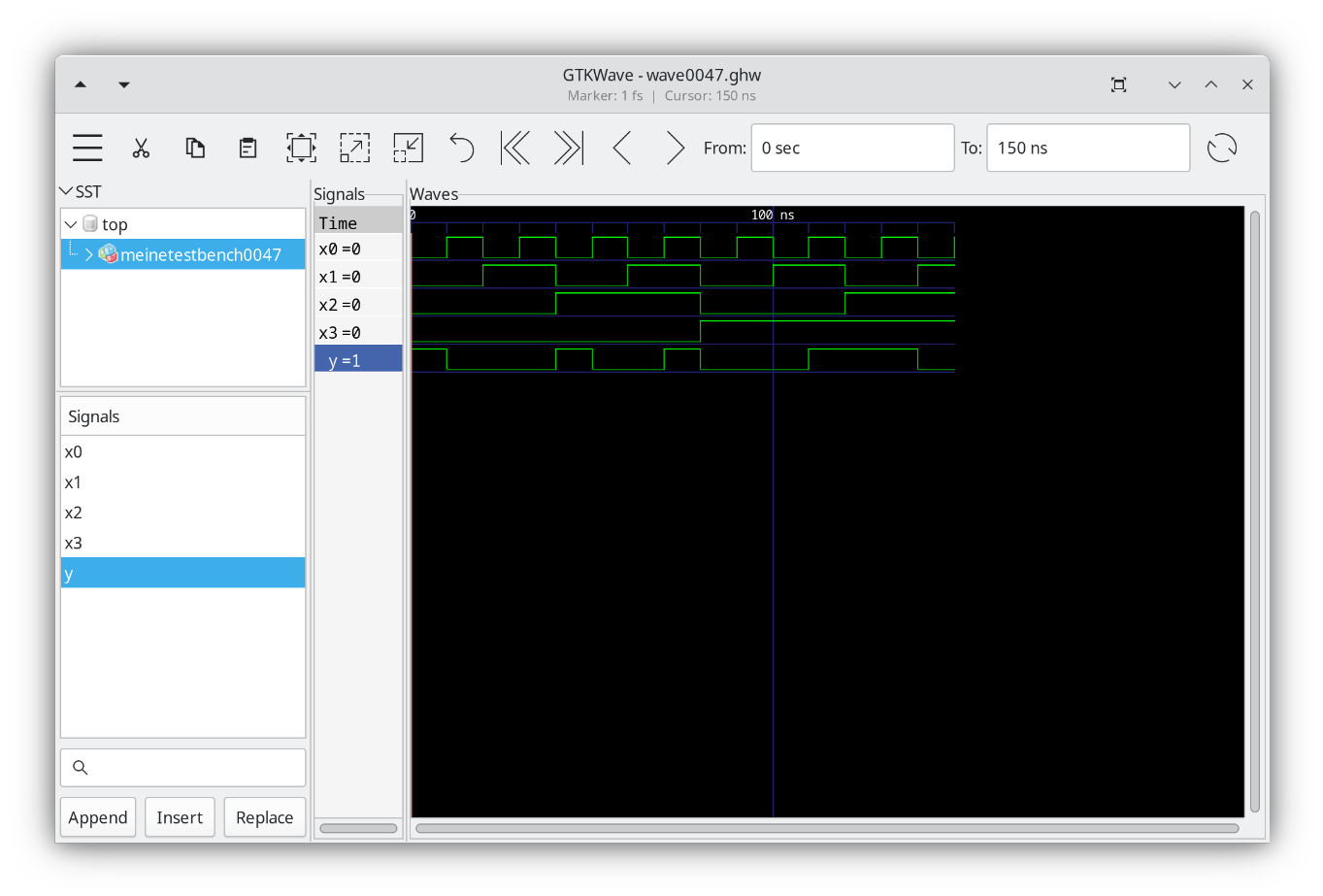

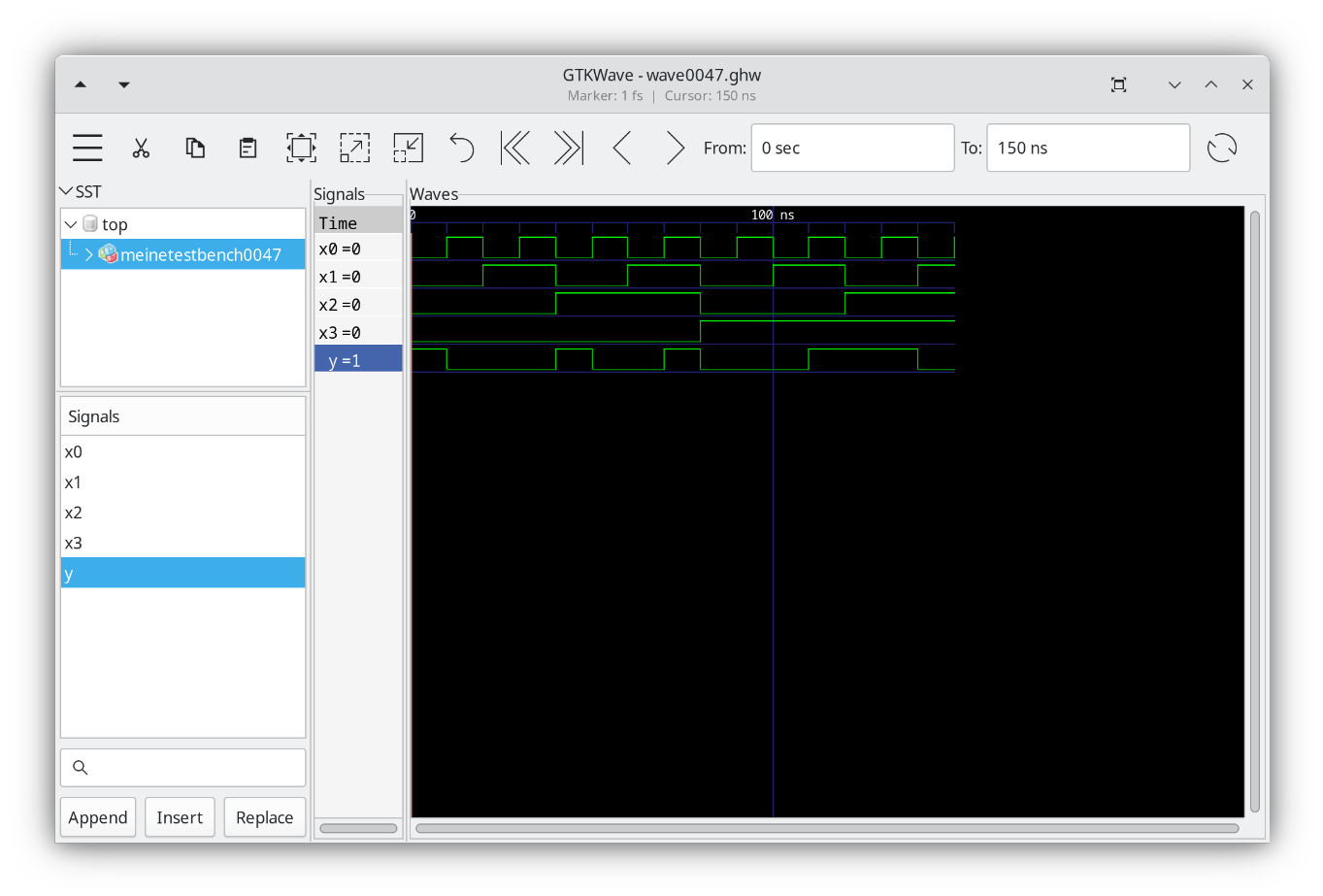

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz0043 is

port

(

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz0043 is

begin

y <= (x3 and not x1) or

(x3 and x2) or

(x3 and not x0) or

(x2 and x1 and not x0) or

(not x3 and not x2 and x1 and x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity testbench0043 is

port

(

y: out std_logic

);

end;

architecture verhalten of testbench0043 is

component meinschaltnetz0043

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

sn: meinschaltnetz0043 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;

[code]

[img] https://www.ituenix.de/nextcloud/data/dave/files/Documents/david4/2023-12-04/Screenshot_20231204_195113.png [/img]

[code]

0 0 0 0 0 0

1 0 0 0 1 0

2 0 0 1 0 0

3 0 0 1 1 1

4 0 1 0 0 0

5 0 1 0 1 0

6 0 1 1 0 1

7 0 1 1 1 0

8 1 0 0 0 1

9 1 0 0 1 1

10 1 0 1 0 1

11 1 0 1 1 0

12 1 1 0 0 1

13 1 1 0 1 1

14 1 1 1 0 1

15 1 1 1 1 1

0 0 0 0 0 0

1 0 0 0 1 0

2 0 0 1 0 0

3 0 0 1 1 1

4 0 1 0 0 0

5 0 1 0 1 0

6 0 1 1 0 1

7 0 1 1 1 0

8 1 0 0 0 1

9 1 0 0 1 1

10 1 0 1 0 1

11 1 0 1 1 0

12 1 1 0 0 1

13 1 1 0 1 1

14 1 1 1 0 1

15 1 1 1 1 1

3 0 0 1 1 1

6 0 1 1 0 1

8 1 0 0 0 1

9 1 0 0 1 1

10 1 0 1 0 1

12 1 1 0 0 1

13 1 1 0 1 1

14 1 1 1 0 1

15 1 1 1 1 1

Gruppe 1:

8 1 0 0 0 1

Gruppe 2:

3 0 0 1 1 1

6 0 1 1 0 1

9 1 0 0 1 1

10 1 0 1 0 1

12 1 1 0 0 1

Gruppe 3:

13 1 1 0 1 1

14 1 1 1 0 1

Gruppe 4:

15 1 1 1 1 1

8:9 1 0 0 -

8:10 1 0 - 0

8:12 1 - 0 0

3 0 0 1 1

6:14 - 1 1 0

9:13 1 - 0 1

10:14 1 - 1 0

12:13 1 1 0 -

12:14 1 1 - 0

13:15 1 1 - 1

14:15 1 1 1 -

12:13 1 1 0 -

8:9 1 0 0 -

14:15 1 1 1 -

8:10 1 0 - 0

12:14 1 1 - 0

13:15 1 1 - 1

8:12 1 - 0 0

9:13 1 - 0 1

10:14 1 - 1 0

6:14 - 1 1 0

3 0 0 1 1

8:9 1 0 0 -

12:13 1 1 0 -

14:15 1 1 1 -

8:10 1 0 - 0

12:14 1 1 - 0

13:15 1 1 - 1

8:12 1 - 0 0

9:13 1 - 0 1

10:14 1 - 1 0

6:14 - 1 1 0

3 0 0 1 1

Gruppe 1:

8:9 1 0 0 -

Gruppe 2:

12:13 1 1 0 -

Gruppe 3:

14:15 1 1 1 -

Gruppe 1:

8:10 1 0 - 0

Gruppe 2:

12:14 1 1 - 0

Gruppe 3:

13:15 1 1 - 1

Gruppe 1:

8:12 1 - 0 0

Gruppe 2:

9:13 1 - 0 1

10:14 1 - 1 0

6:14 - 1 1 0

3 0 0 1 1

Gruppe 1:

8:9 1 0 0 -

Gruppe 2:

12:13 1 1 0 -

Gruppe 3:

14:15 1 1 1 -

8:9:12:13 1 - 0 -

12:13:14:15 1 1 - -

Gruppe 1:

8:10 1 0 - 0

Gruppe 2:

12:14 1 1 - 0

Gruppe 3:

13:15 1 1 - 1

8:10:12:14 1 - - 0

12:14:13:15 1 1 - -

Gruppe 1:

8:12 1 - 0 0

Gruppe 2:

9:13 1 - 0 1

10:14 1 - 1 0

8:12:9:13 1 - 0 -

8:12:10:14 1 - - 0

6:14 - 1 1 0

3 0 0 1 1

8:9:12:13 1 - 0 -

12:13:14:15 1 1 - -

8:10:12:14 1 - - 0

12:14:13:15 1 1 - -

8:12:9:13 1 - 0 -

8:12:10:14 1 - - 0

6:14 - 1 1 0

3 0 0 1 1

8:9:12:13 1 - 0 -

8:12:9:13 1 - 0 -

12:13:14:15 1 1 - -

12:14:13:15 1 1 - -

8:10:12:14 1 - - 0

8:12:10:14 1 - - 0

6:14 - 1 1 0

3 0 0 1 1

8:9:12:13 1 - 0 -

12:13:14:15 1 1 - -

8:10:12:14 1 - - 0

6:14 - 1 1 0

3 0 0 1 1

3 6 8 9 10 12 13 14 15

6:14 * *

8:9:12:13 * * * *

12:13:14:15 * * * *

8:10:12:14 * * * *

3 *

3 8 9 10 12 13 14 15

8:9:12:13 * * * *

12:13:14:15 * * * *

8:10:12:14 * * * *

3 *

y <= (x3 and not x1) or

(x3 and x2) or

(x3 and not x0) or

(x2 and x1 and not x0) or

(not x3 and not x2 and x1 and x0)

y <= not((not x3 or x1) and

(not x3 or not x2) and

(not x3 or x0) and

(not x2 or not x1 or x0) and

(x3 or x2 or not x1 or not x0))

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz0043 is

port

(

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz0043 is

begin

y <= (x3 and not x1) or

(x3 and x2) or

(x3 and not x0) or

(x2 and x1 and not x0) or

(not x3 and not x2 and x1 and x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity testbench0043 is

port

(

y: out std_logic

);

end;

architecture verhalten of testbench0043 is

component meinschaltnetz0043

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

sn: meinschaltnetz0043 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;

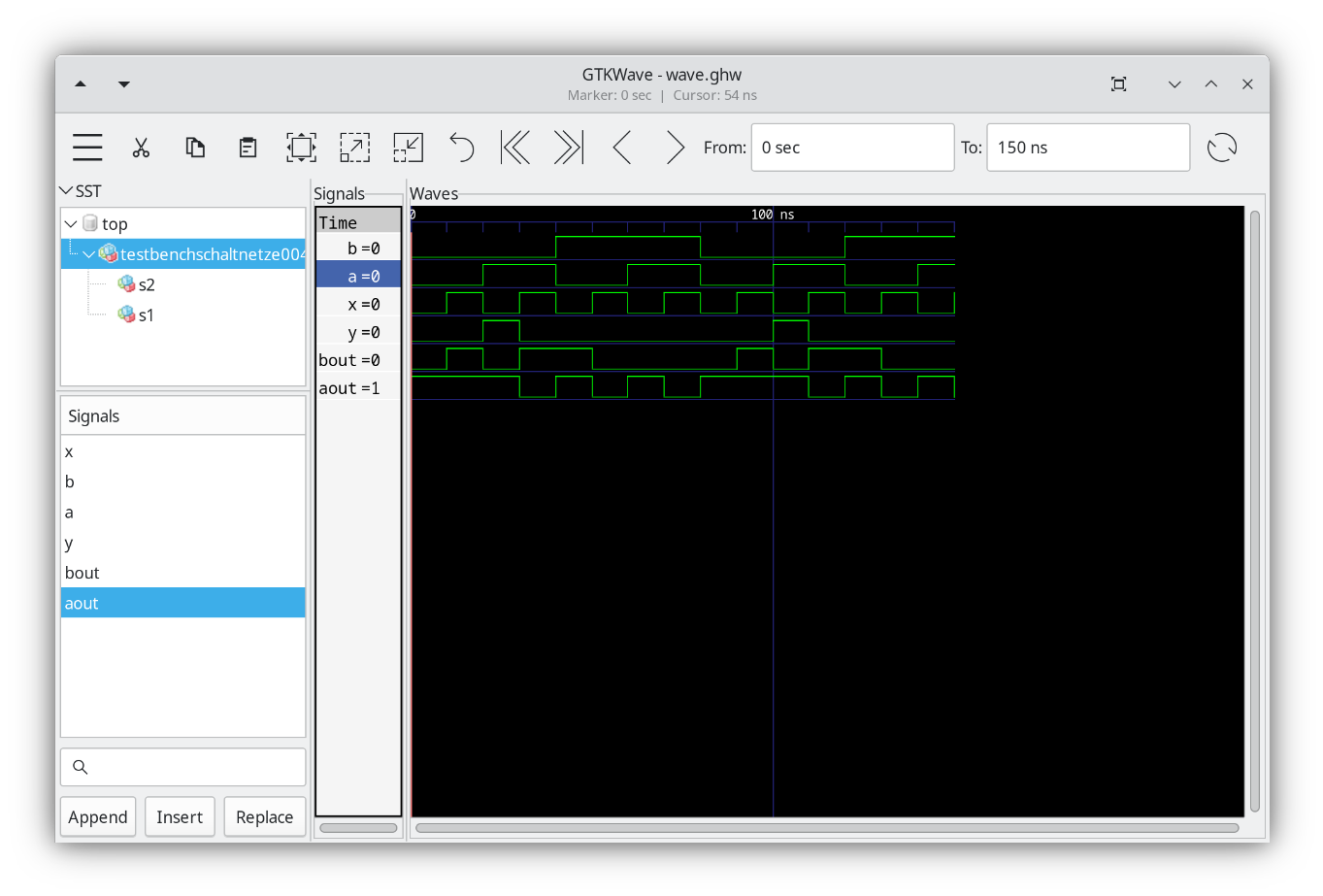

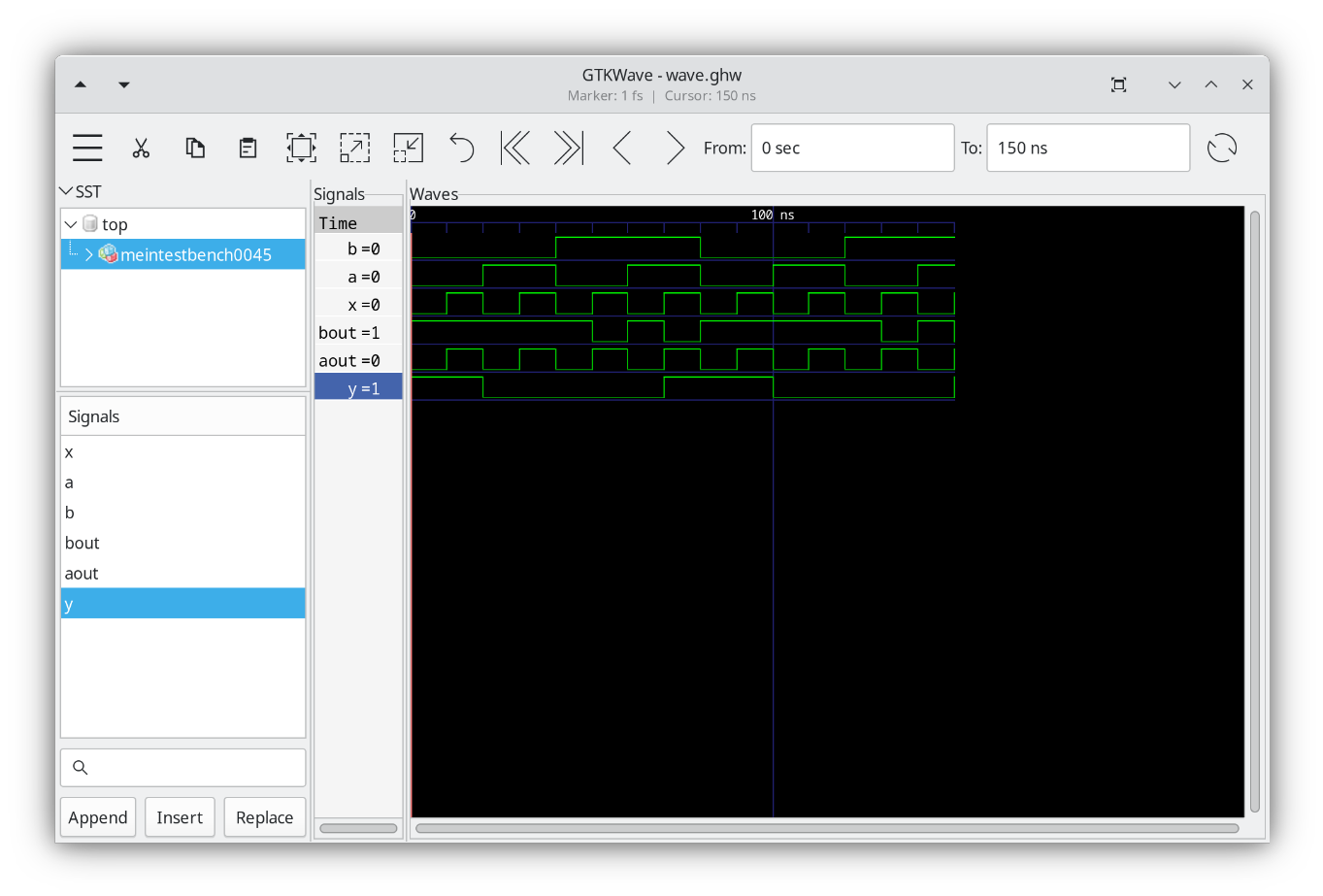

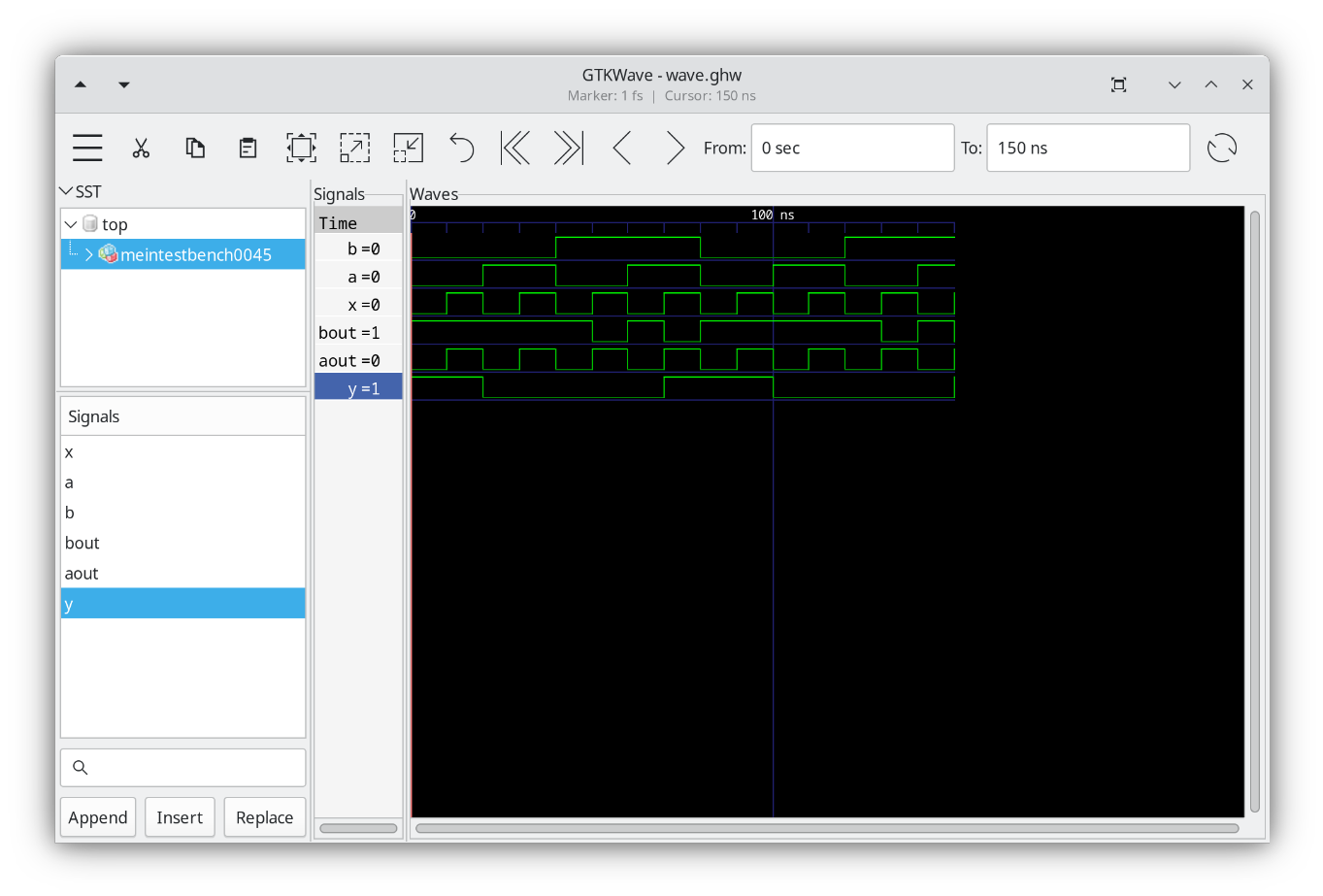

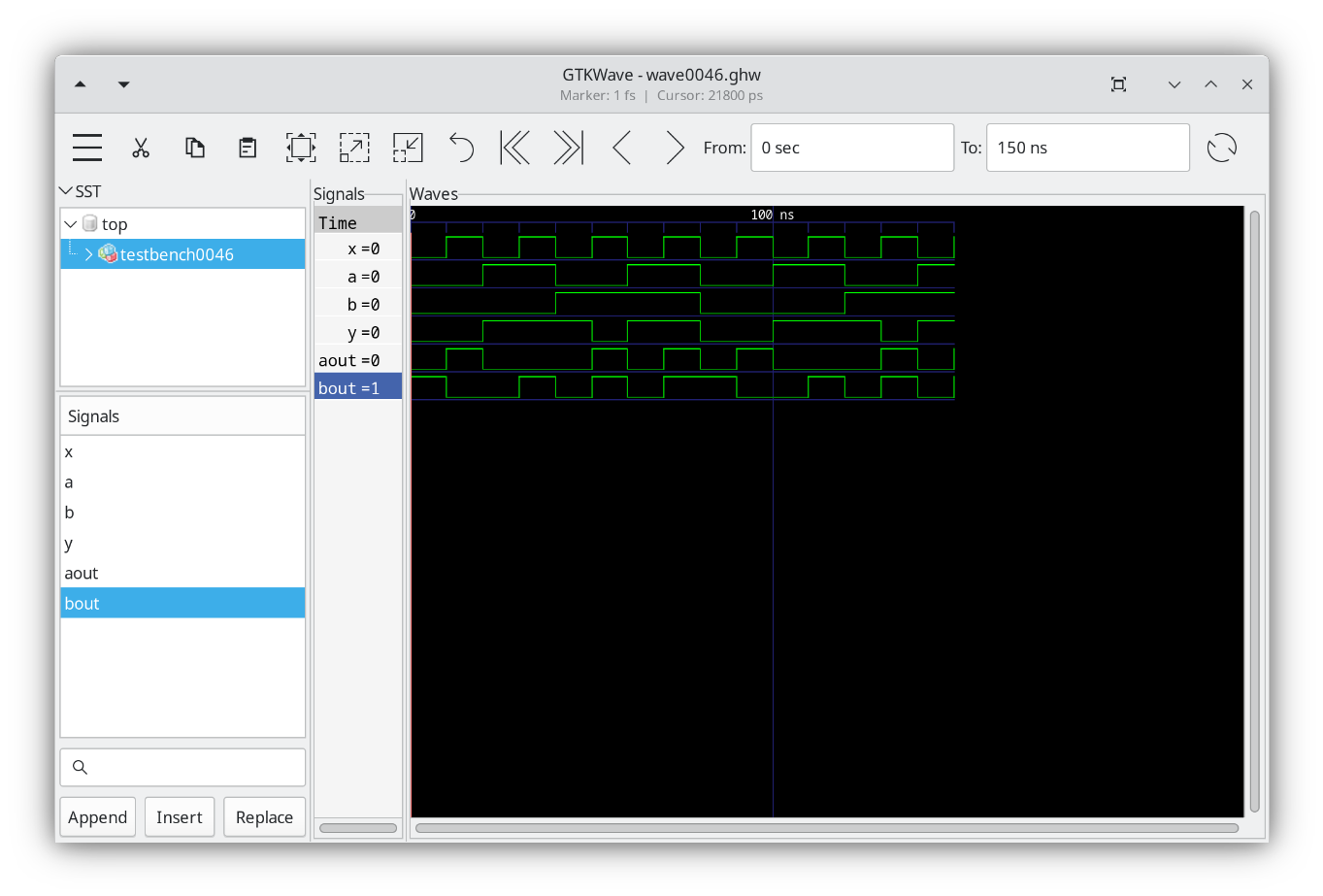

b a x b a y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 2 0 1 0 0 1 1 3 0 1 1 1 0 0 4 1 0 0 1 1 0 5 1 0 1 0 0 0 6 1 1 0 0 1 0 7 1 1 1 0 0 0 b a x b 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 1 4 1 0 0 1 5 1 0 1 0 6 1 1 0 0 7 1 1 1 0 b a x a 0 0 0 0 1 1 0 0 1 1 2 0 1 0 1 3 0 1 1 0 4 1 0 0 1 5 1 0 1 0 6 1 1 0 1 7 1 1 1 0 b a x y 0 0 0 0 0 1 0 0 1 0 2 0 1 0 1 3 0 1 1 0 4 1 0 0 0 5 1 0 1 0 6 1 1 0 0 7 1 1 1 0 b a x b 1 0 0 1 1 3 0 1 1 1 4 1 0 0 1 b a x a 0 0 0 0 1 1 0 0 1 1 2 0 1 0 1 4 1 0 0 1 6 1 1 0 1 b a x y 2 0 1 0 1 b a x b Gruppe 1: 1 0 0 1 1 4 1 0 0 1 Gruppe 2: 3 0 1 1 1 1:3 0 - 1 4 1 0 0 bout <= (not b and x) or (b and not a and not x); b a x a Gruppe 0: 0 0 0 0 1 Gruppe 1: 1 0 0 1 1 2 0 1 0 1 4 1 0 0 1 Gruppe 2: 6 1 1 0 1 0:1 0 0 - 0:2 0 - 0 0:4 - 0 0 2:6 - 1 0 4:6 1 - 0 0:4 - 0 0 2:6 - 1 0 0:2 0 - 0 4:6 1 - 0 0:1 0 0 - 0:4:2:6 - - 0 0:2:4:6 - - 0 0:1 0 0 - aout <= (not x) or (not b and not a); b a x y 2 0 1 0 1 bout <= (not b and x) or (b and not a and not x); aout <= (not x) or (not b and not a); y <= (not b and a and not x); library ieee; use ieee.std_logic_1164.all; entity meinausgangsschaltnetz0043 is port ( a, b, x: in std_logic; y: out std_logic ); end; architecture verhalten of meinausgangsschaltnetz0043 is begin y <= (not b and a and not x); end; library ieee; use ieee.std_logic_1164.all; entity meinuebergangsschaltnetz0043 is port ( a, b, x: in std_logic; aout, bout: out std_logic ); end; architecture verhalten of meinuebergangsschaltnetz0043 is begin bout <= (not b and x) or (b and not a and not x); aout <= (not x) or (not b and not a); end; library ieee; use ieee.std_logic_1164.all; entity testbenchschaltnetze0043 is port ( aout, bout, y: out std_logic ); end; architecture verhalten of testbenchschaltnetze0043 is component meinausgangsschaltnetz0043 port ( a, b, x: in std_logic; y: out std_logic ); end component; component meinuebergangsschaltnetz0043 port ( a, b, x: in std_logic; aout, bout: out std_logic; ); end component; signal a, b, x: std_logic begin u: meinuebergangsschaltnetz0043 PORT MAP (a=>a, b=>b, x=>x, aout=>aout, bout=>bout); a: meinausgangsschaltnetz0043 PORT MAP (a=>a, b=>b, x=>x, y=>y); x <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns; a <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns; b <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns; end;

b a x b a y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 2 0 1 0 0 1 1 3 0 1 1 1 0 0 4 1 0 0 1 1 0 5 1 0 1 0 0 0 6 1 1 0 0 1 0 7 1 1 1 0 0 0

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz0043 is

port

(

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz0043 is

begin

y <= (x3 and not x1) or

(x3 and x2) or

(x3 and not x0) or

(x2 and x1 and not x0) or

(not x3 and not x2 and x1 and x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity testbench0043 is

port

(

y: out std_logic

);

end;

architecture verhalten of testbench0043 is

component meinschaltnetz0043

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

sn: meinschaltnetz0043 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;

library ieee; use ieee.std_logic_1164.all; entity meinausgangsschaltnetz0043 is port ( a, b, x: in std_logic; y: out std_logic ); end; architecture verhalten of meinausgangsschaltnetz0043 is begin y <= (not b and a and not x); end; library ieee; use ieee.std_logic_1164.all; entity meinuebergangsschaltnetz0043 is port ( a, b, x: in std_logic; aout, bout: out std_logic ); end; architecture verhalten of meinuebergangsschaltnetz0043 is begin bout <= (not b and x) or (b and not a and not x); aout <= (not x) or (not b and not a); end; library ieee; use ieee.std_logic_1164.all; entity testbenchschaltnetze0043 is port ( aout, bout, y: out std_logic ); end; architecture verhalten of testbenchschaltnetze0043 is component meinausgangsschaltnetz0043 port ( a, b, x: in std_logic; y: out std_logic ); end component; component meinuebergangsschaltnetz0043 port ( a, b, x: in std_logic; aout, bout: out std_logic ); end component; signal a, b, x: std_logic; begin s1: meinuebergangsschaltnetz0043 PORT MAP (a=>a, b=>b, x=>x, aout=>aout, bout=>bout); s2: meinausgangsschaltnetz0043 PORT MAP (a=>a, b=>b, x=>x, y=>y); x <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns; a <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns; b <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns; end; library ieee; use ieee.std_logic_1164.all; entity rslatch0043 is port ( r, s: in std_logic; q: out std_logic ); end; architecture verhalten of rslatch0043 is signal q1, q2: std_logic; begin q1 <= (s nor q2); q2 <= (r nor q1); q <= q1; end; library ieee; use ieee.std_logic_1164.all; entity clkrslatch0043 is port ( r, s: in std_logic; q: out std_logic; c: in std_logic ); end; architecture verhalten of clkrslatch0043 is component rslatch0043 port ( r, s: in std_logic; q: out std_logic ); end component; signal r1, s1: std_logic; begin rs: rslatch0043 PORT MAP (r=>r1, s=>s1, q=>q); r1 <= r and c; s1 <= s and c; end; library ieee; use ieee.std_logic_1164.all; entity dlatch is port ( q: out std_logic; c, d: in std_logic ); end; architecture verhalten of dlatch is component clkrslatch0043 port ( r, s, c: in std_logic; q: out std_logic ); end component; signal d1, d2: std_logic; begin clkrs: clkrslatch0043 PORT MAP (r=>d1, s=>d2, c=>c, q=>q); d1 <= d; d2 <= not d; end; library ieee; use ieee.std_logic_1164.all; entity dmsff is port ( q: out std_logic; d, c: in std_logic ); end; architecture verhalten of dmsff is component dlatch port ( q: out std_logic; d, c: in std_logic ); end component; signal d1, d2: std_logic; signal c1, c2: std_logic; signal q1, q2: std_logic; begin master: dlatch PORT MAP (d=>d1, c=>c1, q=>q1); slave: dlatch PORT MAP (d=>d2, c=>c2, q=>q2); c1 <= c; c2 <= not c; d1 <= d; d2 <= q1; q <= q2; end;

library ieee;

use ieee.std_logic_1164.all;

entity meinausgangsschaltnetz0043 is

port

(

a, b, x: in std_logic;

y: out std_logic

);

end;

architecture verhalten of meinausgangsschaltnetz0043 is

begin

y <= (not b and a and not x);

end;

library ieee;

use ieee.std_logic_1164.all;

entity meinuebergangsschaltnetz0043 is

port

(

a, b, x: in std_logic;

aout, bout: out std_logic

);

end;

architecture verhalten of meinuebergangsschaltnetz0043 is

begin

--bout <= (not b and x) or

-- (b and not a and not x);

--aout <= (not x) or (not b and not a);

bout <= b xor a;

aout <= not a;

end;

library ieee;

use ieee.std_logic_1164.all;

entity testbenchschaltnetze0043 is

port (

aout, bout, y: out std_logic

);

end;

architecture verhalten of testbenchschaltnetze0043 is

component meinausgangsschaltnetz0043

port (

a, b, x: in std_logic;

y: out std_logic

);

end component;

component meinuebergangsschaltnetz0043

port (

a, b, x: in std_logic;

aout, bout: out std_logic

);

end component;

signal a, b, x: std_logic;

begin

s1: meinuebergangsschaltnetz0043 PORT MAP (a=>a, b=>b, x=>x, aout=>aout, bout=>bout);

s2: meinausgangsschaltnetz0043 PORT MAP (a=>a, b=>b, x=>x, y=>y);

x <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

a <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

b <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity rslatch0043 is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch0043 is

signal q1, q2: std_logic;

begin

q1 <= (s nor q2);

q2 <= (r nor q1);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clkrslatch0043 is

port (

r, s: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of clkrslatch0043 is

component rslatch0043

port

(

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rs: rslatch0043 PORT MAP (r=>r1, s=>s1, q=>q);

r1 <= r and c;

s1 <= s and c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port

(

q: out std_logic;

c, d: in std_logic

);

end;

architecture verhalten of dlatch is

component clkrslatch0043

port

(

r, s, c: in std_logic;

q: out std_logic

);

end component;

signal d1, d2: std_logic;

begin

clkrs: clkrslatch0043 PORT MAP (r=>d1, s=>d2, c=>c, q=>q);

d1 <= d;

d2 <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsff is

port

(

q: out std_logic;

d, c: in std_logic

);

end;

architecture verhalten of dmsff is

component dlatch

port

(

q: out std_logic;

d, c: in std_logic

);

end component;

signal d1, d2: std_logic;

signal c1, c2: std_logic;

signal q1, q2: std_logic;

begin

master: dlatch PORT MAP (d=>d1, c=>c1, q=>q1);

slave: dlatch PORT MAP (d=>d2, c=>c2, q=>q2);

c1 <= c;

c2 <= not c;

d1 <= d;

d2 <= q1;

q <= q2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltwerk0043 is

port

(

c: in std_logic;

we: in std_logic;

x: in std_logic

);

end;

architecture verhalten of meinschaltwerk0043 is

component dmsff

port

(

d, c: in std_logic;

q: out std_logic

);

end component;

component meinausgangsschaltnetz0043

port

(

a, b, x: in std_logic;

y: out std_logic

);

end component;

component meinuebergangsschaltnetz0043

port

(

a, b, x: in std_logic;

aout, bout: out std_logic

);

end component;

signal a, b, aout, bout, y: std_logic;

signal a1, b1, aout1, bout1: std_logic;

begin

z1: dmsff PORT MAP (d=>bout1, c=>c, q=>b);

z2: dmsff PORT MAP (d=>aout1, c=>c, q=>a);

s1: meinausgangsschaltnetz0043 PORT MAP (a=>a1, b=>b1, x=>x, y=>y);

s2: meinuebergangsschaltnetz0043 PORT MAP (a=>a1, b=>b1, aout=>aout, bout=>bout, x=>x);

aout1 <= aout when we='1' else '0';

bout1 <= bout when we='1' else '0';

a1 <= a when we='1' else '0';

b1 <= b when we='1' else '0';

end;

library ieee;

use ieee.std_logic_1164.all;

entity testbenchschaltwerk0043 is

port

(

y: out std_logic

);

end;

architecture verhalten of testbenchschaltwerk0043 is

component meinschaltwerk0043

port (

c: in std_logic;

we: in std_logic;

x: in std_logic

);

end component;

signal c: std_logic;

signal we: std_logic;

signal x: std_logic;

begin

sw: meinschaltwerk0043 PORT MAP (c=>c, we=>we, x=>x);

c <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

we <= '1' after 0 ns, '0' after 10 ns;

x <= '0' after 0 ns, '1' after 20 ns;

end;

Es ist mir nicht gelungen mit ghdl ein Blockdiagramm zu zeichnen. Eine direkte Lösung gibt es nicht.

Aber auf dieser Seite ist ein Vorschlag

https://blog.eowyn.net/netlistsvg/">https://blog.eowyn.net/netlistsvg/</URL>\\

\\

Ist recht simpel.\\

\\

ghdl selber zeichnet nichts. \\

\\

Man kann das tool \\

\\

yosys \\

\\

installieren. Und mit npm\\

\\

netlistsvg\\

\\

Das hat bei mir so weit getan - mit einem Unterschied. \\

\\

npm \\

\\

will netlistsvg \\

\\

nicht installieren. Weil es gibt eine vulnerabily zu gewissen Bibliotheken what ever. Der Fehler wird als fatal angegeben\\

\\

npm selber findet netlistsvg - aber da geht nichts\\

\\

Mir egal - wissen sie, es gibt solche Genies - die denken so: Das erste, was ich ja mache - ist den Schematic meines Schaltwerkes zu zeichnen. Und das nicht ohne Absicht - weil, ich meine, das ist "Ubung. Ist die Schematic automatisch gezeichnet, habe ich nichts ge"ubt\\

\\

Umgekehrt: Den Spezialisten geht es immer darum - Schematicen zu zeichnen.\\

\\

Spezialisten sind Leute, die benutzen wenig Linux - und sie denken sich eine Schaltung nicht in Form einer Logik\\

\\

Also \\

\\

1.) Wenn ich eine Schaltung habe, die tut - dann sehe ich das. Woran? Das ist ganz einfach - ich benutze ja GTKWave f"ur die Signale und vorausgesetzt ich weiss was ich tue - sehe ich bei GTKWave ja, ob die Signale stimmen - oder nicht?\\

\\

2.) Das zweite ist - diese reden von Profis \\

\\

- die verstehen das immer noch nicht - ich bin an der Fernuniversit"at in Hagen und studiere Informatik - OK - also: \\

\\

Sie werden am Ende verstehen - dass alle Programmierer und alle die in VHDL etwas tun - nicht anfangen Schematiken zu zeichnen \\

\\

Lassen sie mich das so sagen - sie entwerfen eine Schaltung - und die Schaltung hat auf dem FPGA Platz zu nehmen und das kann von mir aus ein Prozessor zum Beispiel ein MIPS sein - die Schematic ist ja sch"on, um zu lernen wie der FPGA geht, blos brauchen sie das nicht \\

\\

a) W"urden sie lernen wie in Computersystemen I/II\\

\\

dann w"urden sie wissen, eine Schaltung ist eine Logik und die k"onnen sie logisch hinschreiben \\

\\

b) Ich meine, sie bringen ja nicht ihre Schematik zur Ausf"uhrung, das ist ja sch"on, wenn das so aussieht, aber niemand will eine Schematic ausf"uhren \\

\\

c) Das aussehen hilft mir ja nichts - verstehen sie - dass Digitale Schaltungen Logik sind und wenn man jetzt sich Computersysteme I/II anschaut\\

\\

dann geht es nicht darum - dass man einfach lernt - es gibt solche Schaltelemente und solche\\

\\

sondern man lernt \\

\\

DIN33400\\

\\

DIN - das kennen sie von DIN A 4. Einem Standard, in Deutschland - f"ur Papier und Formate - da k"onnen sie ihre Richter bem"uhen. Die Richter sind derzeit sehr viel mit globalen Fragen beantwortet und behaupten auf alles eine Antwort zu haben, dazu sage ich - gucken sie mal in Deutschen Archiven nach\\

\\

ausser, dass es die Amerikanische Art und Weise gibt, etwas aus zu dr"ucken \\

\\

IEEE auf der einen Seite, entspricht in Deutschland DIN \\

\\

gibt es nat"urlich unsere Gatter \\

\\

7401\\

7404\\

7408\\

\\

sch"on. Und Deutschland? Deutschland hat die DIN. Das heisst, da stehen jetzt Papierstapel in den Aktenschr"anken und da steht alles sch"on definiert\\

\\

Sch"on, wenn man so weit guckt, dann stellt man fest - es gibt einen Zusammenhang zwischen Boolescher Algebra und Schaltalgebra. \\

\\

Und das ist der Witz, bei der Geschichte\\

\\

Die Schaltalgebra ist eine Boolesche Algebra - dazu muss man Mathematik k"onnen \\

\\

1.) Gruppen \\

2.) Halbgruppen\\

3.) Monoide\\

4.) K"orper \\

\\

und so weiter. Dann lernt man, dass es zum Beispiel \\

\\

Mengen mit einem oder zwei Operatoren gibt, die algebraisch sind - Mengen mit unz"ahligen Operatoren gibt es noch mehr\\

\\

Dann haben wir Distributivgesetzt, Kommutativ und Assoziativ in jedem Fall, wir haben Neutrale Elemente und Inverse\\

\\

Gut, dann w"urde man dahinter kommen, wie man Boolesche Algebra lernt und wenn man das hat - ja Mathematik Hauck, der T"ubinger Universit"at. Ich sass in der Mathematikpr"ufung und hatte immerhin eine 4. Mathematik Pr"ufung an der T"ubinger Uni bestanden mit 4. Wo die Pr"ufung ist keine Ahnung. Ich sage das Ergebnis ist beschissen, ich bin aber viel besser geworden\\

\\

Gut - imperative Programmierung habe ich bestanden - auf dem TG war ich - und ich schreibe jetzt Computersysteme I/II und habe vor das zu bestehen\\

\\

dass ich damals in Mathematik an der T"ubinger Uni nur eine 4 hatte. Sehen sie es so - ich war nicht gut in Form. Ich hatte Probleme und Unterlassungss"unden aus der Vergangenheit - da waren viele Sachen noch nicht drin - immerhin ich habe sie an der T"ubinger Uni bestanden\\

\\

Und kann es besser. Und jetzt hoffe ich ich bestehe Computersysteme I und II, und dann kann "uberhaupt keiner was\\

\\

So - aber - dann wissen sie, was Monoide, Gruppen Halbgruppen sind, k"onnen Algebra\\

\\

Gut und die Schaltalgebra ist laut DIN und Computersysteme I und II einfach eine Form der Booleschen Algebra, n"amlich eine die das als Schaltung repr"asentiert\\

\\

Und dann w"urde man wissen, dass es verschiedene Methoden gibt, Schaltelemente dar zu stellen\\

\\

N"amlich - das ist ja Mathematik\\

\\

Also, sie gehen in Mathematik. Sie gehen auf das Gymnasium und sie lernen in der achten Klasse, Funktionen zeichnen. \\

\\

Nun gut - dabei haben sie eine wundersch"one Kurve. Gut, und wenn sie sp"ater mal in die Uni rein schauen - dann haben sie Vektorfunktionen auf den reellen Bereich. gut - und was macht man da? Man zeichnet lauter Wirbelfelder - sp"atestens hier h"ort man auf Graphiker zu sein, weil Wirbelfelder will wirklich niemand zeichnen\\

\\

Das findet man dann in der Metereologie wieder\\

\\

Diese umfasst zwei Bereiche \\

\\

1.) Wirbelfelder, Vektoranalysis\\

2.) Statistik\\

\\

Ist im Endeffekt sehr simpel, vorausgesetzt man hat Datenspeicher und "uberall auf der Welt seine Messsensoren\\

\\

Gut, jetzt wird der Mathematiker ihnen nat"urlich zu recht erkl"aren - dass er ihnen weiter Funktionn zeichnet und das zu recht. Wer ihnen das Gegenteil erkl"art, erkl"art Unsinn\\

\\

weil sie besuchen ja auch mal die 8. Klasse. Und dann w"urden sie sonst nichts wissen\\

\\

Gut, aber, wenn sie so weit sind - werden sie wissen, dass es verschiedene Darstellungsformen Mathematisch gibt\\

\\

1.) Funktionsgleichung\\

2.) Wahrheitstabelle\\

3.) Schematik\\

4.) Bin"ares Entscheidungsdiagramm\\

...\\

\\

Und das lustige ist - dass die Schaltalgebra, Boolesche Algebra ist. Nur mit einer besonderen Form. Das heisst, aber, ob sie das logisch darstellen - also mit and or xor not - oder ob sie das hinzeichnen, das ist egal\\

\\

Und trotzdem beides Mathematik. Weil Schaltalgebra ist Boolesche Algebra\\

\\

Gut - und deswegen ist das relativ egal\\

\\

Nur, ich zeichne das nur deswegen, weil das "Ubung ist und wenn ich das automatisch mache, dann "ube ich nichts\\

\\

K"onnte ich trotzdem machen, wenn es nicht geht, egal\\

\\

Umgekehrt: Das sind die Windows Spezialisten. Ja? Die Fragen - wie machst du das? Und ich m"ochte das so und so - und da sieht man. Und dann kapieren sie die Schaltung nicht, aber wollen die Schematik\\

\\

Als, ob jemand, so einen Prozessor entwickelt. Das ist wirklich Windows. Die kliquen dann ihre Schaltelemente dahin und meinen jetzt haben sie eine Schaltung entworfen\\

\\

Also, wenn sie mich

1906 &

Es ist mir nicht gelungen mit ghdl ein Blockdiagramm zu zeichnen. Eine direkte L"osung gibt es nicht.\\

\\

Aber auf dieser Seite ist ein Vorschlag\\

\\

\begin{verbatim}https://blog.eowyn.net/netlistsvg/">https://blog.eowyn.net/netlistsvg/</URL>\\

\\

Ist recht simpel.\\

\\

ghdl selber zeichnet nichts. \\

\\

Man kann das tool \\

\\

yosys \\

\\

installieren. Und mit npm\\

\\

netlistsvg\\

\\

Das hat bei mir so weit getan - mit einem Unterschied. \\

\\

npm \\

\\

will netlistsvg \\

\\

nicht installieren. Weil es gibt eine vulnerabily zu gewissen Bibliotheken what ever. Der Fehler wird als fatal angegeben\\

\\

npm selber findet netlistsvg - aber da geht nichts\\

\\

Mir egal - wissen sie, es gibt solche Genies - die denken so: Das erste, was ich ja mache - ist den Schematic meines Schaltwerkes zu zeichnen. Und das nicht ohne Absicht - weil, ich meine, das ist "Ubung. Ist die Schematic automatisch gezeichnet, habe ich nichts ge"ubt\\

\\

Umgekehrt: Den Spezialisten geht es immer darum - Schematicen zu zeichnen.\\

\\

Spezialisten sind Leute, die benutzen wenig Linux - und sie denken sich eine Schaltung nicht in Form einer Logik\\

\\

Also \\

\\

1.) Wenn ich eine Schaltung habe, die tut - dann sehe ich das. Woran? Das ist ganz einfach - ich benutze ja GTKWave f"ur die Signale und vorausgesetzt ich weiss was ich tue - sehe ich bei GTKWave ja, ob die Signale stimmen - oder nicht?\\

\\

2.) Das zweite ist - diese reden von Profis \\

\\

- die verstehen das immer noch nicht - ich bin an der Fernuniversit"at in Hagen und studiere Informatik - OK - also: \\

\\

Sie werden am Ende verstehen - dass alle Programmierer und alle die in VHDL etwas tun - nicht anfangen Schematiken zu zeichnen \\

\\

Lassen sie mich das so sagen - sie entwerfen eine Schaltung - und die Schaltung hat auf dem FPGA Platz zu nehmen und das kann von mir aus ein Prozessor zum Beispiel ein MIPS sein - die Schematic ist ja sch"on, um zu lernen wie der FPGA geht, blos brauchen sie das nicht \\

\\

a) W"urden sie lernen wie in Computersystemen I/II\\

\\

dann w"urden sie wissen, eine Schaltung ist eine Logik und die k"onnen sie logisch hinschreiben \\

\\

b) Ich meine, sie bringen ja nicht ihre Schematik zur Ausf"uhrung, das ist ja sch"on, wenn das so aussieht, aber niemand will eine Schematic ausf"uhren \\

\\

c) Das aussehen hilft mir ja nichts - verstehen sie - dass Digitale Schaltungen Logik sind und wenn man jetzt sich Computersysteme I/II anschaut\\

\\

dann geht es nicht darum - dass man einfach lernt - es gibt solche Schaltelemente und solche\\

\\

sondern man lernt \\

\\

DIN33400\\

\\

DIN - das kennen sie von DIN A 4. Einem Standard, in Deutschland - f"ur Papier und Formate - da k"onnen sie ihre Richter bem"uhen. Die Richter sind derzeit sehr viel mit globalen Fragen beantwortet und behaupten auf alles eine Antwort zu haben, dazu sage ich - gucken sie mal in Deutschen Archiven nach\\

\\

ausser, dass es die Amerikanische Art und Weise gibt, etwas aus zu dr"ucken \\

\\

IEEE auf der einen Seite, entspricht in Deutschland DIN \\

\\

gibt es nat"urlich unsere Gatter \\

\\

7401\\

7404\\

7408\\

\\

sch"on. Und Deutschland? Deutschland hat die DIN. Das heisst, da stehen jetzt Papierstapel in den Aktenschr"anken und da steht alles sch"on definiert\\

\\

Sch"on, wenn man so weit guckt, dann stellt man fest - es gibt einen Zusammenhang zwischen Boolescher Algebra und Schaltalgebra. \\

\\

Und das ist der Witz, bei der Geschichte\\

\\

Die Schaltalgebra ist eine Boolesche Algebra - dazu muss man Mathematik k"onnen \\

\\

1.) Gruppen \\

2.) Halbgruppen\\

3.) Monoide\\

4.) K"orper \\

\\

und so weiter. Dann lernt man, dass es zum Beispiel \\

\\

Mengen mit einem oder zwei Operatoren gibt, die algebraisch sind - Mengen mit unz"ahligen Operatoren gibt es noch mehr\\

\\

Dann haben wir Distributivgesetzt, Kommutativ und Assoziativ in jedem Fall, wir haben Neutrale Elemente und Inverse\\

\\

Gut, dann w"urde man dahinter kommen, wie man Boolesche Algebra lernt und wenn man das hat - ja Mathematik Hauck, der T"ubinger Universit"at. Ich sass in der Mathematikpr"ufung und hatte immerhin eine 4. Mathematik Pr"ufung an der T"ubinger Uni bestanden mit 4. Wo die Pr"ufung ist keine Ahnung. Ich sage das Ergebnis ist beschissen, ich bin aber viel besser geworden\\

\\

Gut - imperative Programmierung habe ich bestanden - auf dem TG war ich - und ich schreibe jetzt Computersysteme I/II und habe vor das zu bestehen\\

\\

dass ich damals in Mathematik an der T"ubinger Uni nur eine 4 hatte. Sehen sie es so - ich war nicht gut in Form. Ich hatte Probleme und Unterlassungss"unden aus der Vergangenheit - da waren viele Sachen noch nicht drin - immerhin ich habe sie an der T"ubinger Uni bestanden\\

\\

Und kann es besser. Und jetzt hoffe ich ich bestehe Computersysteme I und II, und dann kann "uberhaupt keiner was\\

\\

So - aber - dann wissen sie, was Monoide, Gruppen Halbgruppen sind, k"onnen Algebra\\

\\

Gut und die Schaltalgebra ist laut DIN und Computersysteme I und II einfach eine Form der Booleschen Algebra, n"amlich eine die das als Schaltung repr"asentiert\\

\\

Und dann w"urde man wissen, dass es verschiedene Methoden gibt, Schaltelemente dar zu stellen\\

\\

N"amlich - das ist ja Mathematik\\

\\

Also, sie gehen in Mathematik. Sie gehen auf das Gymnasium und sie lernen in der achten Klasse, Funktionen zeichnen. \\

\\

Nun gut - dabei haben sie eine wundersch"one Kurve. Gut, und wenn sie sp"ater mal in die Uni rein schauen - dann haben sie Vektorfunktionen auf den reellen Bereich. gut - und was macht man da? Man zeichnet lauter Wirbelfelder - sp"atestens hier h"ort man auf Graphiker zu sein, weil Wirbelfelder will wirklich niemand zeichnen\\

\\

Das findet man dann in der Metereologie wieder\\

\\

Diese umfasst zwei Bereiche \\

\\

1.) Wirbelfelder, Vektoranalysis\\

2.) Statistik\\

\\

Ist im Endeffekt sehr simpel, vorausgesetzt man hat Datenspeicher und "uberall auf der Welt seine Messsensoren\\

\\

Gut, jetzt wird der Mathematiker ihnen nat"urlich zu recht erkl"aren - dass er ihnen weiter Funktionn zeichnet und das zu recht. Wer ihnen das Gegenteil erkl"art, erkl"art Unsinn\\

\\

weil sie besuchen ja auch mal die 8. Klasse. Und dann w"urden sie sonst nichts wissen\\

\\

Gut, aber, wenn sie so weit sind - werden sie wissen, dass es verschiedene Darstellungsformen Mathematisch gibt\\

\\

1.) Funktionsgleichung\\

2.) Wahrheitstabelle\\

3.) Schematik\\

4.) Bin"ares Entscheidungsdiagramm\\

...\\

\\

Und das lustige ist - dass die Schaltalgebra, Boolesche Algebra ist. Nur mit einer besonderen Form. Das heisst, aber, ob sie das logisch darstellen - also mit and or xor not - oder ob sie das hinzeichnen, das ist egal\\

\\

Und trotzdem beides Mathematik. Weil Schaltalgebra ist Boolesche Algebra\\

\\

Gut - und deswegen ist das relativ egal\\

\\

Nur, ich zeichne das nur deswegen, weil das "Ubung ist und wenn ich das automatisch mache, dann "ube ich nichts\\

\\

K"onnte ich trotzdem machen, wenn es nicht geht, egal\\

\\

Umgekehrt: Das sind die Windows Spezialisten. Ja? Die Fragen - wie machst du das? Und ich m"ochte das so und so - und da sieht man. Und dann kapieren sie die Schaltung nicht, aber wollen die Schematik\\

\\

Als, ob jemand, so einen Prozessor entwickelt. Das ist wirklich Windows. Die kliquen dann ihre Schaltelemente dahin und meinen jetzt haben sie eine Schaltung entworfen\\

\\

Also, wenn sie mich

1909 &

\begin{verbatim}

lb, lbu

lh, lhu

lw

ld*

la*

li*

sb

sh

sw

sd*

add, addi, addiu

sub

mult, multu

div, divu

and, andi

or, ori

xor, xori

not*, rem*, abs*, neg*

Datenbewegungsbefehle

arithmetisch logische Befehle

Schiebe und Rotationsbefehle

Gleitkommabefehle

Multimediabefehle

Programmsteuerbefehle

Systemsteuerbefehle

Synchronisationsbefehle

Dreiaddressformat

Zweiaddressformat

Einaddressformat

Nulladdressformat

Stack- und Kellerarchitektur

Register-Speicher Architektur

Speicher-Speicherarchitektur

Lade- und Speicherarchitektur

Akkumulatorarchitektur

Intel 8087, ATAM 862 Atmel

Little-Endian

Big-Endian

Einzelbit

Ganzzahl

Gleitkomma

Multimedia

Byte

Halbwort

Wort

Doppelwort

Quadwort

Ten Byte

signed

unsigned

packed

unpacked

bcd

ascii

ieee-754-std

f = (-1)\^s * 1.m * 2\^(e-b)

32: einfach

64: doppelt

80: erweitert

Unmittelbare Addressierung

Absolute Addressierung

Registeraddressierung

Direkte Addressierung

Indirekte Addressierung

Indirekte Addressierung mit Verschiebung

Indirekte Addressierung mit Autoinkrement/Dekrement

Indizierte Addressierung

Indizierte Addressierung mit Verschiebung

Steuereinheit

1.) Befehlsdekodierer

2.) Funktionsdekodierer

MemToReg

MemWrite

Branch

ALU-Src

RegDst

RegWrite

ALU-Op

Befehlsdekodierer

Funktionsdekodierer

Registersatz

ALU

Datenspeicher

Befehlsspeicher

Befehlsz"ahler

Vorzeichenerweiterungseinheit

4 x MUX

1 x AND

2 x Addierer

1 x 2 Bit Shifter

Befehlsdekodierer

- MemToReg

- MemWrite

- Branch

- ALU-Src

- ALU-Op

- RegDst

- RegWrite

Funktionsdekodierer

- Func

- ALU-Op

- ALU-Operation

Registersatz

- Lese-Daten-1

- Lese-Daten-2

- Schreibedaten

- Lese-Register-1

- Lese-Register-2

- Schreiberegister

- WE

Datenspeicher

- Lesedaten

- Schreibedaten

- Addresse

- WE

ALU

- Null

- Ergebnis

AND

- PCSrc

Befehlsspeicher

- Lesedaten

- Addresse

Befehlsz"ahler

- PC (t)

- PC (t+1)

Func ALU-Op ALU-Operation

00 x 010 - add

x1 x 110 - sub

1x 100 000 - add 010 - add

OpCode RegDst RegWrite Branch ALU-Src MemToReg MemWrite ALU-Op

r-typ 000 000 1 1 0 0 0 0 10

Verzweigungsbefehle

1.) Bedingt

2.) Unbedingt

eq - equal

ne - not equal

gt - greater than

ge - greater than equal

lt - less than

le - less than equal

Absolut: Branch

Befehlsz"ahlerrelativ: Jump

Befehlsz"ahlerindirekt: Jump Register

JAL: Jump and Link: Speichern zus"atzlich die Addresse die dem Befehl folgt

PC_neu = PC_alt + (i << 2)

PC_neu = PC_alt \& 0xf000 0000 | (i << 2)

j, b*, jr

jal

jalr

beq, bne

beqz*, bnez*

bgt*, bge*

bltz, blez

blt*, ble*

bgtz, bgez

Mehrzyklus Zustandselemente

- Befehlsspeicher

- Befehlsz"ahler

- Registersatz

- Datenspeicher

Pipeline-Prinzip

Pipeline-Stufe

Pipeline-Takt

1.) Befehl Holen

2.) Befehl dekodieren

3.) Operanden der ALU bereitstellen

4.) Operation in der ALU ausf"uhren

5.) Operanden in Architekturregister zur"uckschreiben

1.) IF - Instruction Fetch - Befehls bereitstellungsphasen

2.) ID - Instruction Decode / Register Fetch - Befehlsdekodierphase Operanden Bereitstellungsphasen

3.) EX - Execute / Address Calculation - Ausf"uhrungsphase

4.) MEM - Memory Access / Speicherzugriffsphase

5.) WB - Write Back / Resultatsspeicherphase

1.) Datenkonflikte

2.) Steuerflusskonflikte

3.) Struktur und Ressourcenkonflikte

1.) In Order Issue In Order Completion: OOE-Prozessor

2.) Out Of Order Issue Out Of Order Completion: VLIW-Prozessor

1.) Statische Sprungvorhersage, durch die Hardware

1.1.) Predict Always Not Taken

1.2.) Predict Always Taken

1.3.) Predict Backward Taken forward Not Taken

2.) Dynamisch: 1 und 2 Bit Pr"adiktor

2.1.) 1 Bit Pr"adiktor: Taken -> Not Taken, Not Taken -> Taken

2.2.) 2 Bit Pr"adiktor: Strongly/ Weakly Taken/Not Taken

Schaltnetze

Schaltwerke

Komplexe Schaltwerke

Aufbau und Funktionsweise eines Computers

Schaltnetze

Boolesche Algebra

Definition der Booleschen Algebra

Schaltalgebra ein Modell der Booleschen Algebra

Schaltfunktion

Definition

Darstellung

Minimierung

Analyse von Schaltnetzen

Synthese von Schaltnetzen

Kodierglieder

Schaltnetzentwurf f"ur den 8421-BCD-zu 7 Segmentumsetzung

Schaltnetzentwurf f"ur den Addresskodierer

Addierglieder

Halbaddierer

Volladdierer

Paralleladdierer

Komperatoren

Multiplexer

ALU

Zahlendarstellung und Zweierkomplement

Addierer/Subtrahierer

Schaltnetze mit Programmierbaren Baustein

ROM

PROM, EPROM

PAL, PLA

Laufzeiteffekte in Schaltnetzen

Schaltwerke

Implementierung von Schaltwerken

Modelle f"ur Schaltwerke

Synthese f"ur Schaltwerke

Analyse f"ur Schaltwerke

Speicherglieder

Transformation Mealy und Moore Automat

Schaltwerke mit Bin"arcodierten Zustand

Komplexe Schaltwerke

Aufbau komplexer Schalterwerke

Entwurf komplexer Schaltwerke

RTL-Notation

ASM-Diagramme

Zustandsboxen

Entscheidungsboxen

Bedingte Ausgangsboxen

ASM-Block

Operationswerk ...

Beispieln Einsenz"ahler

Komplexes Schaltwerk Mealy

Komplexes Schaltwerk Moore

Konstroktionsregeln Operationswerke

Mealy Schaltwerk als Konventionelles Schaltwerk

Mealy Steuerwerk mit Hotone Zustan d

Moore Steuerwerk als Konoventielles Schaltwerk

Moore Steuer mit Hotone Kodierung

Mikroprogrammierte Steuerwerk

Aufbau und Funktionsweise eins Computer

Erweiterung komplexer Schaltwerke

Komponenten eines Computers

Rechenwerk

Leitwerk

Speicher

Ein und Ausgaben

Datenpfade und Steuerpfade

Anwendung des Stapelzeigers

Unterprogramme

Unterbrechungen = Interrupts

Rechenwerk

Steuerwerk

Schaltalgebra: Boolesche Algebra, wo Elektrische Schaltungen, Spannungen als Boolesche Werte 0 und 1 interpretieren

Schaltfunktion, Vektorfunktion

Eingangsvektor, Ausgangsvektor

Eingangsvariable, x0, x1, x2, ..., xn

Eingangsvektor

Schaltnetz

Ausgangsvektor

f:{0,1}\^n -> {0,1}\^m

Schaltfunktion: DIN44300/93

Schaltnet: DIN44300/87

Darstellung

- KV-Diagramm

- Wahrheitstaballe

- Funktionsgleichung

- Sprache

- Bin"ares Entscheidungsdiagramm

- Schematik

Das gibt f"ur die Schaltfunktion, oder das einzelne Element und f"ur das gesamte Netz

Gesetze

- Assoziativ

- Distributiv

- Kommutativ

- Absorbtion

- Neutrale Elemente

- Inverse Elemente

- De Morgan

- Dualtit"atsprinzip

Verkn"upfung, Operatoren, was auch immer

- 0

- 1

- Konjunktion, AND

- Disjunktion, OR

- NAND

- NOR

- Komplement, Invers, NOT

- "Aquivalenz

- Antivalenz

- Transfer

- Inhibition

- Implikation

Kodierer: 40700/121 oder so - Ein Schaltnetz was dem Zeichen eines Zeichenvorrats das Zeichen eines anderen Zeichenvorrats zu ordnent

Dekodierer: Ist ein Kodierer mit Eingangs und Ausgangssignal, bei dem Pro Kombination von Eingangssignalen immer nur ein Ausganssignal den Wert 1 annimmt

Volladdierer

S = A XOR B XOR C

U = (A AND B) OR (A OR B) AND C

PLHS18P8

Schaltnetze: Elektronische Schaltungen die Spannungen als Variablen 0 und 1 interpretieren

Schaltnetze: Elektronische Schaltungen die Spannungen als logische Variablen 0 und 1 interpretieren

Schaltnetze: Eelktronische Schaltungen die Spannungen als logische Variablen 0 und 1 interpretieren

Schaltnetze: Elektronsiche Schlatungen diie Spannungen als logische Variablen 0 und 1 interpretieren

Boolesche Algebra, Schaltalgebra

Boolesche Algebra, Schaltalgebra

Boolesche Algebra, Schaltalgebra

Boolesche Algebra, Schaltalgebra

Boolesche Algebra, Schaltalgebra

Verkn"upfungsglieder, Schaltfunktion, Vektorfunktion

Verkn"upfungsglieder, Schaltfunktion, Vektorfunktion

Verkn"upfungsglieder, Schaltfunktion, Vektorfunktion

Verkn"upfungsglieder, Schaltfunktion, Vetkorfunktion

Verkn"ufungsglieder, Schaltfunktion, Vektorfunktion

F:{0,1}\^n -> {0,1}\^m

F:{0,1}\^n -> {0,1}\^m

F:{0,1}\^n -> {0,1}\^m

F:{0,1}\^n -> {0,1}\^m

F:{0,1}\^n -> {0,1}\^m

Eingangsvektor

Eingangsvariablen x1, x2, ..., xn

Eingangsvektor

Eingangsvariablen x1, x2, ..., xn

Eingangsvektor

Eingangsvariablen x1, x2, ..., xn

Eingangsvektor

Eingangsvariablen x1, x2, ..., xn

DIN44300/93: Schaltnetz

DIN44300/93: Schaltnetz

DIN44300/93: Schaltnetz

DIN44300/93: Schaltnetz

DIN44300/93: Schaltnetz

DIN44300/93: Schaltnetz

DIN44300/93: Schaltnetz

Eingangsvektor Schaltnetz Ausgangsvektor

Eingangsvektor Schaltnetz Ausgangsvektor

Eingangsvektor Schaltnetz Ausgansgvektor

Eingangsvektor Schaltnetz Ausgangsvektor

Eingangsvektor Schaltnetz Ausgangsvektor

Gesetze: Kommutativ, Assoziativ, Distributiv, Absorbtion

Gesetze: Kommutativ, Assoziativ, Distributiv, Absorbtion

Gesetze: Kommutativ, Assoziativ, Distributiv, Absorbtion

Gesetze: Kommutativ, Assoziativ, Distributiv, Absorbtion

Gesetze: Kommutativ, Assoziativ, Distributiv, Absorbition

Gesetze: Kommutativ, Assoziativ, Distributiv, Absorbition

Neutrales Element, Inverses Elemente, Dualit"atsprinzip, De Morgan

Neutrales Element, Inverses Element, Dualit"atsprinzip De Morgan

Neutrales Element, Inverses Element, Dualit"atsprinzip, De Morgan

Neutrales Element, Inverses Element, Dualit"atsprinzip, De Morgan

Neutrales Element, Inverses Element, Dualti"atsprinzip, De Morgan

DIN44300/87: Schaltfuntkion

DIN44300/87: Schaltfunktion

DIN44300/87: Schaltfunktion

DIN44300/87: Schaltfunktion

DIN44300/87: Schaltfunktion

Benennung der Verkn"upfung: Null, Eins

Bennenung der Verkn"upfung: Null, Eins

Bennennung der Verkn"upfung: Null, Eins

Benennung der Verkn"upfung: Null, Eins

Bennenunng der Verkn"upfung: Null, Eins

Konjunktion, Disjunktion

Konjunktion, Disjunktion

Konjunktion, Disjunktion

Konjunktion, Disjunktion

Konjunktion, Disjunktion

NAND, NOR, NAND, NOR, NAND, NOR, NAND, NOR, NAND, NOR

Antivalenz, "Aquivalenz

Antivalenz, "Aquivalenz

Antivalenz, "Aquivalenz

Antivalenz, "Aquivalenz

Antivalenz, "Aquivalenz

Inhibition, Transfer, Komplement, Implikation

Inhibition, Transfer, Komplement, Implikation

Inhibition, Transfer, Komplement, Implikation

Inhibition, Transfer, Komplement, Implikation

Inhibition, Transfer, Komplement, Implikation

Darstellung

- Funktionstabelle

- Funktionsgleichung

- KV-Diagramm

- Bin"ares Entscheidungsdiagramm

- Schaltzeichen

Darstellung

- Funktionstabelle

- Funktionsgleichung

- KV-Diagramm

- Bin"ares Entscheidungsdiagramm

- Schaltzeichen

Darstellung

- Funktionstabelle

- Funktionslgleichugn

- KV-Diagramm

- Bin"ares Entscheidungsdiagramm

- Schaltzeichen

S = A XOR B XOR C

S = A XOR B XOR C

S = A XOR B XOR C

S = A XOR B XOR C

S = A XOR B XOR C

S = A XOR B XOR C

U = (A AND B) OR (A OR B) AND C

U = (A AND B) OR (A OR B) AND C

U = (A AND B) OR (A OR B) AND C

U = (A AND B) OR (A OR B) AND C

U = (A AND B) OR (A OR B) AND C

U = (A AND B) OR (A OR B) AND C

PLHS 18P8

PLHS 18P8

PLHS 18P8

PLHS 18P8

PLHS 18P8

PLHS 18P8

0 0 0 0 0 0

1 0 0 0 1 1

2 0 0 1 0 0

3 0 0 1 1 1

4 0 1 0 0 1

5 0 1 0 1 0

6 0 1 1 0 1

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 0

10 1 0 1 0 1

11 1 0 1 1 1

12 1 1 0 0 1

13 1 1 0 1 0

14 1 1 1 0 0

15 1 1 1 1 1

1 0 0 0 1 1

3 0 0 1 1 1

4 0 1 0 0 1

6 0 1 1 0 1

7 0 1 1 1 1

8 1 0 0 0 1

10 1 0 1 0 1

11 1 0 1 1 1

12 1 1 0 0 1

15 1 1 1 1 1

Gruppe 1:

1 0 0 0 1 1

4 0 1 0 0 1

8 1 0 0 0 1

Gruppe 2:

3 0 0 1 1 1

6 0 1 1 0 1

10 1 0 1 0 1

12 1 1 0 0 1

Gruppe 3:

7 0 1 1 1 1

11 1 0 1 1 1

Gruppe 4:

15 1 1 1 1 1

1:3 0 0 - 1

4:6 0 1 - 0

4:12 - 1 0 0

8:10 1 0 - 0

8:12 1 - 0 0

3:7 0 - 1 1

3:11 - 0 1 1

6:11 0 1 1 -

10:11 1 0 1 -

7:15 - 1 1 1

11:15 1 - 1 1

4:12 - 1 0 0

3:11 - 0 1 1

7:15 - 1 1 1

8:12 1 - 0 0

3:7 0 - 1 1

11:15 1 - 1 1

1:3 0 0 - 1

4:6 0 1 - 0

8:10 1 0 - 0

6:11 0 1 1 -

10:11 1 0 1 -

Gruppe 1:

4:12 - 1 0 0

Gruppe 2:

3:11 - 0 1 1

Gruppe 3:

7:15 - 1 1 1

Gruppe 1:

8:12 1 - 0 0

Gruppe 2:

3:7 0 - 1 1

Gruppe 3:

11:15 1 - 1 1

Gruppe 1:

1:3 0 0 - 1

4:6 0 1 - 0

8:10 1 0 - 0

Gruppe 2:

6:11 0 1 1 -

10:11 1 0 1 -

Gruppe 1:

4:12 - 1 0 0

Gruppe 2:

3:11 - 0 1 1

Gruppe 3:

7:15 - 1 1 1

4:12 - 1 0 0

3:11:7:15 - - 1 1

Gruppe 1:

8:12 1 - 0 0

Gruppe 2:

3:7 0 - 1 1

Gruppe 3:

11:15 1 - 1 1

3:7:11:15 - - 1 1

Gruppe 1:

1:3 0 0 - 1

4:6 0 1 - 0

8:10 1 0 - 0

Gruppe 2:

6:11 0 1 1 -

10:11 1 0 1 -

4:12 - 1 0 0

3:11:7:15 - - 1 1

8:12 1 - 0 0

3:7:11:15 - - 1 1

1:3 0 0 - 1

4:6 0 1 - 0

8:10 1 0 - 0

6:11 0 1 1 -

10:11 1 0 1 -

3:11:7:15 - - 1 1

4:12 - 1 0 0

8:12 1 - 0 0

1:3 0 0 - 1

4:6 0 1 - 0

8:10 1 0 - 0

6:11 0 1 1 -

10:11 1 0 1 -

1 3 4 6 7 8 10 11 12 15

3:11:7:15 * * * *

4:12 * *

8:12 * *

1:3 * *

4:6 * *

8:10 * *

6:11 * *

10:11 * *

1

3

4

6

7

8

10

11

12

15

1 3 4 6 7 8 10 11 12 15

3:11:7:15 * * * *

4:12 * *

1:3 * *

4:6 * *

8:10 * *

3:11:7:15 - - 1 1

4:12 - 1 0 0

1:3 0 0 - 1

4:6 0 1 - 0

8:10 1 0 - 0

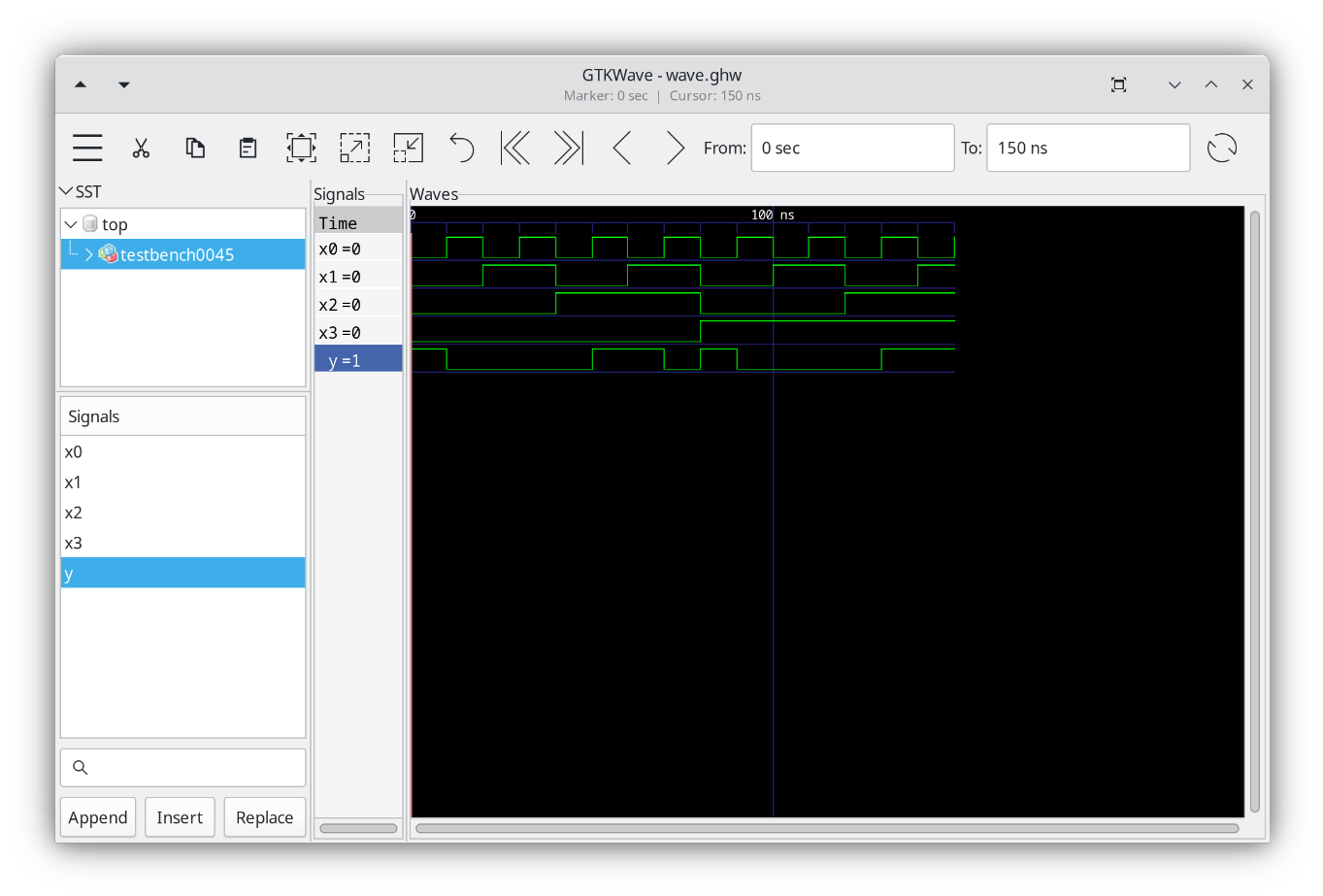

DNF:

y <= (x1 and x0) or

(x2 and not x1 and not x0) or

(not x3 and not x2 and x0) or

(not x3 and x2 and not x0) or

(x3 and not x2 and not x0)

y <= not()(not x1 or not x0) and

(not x2 or x1 or x0) and

(x3 or x2 or not x0) and

(x3 or not x2 or x0) and

(not x3 or x2 or x0))

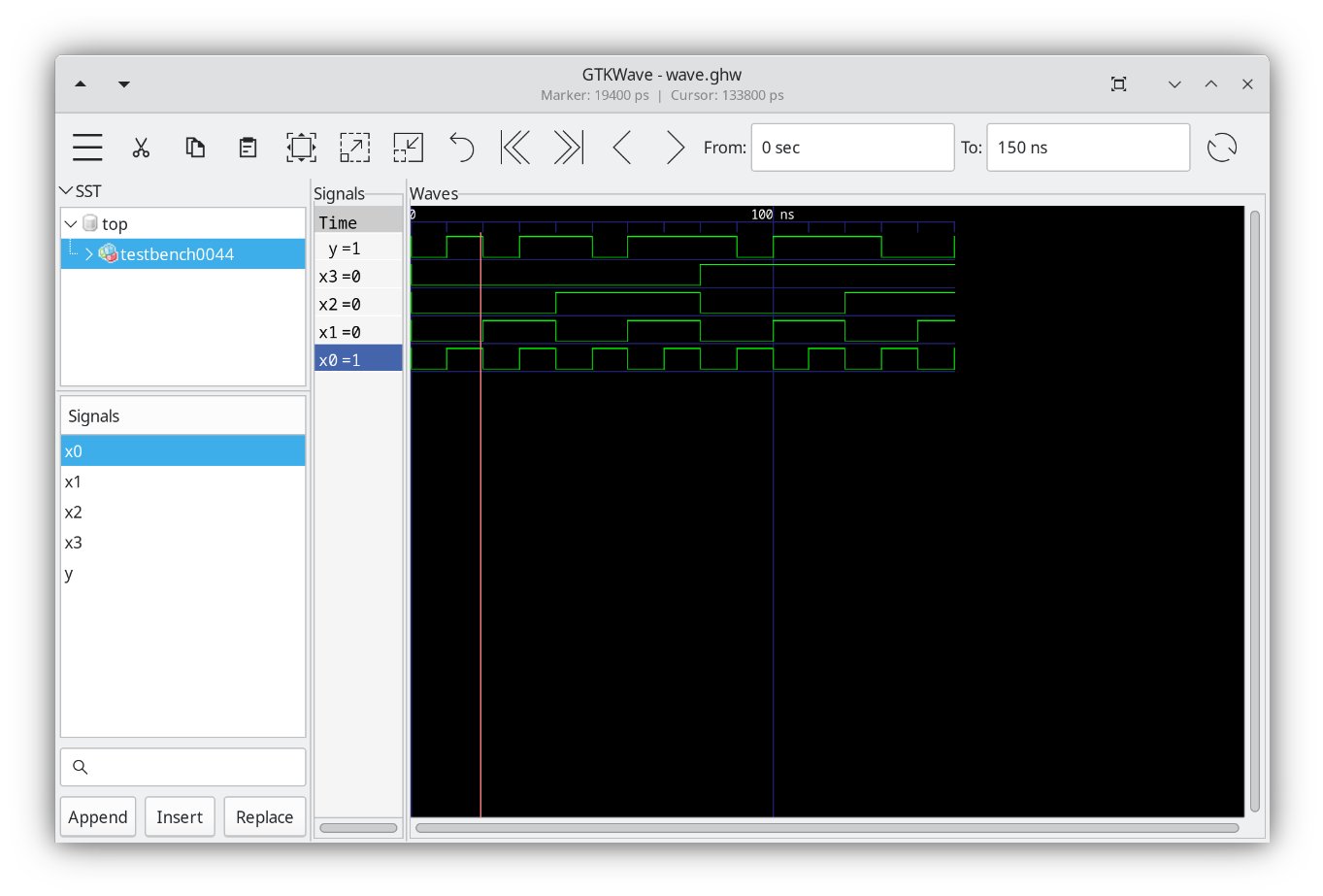

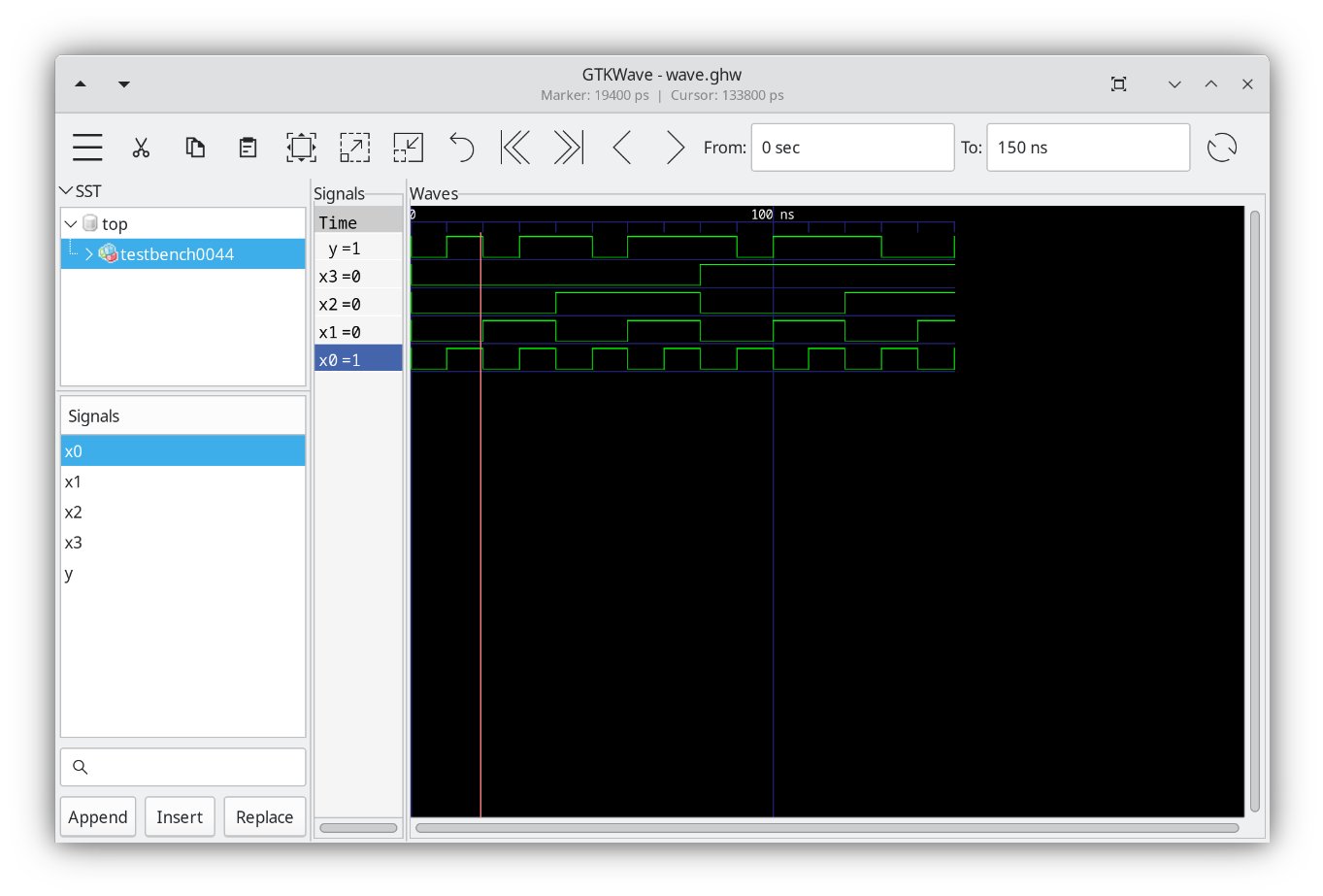

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz044 is

port

(

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz044 is

begin

y <= (x1 and x0) or

(x2 and not x1 and not x0) or

(not x3 and not x2 and x0) or

(not x3 and x2 and not x0) or

(x3 and not x2 and not x0);

end;

library ieee;

use ieee.std_loc_1164.all;

entity testbench0044 is

port

(

y: out std_logic

);

end;

architecture verhalten of testbench0044 is

component meinschaltnetz044

port

(

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

signal x3, x2, x1, x0: std_logic;

begin

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;