Nächste Seite: Re: Aufgaben und Übungen, Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: Aufgaben und Übungen,

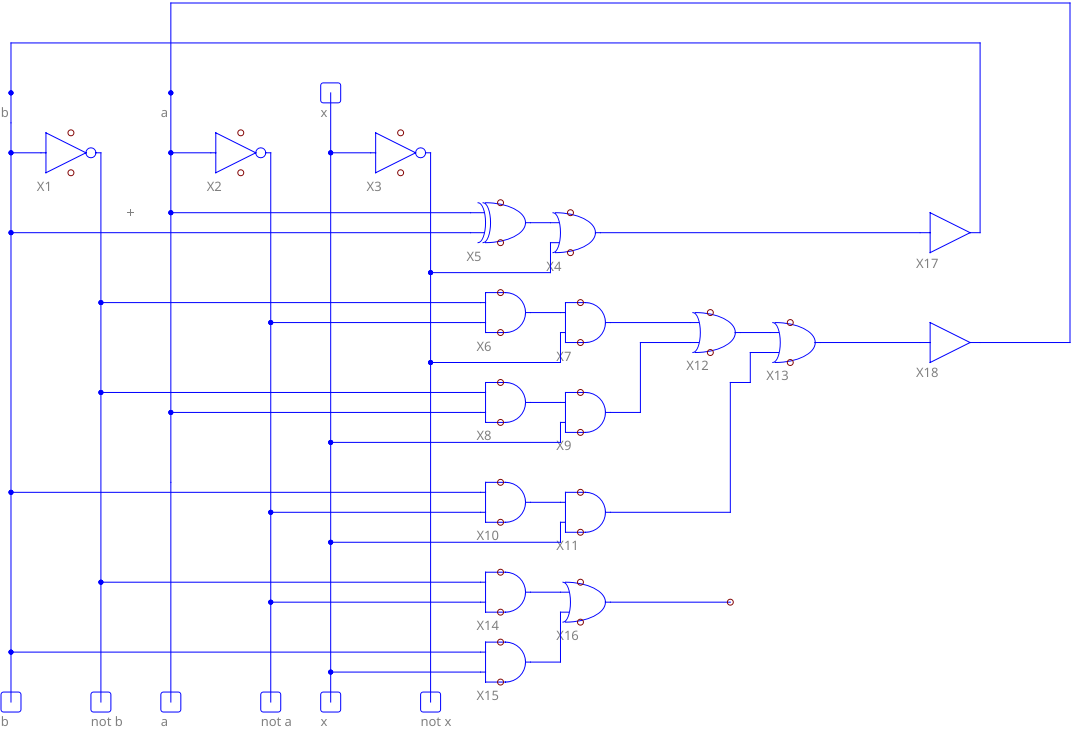

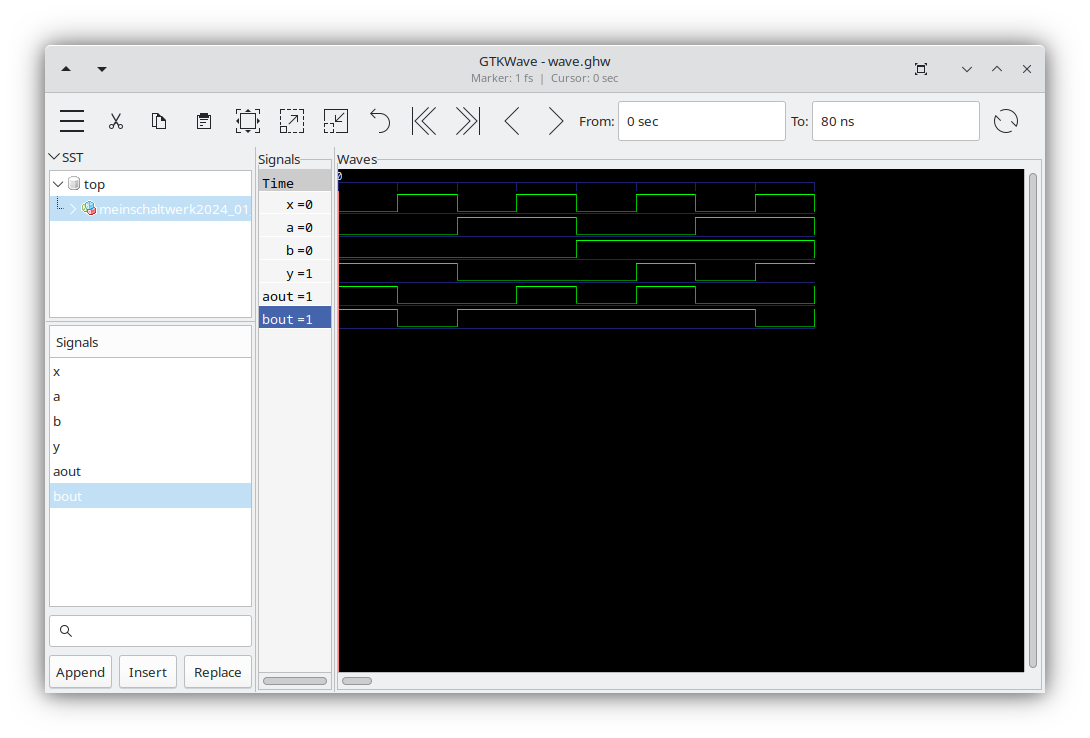

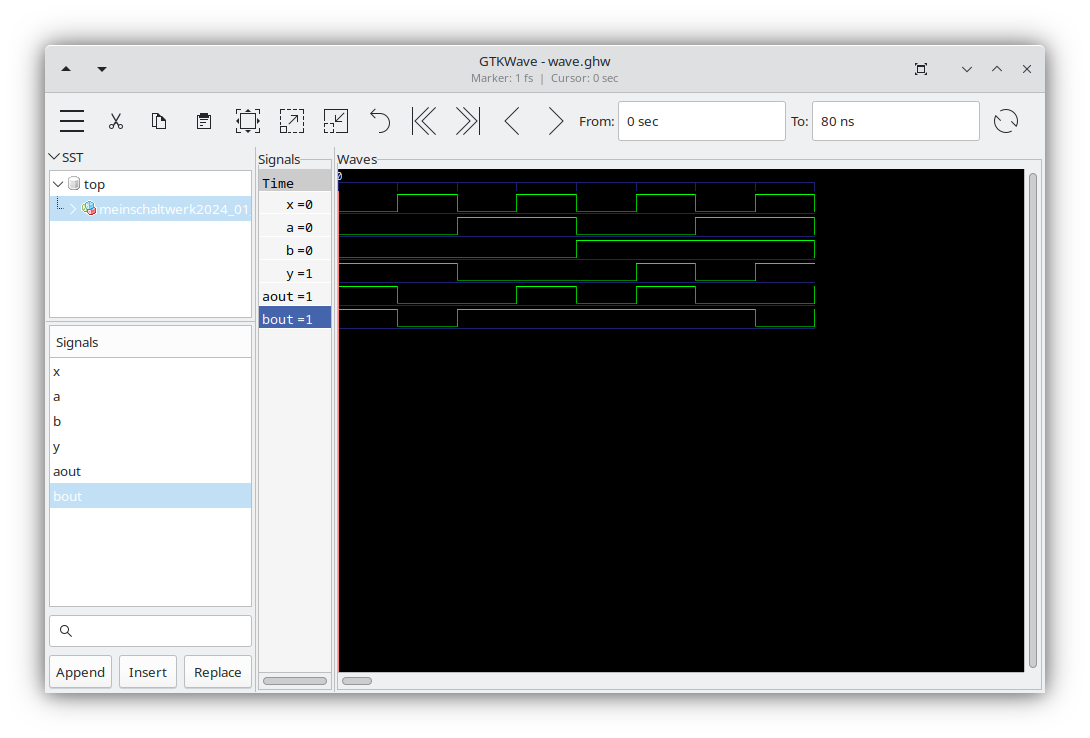

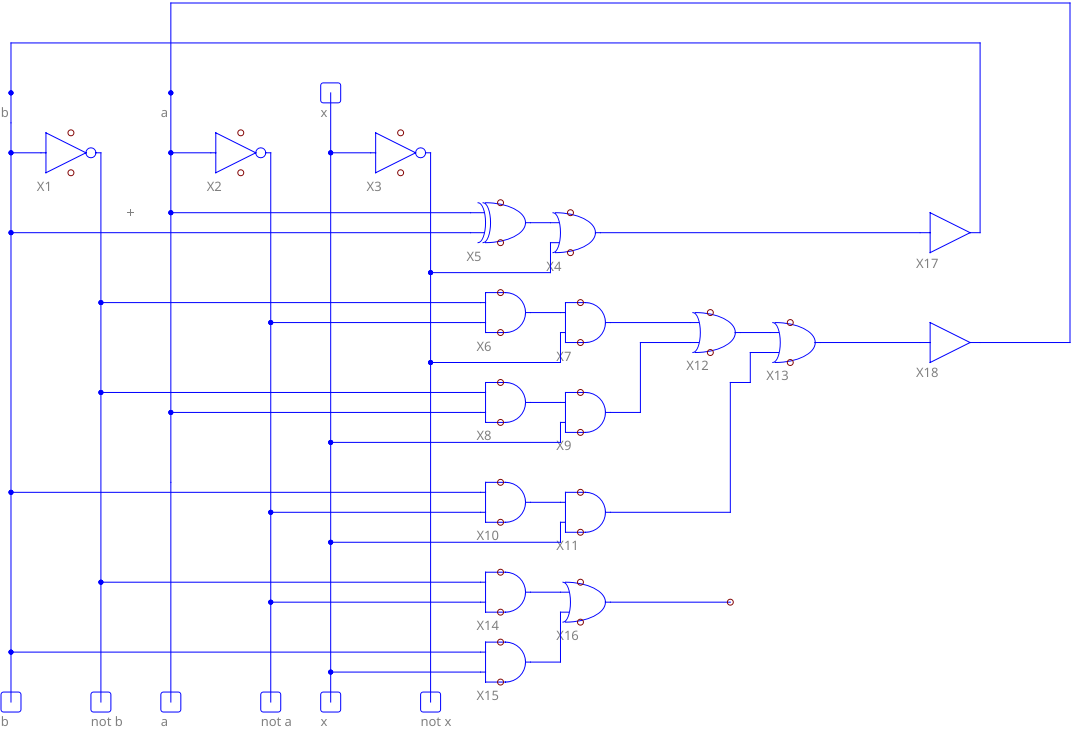

b a x b a y 0 0 0 0 1 1 1 1 0 0 1 0 0 1 2 0 1 0 1 0 0 3 0 1 1 1 1 0 4 1 0 0 1 0 0 5 1 0 1 1 1 1 6 1 1 0 1 0 0 7 1 1 1 0 0 1 b a x b 0 0 0 0 1 1 0 0 1 0 2 0 1 0 1 3 0 1 1 1 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 7 1 1 1 0 b a x a 0 0 0 0 1 1 0 0 1 0 2 0 1 0 0 3 0 1 1 1 4 1 0 0 0 5 1 0 1 1 6 1 1 0 0 7 1 1 1 0 b a x y 0 0 0 0 1 1 0 0 1 1 2 0 1 0 0 3 0 1 1 0 4 1 0 0 0 5 1 0 1 1 6 1 1 0 0 7 1 1 1 1 b a x b 0 0 0 0 1 2 0 1 0 1 3 0 1 1 1 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 b a x a 0 0 0 0 1 3 0 1 1 1 5 1 0 1 1 b a x y 0 0 0 0 1 1 0 0 1 1 5 1 0 1 1 7 1 1 1 1 b a x b Gruppe 0: 0 0 0 0 1 Gruppe 1: 2 0 1 0 1 4 1 0 0 1 Gruppe 2: 3 0 1 1 1 5 1 0 1 1 6 1 1 0 1 b a x a Gruppe 0: 0 0 0 0 1 Gruppe 2: 3 0 1 1 1 5 1 0 1 1 b a x y Gruppe 0: 0 0 0 0 1 Gruppe 1: 1 0 0 1 1 Gruppe 2: 5 1 0 1 1 Gruppe 3: 7 1 1 1 1 b a x b Gruppe 0: 0 0 0 0 1 Gruppe 1: 2 0 1 0 1 4 1 0 0 1 Gruppe 2: 3 0 1 1 1 5 1 0 1 1 6 1 1 0 1 0:2 0 - 0 0:4 - 0 0 2:3 0 1 - 2:6 - 1 0 4:5 1 0 - 4:6 1 - 0 0:2 0 - 0 4:6 1 - 0 0:2:4:6 - - 0 0:4 - 0 0 2:6 - 1 0 0:4:2:6 - - 0 2:3 0 1 - 4:5 1 0 - b <= (not x) or (b xor a); b a x a Gruppe 0: 0 0 0 0 1 Gruppe 2: 3 0 1 1 1 5 1 0 1 1 a <= (not b and not a and not x) or (not b and a and x) or (b and not a and x); a <= not ( (b or a or x) and (b or not a or not x) and (not b or a or not x); ); b a x y Gruppe 0: 0 0 0 0 1 Gruppe 1: 1 0 0 1 1 Gruppe 2: 5 1 0 1 1 Gruppe 3: 7 1 1 1 1 0:1 0 0 - 1:5 - 0 1 5:7 1 - 1 0 1 5 7 0:1 * * 1:5 * * 5:7 * * 0 1 5 7 0:1 * * 5:7 * * y <= (not b and not a) or (b and x); y <= not ( (b or a) and (not b or not x) ); bout <= (not x) or (b xor a); aout <= (not b and not a and not x) or (not b and a and x) or (b and not a and x); y <= (not b and not a) or (b and x); library ieee; use ieee.std_logic_1164.all; entity meinschaltwerk2024_01_01uebergangsschaltnetz is port ( b, a, x: in std_logic; bout, aout: out std_logic ); end; architecture verhalten of meinschaltwerk2024_01_01uebergangsschaltnetz is begin bout <= (not x) or (b xor a); aout <= (not b and not a and not x) or (not b and a and x) or (b and not a and x); end; library ieee; use ieee.std_logic_1164.all; entity meinschaltwerk2024_01_01ausgangsschaltnetz is port ( b, a, x: in std_logic; y: out std_logic ); end; architecture verhalten of meinschaltwerk2024_01_01ausgangsschaltnetz is begin y <= (not b and not a) or (b and x); end; library ieee; use ieee.std_logic_1164.all; entity meinschaltwerk2024_01_01testbench is port ( bout, aout: out std_logic; y: out std_logic ); end; architecture verhalten of meinschaltwerk2024_01_01testbench is component meinschaltwerk2024_01_01uebergangsschaltnetz port ( b, a, x: in std_logic; bout, aout: out std_logic ); end component; component meinschaltwerk2024_01_01ausgangsschaltnetz port ( b, a, x: in std_logic; y: out std_logic ); end component; signal b, a, x: std_logic; begin sn1: meinschaltwerk2024_01_01uebergangsschaltnetz PORT MAP (b=>b, a=>a, x=>x, bout=>bout, aout=>aout); sn2: meinschaltwerk2024_01_01ausgangsschaltnetz PORT MAP (b=>b, a=>a, x=>x, y=>y); x <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns; a <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns; b <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns; end;

library ieee; use ieee.std_logic_1164.all; entity meinschaltwerk2024_01_01uebergangsschaltnetz is port ( b, a, x: in std_logic; bout, aout: out std_logic ); end; architecture verhalten of meinschaltwerk2024_01_01uebergangsschaltnetz is begin bout <= (not x) or (b xor a); aout <= (not b and not a and not x) or (not b and a and x) or (b and not a and x); end; library ieee; use ieee.std_logic_1164.all; entity meinschaltwerk2024_01_01ausgangsschaltnetz is port ( b, a, x: in std_logic; y: out std_logic ); end; architecture verhalten of meinschaltwerk2024_01_01ausgangsschaltnetz is begin y <= (not b and not a) or (b and x); end; library ieee; use ieee.std_logic_1164.all; entity meinschaltwerk2024_01_01testbench is port ( bout, aout: out std_logic; y: out std_logic ); end; architecture verhalten of meinschaltwerk2024_01_01testbench is component meinschaltwerk2024_01_01uebergangsschaltnetz port ( b, a, x: in std_logic; bout, aout: out std_logic ); end component; component meinschaltwerk2024_01_01ausgangsschaltnetz port ( b, a, x: in std_logic; y: out std_logic ); end component; signal b, a, x: std_logic; begin sn1: meinschaltwerk2024_01_01uebergangsschaltnetz PORT MAP (b=>b, a=>a, x=>x, bout=>bout, aout=>aout); sn2: meinschaltwerk2024_01_01ausgangsschaltnetz PORT MAP (b=>b, a=>a, x=>x, y=>y); x <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns; a <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns; b <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns; end;

b a x b a y 0 0 0 0 1 1 1 1 0 0 1 0 0 1 2 0 1 0 1 0 0 3 0 1 1 1 1 0 4 1 0 0 1 0 0 5 1 0 1 1 1 1 6 1 1 0 1 0 0 7 1 1 1 0 0 1

So, sieht es bisher aus, ich glaube die Tabelle kommt hier nicht richtig raus, aber auf meiner Homepages

Die Ausgabe - Status-Signal (das sind nicht die Register R0, R1, R2 - wir sind im Schaltwerk)

ist die Abfrage, PC < R0

Die Abfrage PC < 5

Aber doch ein wenig die Register

Ausgabe:

Enable PC, R0, R1, R2

PC < R0 ist Eingabe f"ur das Steuerwerk

PC < 5 ist Eingabe f"ur das Steuwerk

Enable PC, R0, R1, R2 ist Ausgbae f"ur das Steuerwerk

Und man braucht noch was man da rein schreibt, das heisst, Multiplexer, das muss man kodieren

Also

R0:

1.) In Z0: R0(7:0) <- X(15:8)

R1:

1.) In R1(15:0) wir X(31:16) geschrieben

3.) R1 <- R1+M[PC]

4.) R1 <- R1+2

In PC

1.) Z0: PC(7:0) <- X(7:0)

2.) Z1, Z6: PC <- PC+1

3.) Z4, PC <- 0

Wir haben also Zwei Multiplexer

F"ur PC einen und f"ur R1 einen.

Sie haben zwischen 3 und 3 M"oglichkeiten brauchen als 2 Bit jeweils, insgesamt 4 Bit

Das macht einen Steuervektor von 4 Bit

Dieser heisst

S(3:0)

S3, S2, S1, S0

S3, S2: F"ur PC

S1, S0: F"ur R1

Aber wir brauchen Enable, deswegen sind es drei Bits, pro Register, als 2 Bit mehr

S(5:0)

Das Most Significant Bit ist das Enable des jeweiligen Registers

Wir haben den Statusvektor V(1:0)

V1 und V0, stehen f"ur:

PC < R0

und

PC < 5

Aktueller Zustand Eingabe - Status Signal Ausgabe - Status Signal Folgezustand Code-Folgezustand

0 00 100100 1

0 01 100100 1

0 10 100100 1

0 11 100100 1

1 00 0xx0xx

1 01 0xx0xx

1 10 0xx0xx

1 11 0xx0xx

2 00 101101

2 01 101101

2 10 101101

2 11 101101

3 00 1100xx

3 01 1100xx

3 10 1100xx

3 11 1100xx

4 00 0xx0xx

4 01 0xx0xx

4 10 0xx0xx

4 11 0xx0xx

5 00 101110

5 01 101110

5 10 101110

5 11 101110

6 00 0xx0xx

6 01 0xx0xx

6 10 0xx0xx

6 11 0xx0xx

So, ist es richtig, jetzt mache ich die Tabelle f"ur Facebook

Die Ausgabe - Status-Signal (das sind nicht die Register R0, R1, R2 - wir sind im Schaltwerk)

ist die Abfrage, PC < R0

Die Abfrage PC < 5

Aber doch ein wenig die Register

Ausgabe:

Enable PC, R0, R1, R2

PC < R0 ist Eingabe f"ur das Steuerwerk

PC < 5 ist Eingabe f"ur das Steuwerk

Enable PC, R0, R1, R2 ist Ausgbae f"ur das Steuerwerk

Und man braucht noch was man da rein schreibt, das heisst, Multiplexer, das muss man kodieren

Also

R0:

1.) In Z0: R0(7:0) <- X(15:8)

R1:

1.) In R1(15:0) wir X(31:16) geschrieben

3.) R1 <- R1+M[PC]

4.) R1 <- R1+2

In PC

1.) Z0: PC(7:0) <- X(7:0)

2.) Z1, Z6: PC <- PC+1

3.) Z4, PC <- 0

Wir haben also Zwei Multiplexer

F"ur PC einen und f"ur R1 einen.

Sie haben zwischen 3 und 3 M"oglichkeiten brauchen als 2 Bit jeweils, insgesamt 4 Bit

Das macht einen Steuervektor von 4 Bit

Dieser heisst

S(3:0)

S3, S2, S1, S0

S3, S2: F"ur PC

S1, S0: F"ur R1

Aber wir brauchen Enable, deswegen sind es drei Bits, pro Register, als 2 Bit mehr

S(5:0)

Das Most Significant Bit ist das Enable des jeweiligen Registers

Wir haben den Statusvektor V(1:0)

V1 und V0, stehen f"ur:

PC < R0

und

PC < 5

Aktueller Zustand Eingabe - Status Signal Ausgabe - Status Signal Folgezustand Code-Folgezustand

0 00 100100 1 000001

0 01 100100 1 000001

0 10 100100 1 000001

0 11 100100 1 000001

1 00 0xx0xx 3 000100

1 01 0xx0xx 3 000100

1 10 0xx0xx 2 000010

1 11 0xx0xx 2 000010

2 00 101101 1 000001

2 01 101101 1 000001

2 10 101101 1 000001

2 11 101101 1 000001

3 00 1100xx 4 001000

3 01 1100xx 4 001000

3 10 1100xx 4 001000

3 11 1100xx 4 001000

4 00 0xx0xx 6 100000

4 01 0xx0xx 5 010000

4 10 0xx0xx 6 100000

4 11 0xx0xx 5 010000

5 00 101110 4 001000

5 01 101110 4 001000

5 10 101110 4 001000

5 11 101110 4 001000

6 00 0xx0xx 6 100000

6 01 0xx0xx 6 100000

6 10 0xx0xx 6 100000

6 11 0xx0xx 6 100000

A B C D E

0 00 100100 1 000001

0 01 100100 1 000001

0 10 100100 1 000001

0 11 100100 1 000001

1 00 0xx0xx 3 000100

1 01 0xx0xx 3 000100

1 10 0xx0xx 2 000010

1 11 0xx0xx 2 000010

2 00 101101 1 000001

2 01 101101 1 000001

2 10 101101 1 000001

2 11 101101 1 000001

3 00 1100xx 4 001000

3 01 1100xx 4 001000

3 10 1100xx 4 001000

3 11 1100xx 4 001000

4 00 0xx0xx 6 100000

4 01 0xx0xx 5 010000

4 10 0xx0xx 6 100000

4 11 0xx0xx 5 010000

5 00 101110 4 001000

5 01 101110 4 001000

5 10 101110 4 001000

5 11 101110 4 001000

6 00 0xx0xx 6 100000

6 01 0xx0xx 6 100000

6 10 0xx0xx 6 100000

6 11 0xx0xx 6 100000

Aktueller Zustand: A

Eingabe - Status Signal: B

Ausgabe - Status Signal: C

Folgezustand: D

Code-Folgezustand: E

Jetzt kann ich damit beginnen, unnötigen Einträge in der Tabelle zu vermeiden. Wenn ein Zustand, keine Eingabe hat, davon unabhängig ist, unweigerlich ein Zustand folgt, kann von der Eingabe ins Steuwerk bei der Eingabe xx stehen und der Zustand ist in jedem Fall der Zustand, der folgt.

A B C D E

0 xx 100100 1 000001

1 0x 0xx0xx 3 000100

1 1x 0xx0xx 2 000010

2 xx 101101 1 000001

3 xx 1100xx 4 001000

4 x0 0xx0xx 6 100000

4 x1 0xx0xx 5 010000

5 xx 101110 4 001000

6 xx 0xx0xx 6 100000

Aktueller Zustand: A

Eingabe - Status Signal: B

Ausgabe - Status Signal: C

Folgezustand: D

Code-Folgezustand: E

Die Einträge in der letzten Spalte heissen eigentlich

z7+, z6+, z5+

A B C D E

0 xx 100100 1 000001

1 0x 0xx0xx 3 000100

1 1x 0xx0xx 2 000010

2 xx 101101 1 000001

3 xx 1100xx 4 001000

4 x0 0xx0xx 6 100000

4 x1 0xx0xx 5 010000

5 xx 101110 4 001000

6 xx 0xx0xx 6 100000

=

z1 = z0+ z2 = z1+ AND v1 z3 = z1+ AND NOT v1 z4 = z3+ OR z5+ z5 = z4+ AND v0 z6 = (z4+ AND NOT v0) OR (z6+)Wir haben

wird n"amlich erst durch den Addierer gejagt.\\

A B C D E\\

0 xx 100100 1 000001\\

1 0x 0xx0xx 3 000100\\

1 1x 0xx0xx 2 000010\\

2 xx 101101 1 000001\\

3 xx 1100xx 4 001000\\

4 x0 0xx0xx 6 100000\\

4 x1 0xx0xx 5 010000\\

5 xx 101110 4 001000\\

6 xx 0xx0xx 6 100000\\

\\

\\

Aktueller Zustand: A\\

Eingabe - Status Signal: B\\

Ausgabe - Status Signal: C\\

Folgezustand: D\\

Code-Folgezustand: E\\

\begin{verbatim}

z1+ = z0

z2+ = z1 AND v1

z3+ = z1 AND NOT v1

z4+ = z3 OR z5

z5+ = z4 AND v0

z6+ = (z4 AND NOT v0) OR (z6)

s5 = z0

A B C D E

0 xx 100100 1 000001

1 0x 0xx0xx 3 000100

1 1x 0xx0xx 2 000010

2 xx 101101 1 000001

3 xx 1100xx 4 001000

4 x0 0xx0xx 6 100000

4 x1 0xx0xx 5 010000

5 xx 101110 4 001000

6 xx 0xx0xx 6 100000

Aktueller Zustand: A

Eingabe - Status Signal: B

Ausgabe - Status Signal: C

Folgezustand: D

Code-Folgezustand: E

z1+ = z0 z2+ = z1 AND v1 z3+ = z1 AND NOT v1 z4+ = z3 OR z5 z5+ = z4 AND v0 z6+ = (z4 AND NOT v0) OR (z6) s5 = z0 OR z2 OR z3 OR z5 s4 = z3 s3 = z2 OR z5 s2 = z0 OR s2 OR s5 s1 = s5 s0 = z5