Nächste Seite: Re: Aufgaben und Übungen, Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: Aufgaben und Übungen,

32x32 Registersatz

2 Lese und 1 Schreibport

5 Bit Addresse

2\^5 = 32

32 Bit Bus

5 Bit Bus

r-typ

rs-Feld: Quelloperand

rt-Feld: Quelloperand

rd-Feld: Zieloperand

r-typ

i-typ

j-typ

ALU-Op

Opcode:

00 - add

01 - sub

10 - nutze das Func Feld

11 - n/a

Func-Feld:

100 000 - add 4 0

100 010 - sub 4 2

100 100 - and 4 4

100 101 - or 4 5

101 010 - slt - set less than 5 2

ALU-Operation

010 - add

110 - sub

000 - and

001 - or

111 - slt set less than

Einzyklus

Mehrzyklus

Pipelining

Datenkonflikt

Steuerflusskonflikt

Struktur und Ressourcen Konflikt

Echte Datenabh"angigkeit: ED - RAW - Read after Write

Ausgabeabh"angigkeit: AA - WAR - Write after Read

Gegenabh"angigkeit: GA - WAW - Write after Write

Schaltnetz: Elektrische Schaltung, die Spannung als logische Variablen 0 und 1 interpretieren

Schaltnetz: DIN44300/93

Schaltunktion: DIN44300/87

Eingangsvektor

Schaltnetz

Ausgangsvektor

Eingangsvariablen: x0, x1, ..., xn

Eingangsvektor

Schaltalgebra/Boolesche Algebra

Schaltzeichen

Schaltfunktion

Wahrheitstabelle

Funktionsgleichung

Bin"ares Entscheidungsdiagramm

KV-Diagramm

Schaltplan

Gesetze:

Neutrales Element

Inverses Element

Dualit"atsprinzip

De Morgansche Gleichungen oder Regeln

Assoziativ

Distributiv

Kommutativ

Absorbition

Verkn"upfung

Null

Eins

AND (Konjunktion)

OR (Disjunktion)

NAND

NOR

"Aquivalenz

Antivalenz

Komplement

Inverse

Implikation

Transfer

Codierer: Zurordnung eines Zeichen eines Zeichenvorrats zu derjenigen eines anderen Zeichenvorrats

Dekodierer: Codierer mit mehreren Ein und Ausg"angen, die f"ur jede Kombination von Eingangssignalen immer nur

je ein Ausgang ein Signal abgibt

Codierer: DIN44300/118

Dekoderier: DIN44300/121

Verkn"upfungsglieder: DIN40700

Rechenelemente, Komperatoren: DIN40700

PLHS 18P8

Minimierung von Schaltfunktion

Bin"ar"aquivalente

Primimplikantentafel

Quine Mc Cluskey

....

Volladdierer

S = A XOR B XOR C

U = (A AND B) OR (A OR B) AND C

Befehlsz"ahler

Eingang: PC (t)

Ausgang: PC (t+1)

Befehlsdekodierer:

Eingang: OpCode

Ausgang:

MemToReg

MemWrite

Branch

ALU-Src

RegDst

RegWrite

Ausgang: ALU-Op

Funktionsdekodierer:

Eingang:

Func

ALU-Op

Ausgang:

ALU-Operation

Befehlsdekodierer + 32 Bit Befehlswort: Bit 31 bis Bit 26

Func: Bit 5 bis Bit 0

rs-Feld: 26-21

rt-Feld: 20-16

Immidiate Werte - I-Typ Befehle: Bit 0 bis bit 15 (16 Bit) -> Vorzeichenerweiterungseinheit

1.) Befehlsz"ahler PC (t)

2.) Befehlsspeicher

3.) Vorzeichenerweiterungseinheit

4.) 2 Bit Shifter

5.) Addierer

6.) DeMUX

7.) PC (t+1)

1.) Befehsz"ahler PC (t)

2.) Befehlsspeicher

3.) Befehlsz"ahler PC (t+1)

Addierer: +4

PC (t) -> Addierer + 4 -> PC (t+1)

I1: WB

I2: MEM

I3: EX

I4: ID

I5: IF

addi \$t1, \$t2, 2

add \$t4, \$t1, \$t3

subi \$t3, \$t5, 3

subi \$t3, \$t6, 3

Einzyklus

I1: 0, IF, 1, ID, 2, EX, 3 MEM, 4 WB

I2: 5, IF, 6, ID, 7, EX, 8, MEM, 9 WB

Mehryzyklus Pipelining

I1: 0, IF, 1, ID, 2, EX, 3, MEM, 4 WB

I2: 0 - NIX, 1, IF, 2 ID, 3 EX 4 MEM, 5 WB

I1 schreibt in WB

I2 liesst in ID

Interlocking, Stalling

IF ID EX MEM WB

ID ID EX MEM WB

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 0

3 0 0 1 1 0

4 0 1 0 0 0

5 0 1 0 1 1

6 0 1 1 0 0

7 0 1 1 1 0

8 1 0 0 0 0

9 1 0 0 1 1

10 1 0 1 0 0

11 1 0 1 1 0

12 1 1 0 0 0

13 1 1 0 1 0

14 1 1 1 0 1

15 1 1 1 1 1

0 0 0 0 0 1

1 0 0 0 1 1

5 0 1 0 1 1

9 1 0 0 1 1

14 1 1 1 0 1

15 1 1 1 1 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

1 0 0 0 1 1

Gruppe 2:

5 0 1 0 1 1

9 1 0 0 1 1

Gruppe 3:

14 1 1 1 0 1

Gruppe 4:

15 1 1 1 1 1

0:1 0 0 0 -

1:5 0 - 0 1

1:9 - 0 0 1

14:15 1 1 1 -

0 1 5 9 14 15

0:1 * *

1:5 * *

1:9 * *

14:15 * *

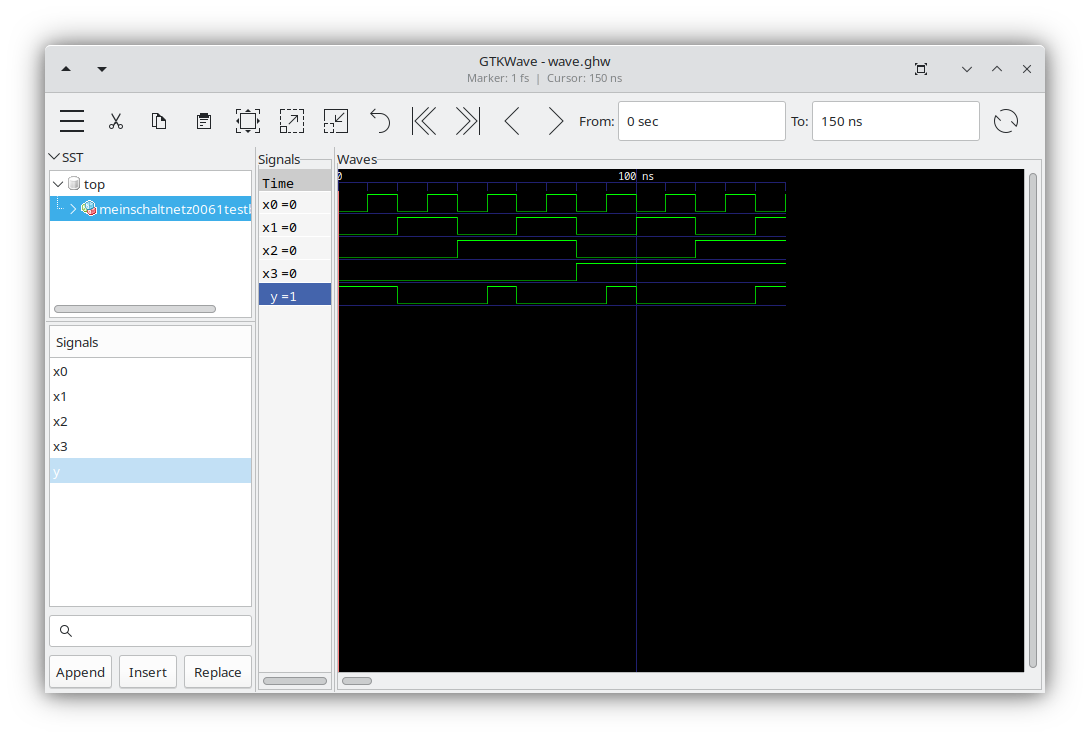

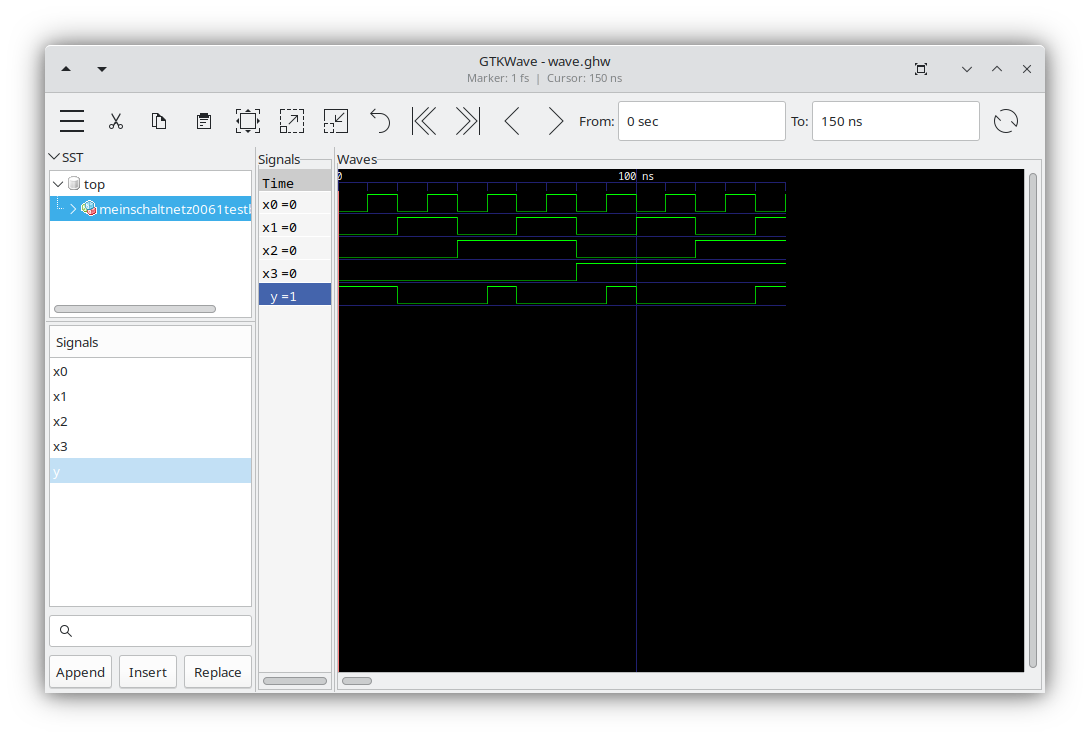

y <= (not x3 and not x2 and not x1) or

(not x3 and not x1 and x0) or

(not x2 and not x1 and x0) or

(x3 and x2 and x1);

y <= not (

(x3 or x2 or x1) and

(x3 or x1 or not x0) and

(x3 or x1 or not x0) and

(not x3 or not x2 or not x1)

);

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz0061 is

port

(

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz0061 is

begin

y <= (not x3 and not x2 and not x1) or

(not x3 and not x1 and x0) or

(not x2 and not x1 and x0) or

(x3 and x2 and x1);

end;

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz0061testbench is

port (

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz0061testbench is

component meinschaltnetz0061

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

sn: meinschaltnetz0061 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz0061 is

port

(

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz0061 is

begin

y <= (not x3 and not x2 and not x1) or

(not x3 and not x1 and x0) or

(not x2 and not x1 and x0) or

(x3 and x2 and x1);

end;

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz0061testbench is

port (

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz0061testbench is

component meinschaltnetz0061

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

sn: meinschaltnetz0061 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;

meinschaltnetz2023_12_31

library ieee;

use ieee.std_logic_1164.all;

entity my_switching_network_happy_new_year is

port

(

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture behaviour of my_switching_network_happy_new_year is

begin

y <= (not x3 and not x2 and not x1) or

(not x3 and not x1 and x0) or

(not x2 and not x1 and x0) or

(x3 and x2 and x1);

end;

library ieee;

use ieee.std_logic_1164.all;

entity my_switching_network_happy_new_year_testbench is

port (

y: out std_logic

);

end;

architecture behaviour of my_switching_network_happy_new_year_testbench is

component my_switching_network_happy_new_year

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

sn: my_switching_network_happy_new_year PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;