Nächste Seite: Re: Aufgaben und Übungen, Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: Aufgaben und Übungen,

-- eine Fussgaengerampel zeigt normalerweise auf rot

-- drueckt man den Knopfl, geht sie auf gruen

-- dort bleibt sie fuer drei Sekunden

-- und geht zurueck auf rot

-- z0+ = z0 AND NOT Knopf OR z2

-- z1+ = z0 AND KNOPF

-- z2+ = z1

-- farbe = z0 AND knopf OR z1 OR z2

library ieee;

use ieee.std_logic_1164.all;

entity ampel20240111 is

port (

farbe: out std_logic;

knopf: in std_logic;

z2p, z1p, z0p: out std_logic;

z2, z1, z0: in std_logic

);

end;

architecture verhalten of ampel20240111 is

begin

z0p <= ((z0 and not knopf) or z2);

z1p <= (z0 and knopf);

z2p <= (z1);

farbe <= (z0 and knopf) or z1 or z2;

end;

-- keine Sorge, ich mache die Schaltung jetzt weiter, ich habe inzwischen andere Aufgaben gemacht

-- eine Fussgaengerampel zeigt normalerweise auf rot

-- drueckt man den Knopfl, geht sie auf gruen

-- dort bleibt sie fuer drei Sekunden

-- und geht zurueck auf rot

-- z0+ = z0 AND NOT Knopf OR z2

-- z1+ = z0 AND KNOPF

-- z2+ = z1

-- farbe = z0 AND knopf OR z1 OR z2

library ieee;

use ieee.std_logic_1164.all;

entity ampel20240111 is

port (

farbe: out std_logic;

knopf: in std_logic;

z2p, z1p, z0p: out std_logic;

z2, z1, z0: in std_logic

);

end;

architecture verhalten of ampel20240111 is

begin

z0p <= ((z0 and not knopf) or z2);

z1p <= (z0 and knopf);

z2p <= (z1);

farbe <= (z0 and knopf) or z1 or z2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20240111 is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch20240111 is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor s);

q2 <= '0' when (init='1') else

(q1 nor r);

q <= q1;

end;

-- da sind wir schon ein St"uck weiter

-- eine Fussgaengerampel zeigt normalerweise auf rot

-- drueckt man den Knopfl, geht sie auf gruen

-- dort bleibt sie fuer drei Sekunden

-- und geht zurueck auf rot

-- z0+ = z0 AND NOT Knopf OR z2

-- z1+ = z0 AND KNOPF

-- z2+ = z1

-- farbe = z0 AND knopf OR z1 OR z2

library ieee;

use ieee.std_logic_1164.all;

entity ampel20240111 is

port (

farbe: out std_logic;

knopf: in std_logic;

z2p, z1p, z0p: out std_logic;

z2, z1, z0: in std_logic

);

end;

architecture verhalten of ampel20240111 is

begin

z0p <= ((z0 and not knopf) or z2);

z1p <= (z0 and knopf);

z2p <= (z1);

farbe <= (z0 and knopf) or z1 or z2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20240111 is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch20240111 is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor s);

q2 <= '0' when (init='1') else

(q1 nor r);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity crslatch20240111 is

port (

r, s: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of crslatch20240111 is

component rslatch20240111

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch: rslatch20240111 PORT MAP (r=>r1, s=>s1, q=>q);

r1 <= r and c;

s1 <= s and c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024011 is

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of dlatch2024011 is

component crslatch20240111

port (

r, s: in std_logic;

q: out std_logic;

c: in std_logic

);

end component;

signal r1, s1: std_logic;

begin

crslatch: crslatch20240111 PORT MAP (r=>r1, s=>s1, c=>c, q=>q);

s1 <= d;

r1 <= not d;

end;

-- das D-Master Slave Flip Flop ist auch schon da

-- eine Fussgaengerampel zeigt normalerweise auf rot

-- drueckt man den Knopfl, geht sie auf gruen

-- dort bleibt sie fuer drei Sekunden

-- und geht zurueck auf rot

-- z0+ = z0 AND NOT Knopf OR z2

-- z1+ = z0 AND KNOPF

-- z2+ = z1

-- farbe = z0 AND knopf OR z1 OR z2

library ieee;

use ieee.std_logic_1164.all;

entity ampel20240111 is

port (

farbe: out std_logic;

knopf: in std_logic;

z2p, z1p, z0p: out std_logic;

z2, z1, z0: in std_logic

);

end;

architecture verhalten of ampel20240111 is

begin

z0p <= ((z0 and not knopf) or z2);

z1p <= (z0 and knopf);

z2p <= (z1);

farbe <= (z0 and knopf) or z1 or z2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20240111 is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch20240111 is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor s);

q2 <= '0' when (init='1') else

(q1 nor r);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity crslatch20240111 is

port (

r, s: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of crslatch20240111 is

component rslatch20240111

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch: rslatch20240111 PORT MAP (r=>r1, s=>s1, q=>q);

r1 <= r and c;

s1 <= s and c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch20240111 is

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of dlatch20240111 is

component crslatch20240111

port (

r, s: in std_logic;

q: out std_logic;

c: in std_logic

);

end component;

signal r1, s1: std_logic;

begin

crslatch: crslatch20240111 PORT MAP (r=>r1, s=>s1, c=>c, q=>q);

s1 <= d;

r1 <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsff20240111 is

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of dmsff20240111 is

component dlatch20240111

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end component;

signal c1, c2: std_logic;

signal qd12: std_logic;

begin

c1 <= c;

c2 <= not c;

master: dlatch20240111 PORT MAP (d=>d, c=>c1, q=>qd12);

slave: dlatch20240111 PORT MAP (d=>qd12, c=>c2, q=>q);

end;

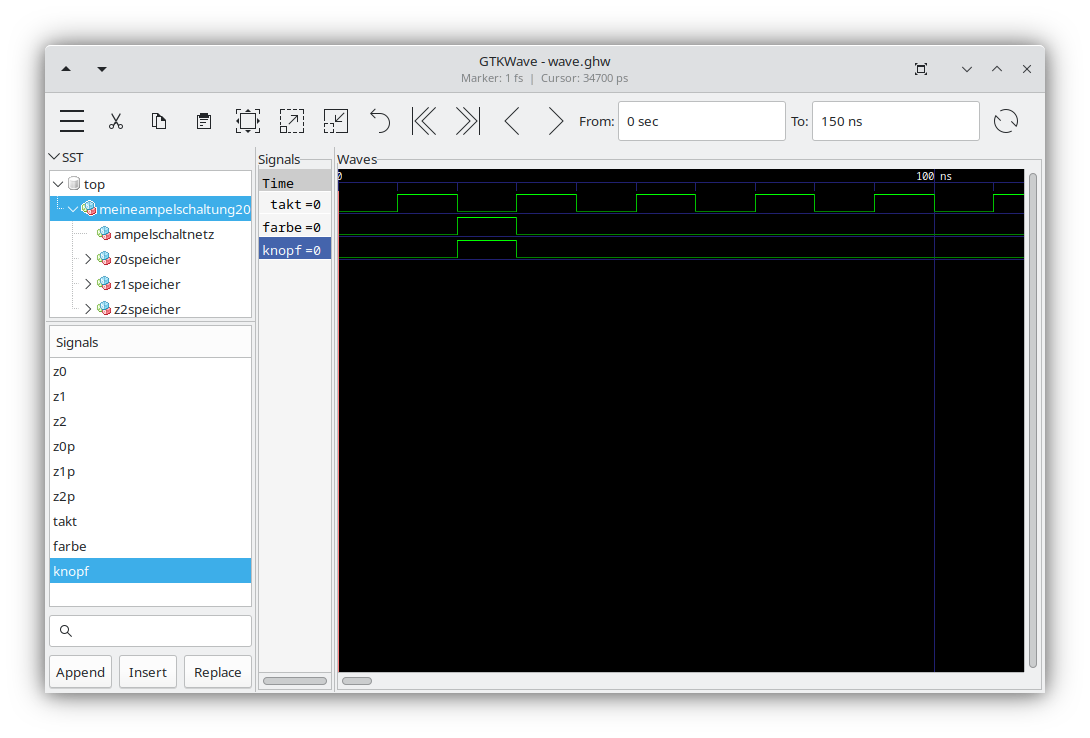

-- na, dann wollen wir es mal probieren, das jetzt das ungetestete schaltnetz, ich f"uhre einen Takt ein und dr"ucke die Taste, mal sehen, was passiert

-- eine Fussgaengerampel zeigt normalerweise auf rot

-- drueckt man den Knopfl, geht sie auf gruen

-- dort bleibt sie fuer drei Sekunden

-- und geht zurueck auf rot

-- z0+ = z0 AND NOT Knopf OR z2

-- z1+ = z0 AND KNOPF

-- z2+ = z1

-- farbe = z0 AND knopf OR z1 OR z2

library ieee;

use ieee.std_logic_1164.all;

entity ampel20240111 is

port (

farbe: out std_logic;

knopf: in std_logic;

z2p, z1p, z0p: out std_logic;

z2, z1, z0: in std_logic

);

end;

architecture verhalten of ampel20240111 is

begin

z0p <= ((z0 and not knopf) or z2);

z1p <= (z0 and knopf);

z2p <= (z1);

farbe <= (z0 and knopf) or z1 or z2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20240111 is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch20240111 is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor s);

q2 <= '0' when (init='1') else

(q1 nor r);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity crslatch20240111 is

port (

r, s: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of crslatch20240111 is

component rslatch20240111

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch: rslatch20240111 PORT MAP (r=>r1, s=>s1, q=>q);

r1 <= r and c;

s1 <= s and c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch20240111 is

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of dlatch20240111 is

component crslatch20240111

port (

r, s: in std_logic;

q: out std_logic;

c: in std_logic

);

end component;

signal r1, s1: std_logic;

begin

crslatch: crslatch20240111 PORT MAP (r=>r1, s=>s1, c=>c, q=>q);

s1 <= d;

r1 <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsff20240111 is

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of dmsff20240111 is

component dlatch20240111

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end component;

signal c1, c2: std_logic;

signal qd12: std_logic;

begin

c1 <= c;

c2 <= not c;

master: dlatch20240111 PORT MAP (d=>d, c=>c1, q=>qd12);

slave: dlatch20240111 PORT MAP (d=>qd12, c=>c2, q=>q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity meineampelschaltung20240111unaercodiert is

port (

knopf: in std_logic;

farbe: out std_logic;

takt: in std_logic

);

end;

architecture verhalten of meineampelschaltung20240111unaercodiert is

component dmsff20240111

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end component;

component ampel20240111

port (

farbe: out std_logic;

knopf: in std_logic;

z2p, z1p, z0p: out std_logic;

z2, z1, z0: in std_logic

);

end component;

signal z2p, z1p, z0p: std_logic;

signal z2, z1, z0: std_logic;

begin

z2speicher: dmsff20240111 PORT MAP (q=>z2p, d=>z2, c=>takt);

z1speicher: dmsff20240111 PORT MAP (q=>z1p, d=>z1, c=>takt);

z0speicher: dmsff20240111 PORT MAP (q=>z0p, d=>z0, c=>takt);

ampelschaltnetz: ampel20240111 PORT MAP (z2p=>z2p, z1p=>z1p, z0p=>z0p, z2=>z2, z1=>z1, z0=>z0, knopf=>knopf, farbe=>farbe);

end;

-- ein kleiner Fehler ist noch drin, den finden wir nach der Raucherpause

-- eine Fussgaengerampel zeigt normalerweise auf rot

-- drueckt man den Knopfl, geht sie auf gruen

-- dort bleibt sie fuer drei Sekunden

-- und geht zurueck auf rot

-- z0+ = z0 AND NOT Knopf OR z2

-- z1+ = z0 AND KNOPF

-- z2+ = z1

-- farbe = z0 AND knopf OR z1 OR z2

library ieee;

use ieee.std_logic_1164.all;

entity ampel20240111 is

port (

farbe: out std_logic;

knopf: in std_logic;

z2p, z1p, z0p: out std_logic;

z2, z1, z0: in std_logic

);

end;

architecture verhalten of ampel20240111 is

begin

z0p <= ((z0 and not knopf) or z2);

z1p <= (z0 and knopf);

z2p <= (z1);

farbe <= (z0 and knopf) or z1 or z2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20240111 is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch20240111 is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor s);

q2 <= '0' when (init='1') else

(q1 nor r);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity crslatch20240111 is

port (

r, s: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of crslatch20240111 is

component rslatch20240111

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch: rslatch20240111 PORT MAP (r=>r1, s=>s1, q=>q);

r1 <= r and c;

s1 <= s and c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch20240111 is

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of dlatch20240111 is

component crslatch20240111

port (

r, s: in std_logic;

q: out std_logic;

c: in std_logic

);

end component;

signal r1, s1: std_logic;

begin

crslatch: crslatch20240111 PORT MAP (r=>r1, s=>s1, c=>c, q=>q);

s1 <= d;

r1 <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsff20240111 is

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end;

architecture verhalten of dmsff20240111 is

component dlatch20240111

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end component;

signal c1, c2: std_logic;

signal qd12: std_logic;

begin

c1 <= c;

c2 <= not c;

master: dlatch20240111 PORT MAP (d=>d, c=>c1, q=>qd12);

slave: dlatch20240111 PORT MAP (d=>qd12, c=>c2, q=>q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity meineampelschaltung20240111unaercodiert is

port (

knopf: inout std_logic;

farbe: out std_logic;

takt: inout std_logic

);

end;

architecture verhalten of meineampelschaltung20240111unaercodiert is

component dmsff20240111

port (

d: in std_logic;

q: out std_logic;

c: in std_logic

);

end component;

component ampel20240111

port (

farbe: out std_logic;

knopf: in std_logic;

z2p, z1p, z0p: out std_logic;

z2, z1, z0: in std_logic

);

end component;

signal z2p, z1p, z0p: std_logic;

signal z2, z1, z0: std_logic;

begin

z2speicher: dmsff20240111 PORT MAP (q=>z2p, d=>z2, c=>takt);

z1speicher: dmsff20240111 PORT MAP (q=>z1p, d=>z1, c=>takt);

z0speicher: dmsff20240111 PORT MAP (q=>z0p, d=>z0, c=>takt);

ampelschaltnetz: ampel20240111 PORT MAP (z2p=>z2p, z1p=>z1p, z0p=>z0p, z2=>z2, z1=>z1, z0=>z0, knopf=>knopf, farbe=>farbe);

z2 <= '0' after 0 ns;

z1 <= '0' after 0 ns;

z0 <= '1' after 0 ns;

takt <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

knopf <= '0' after 0 ns, '1' after 20 ns, '0' after 30 ns;

end;

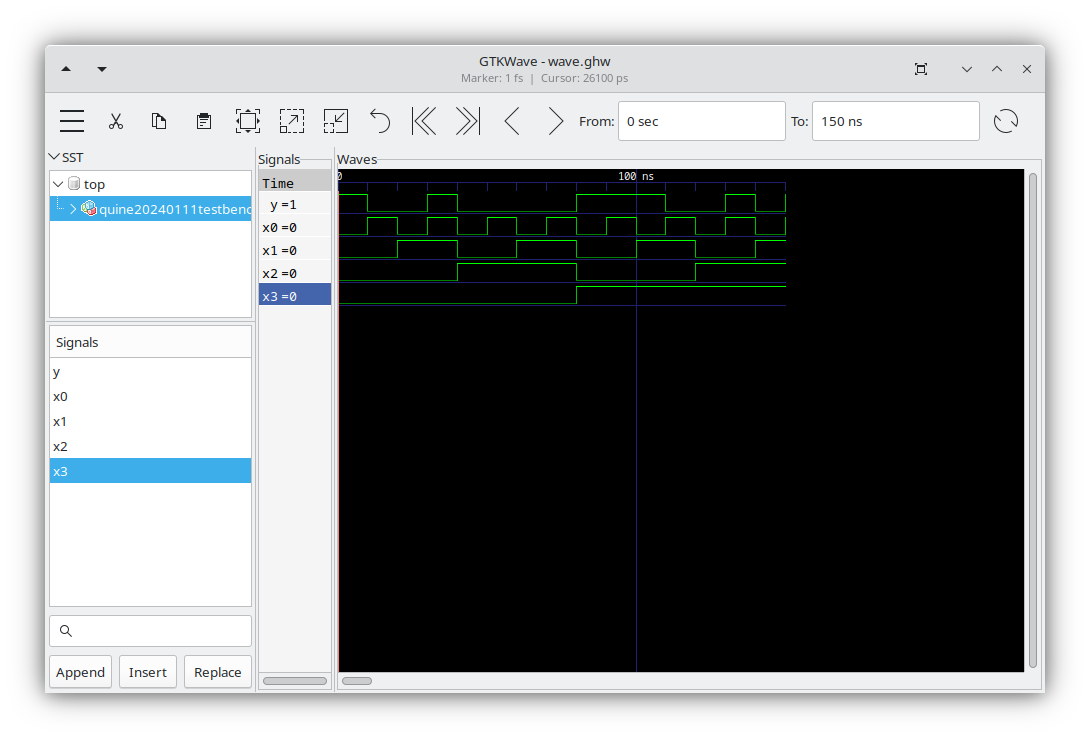

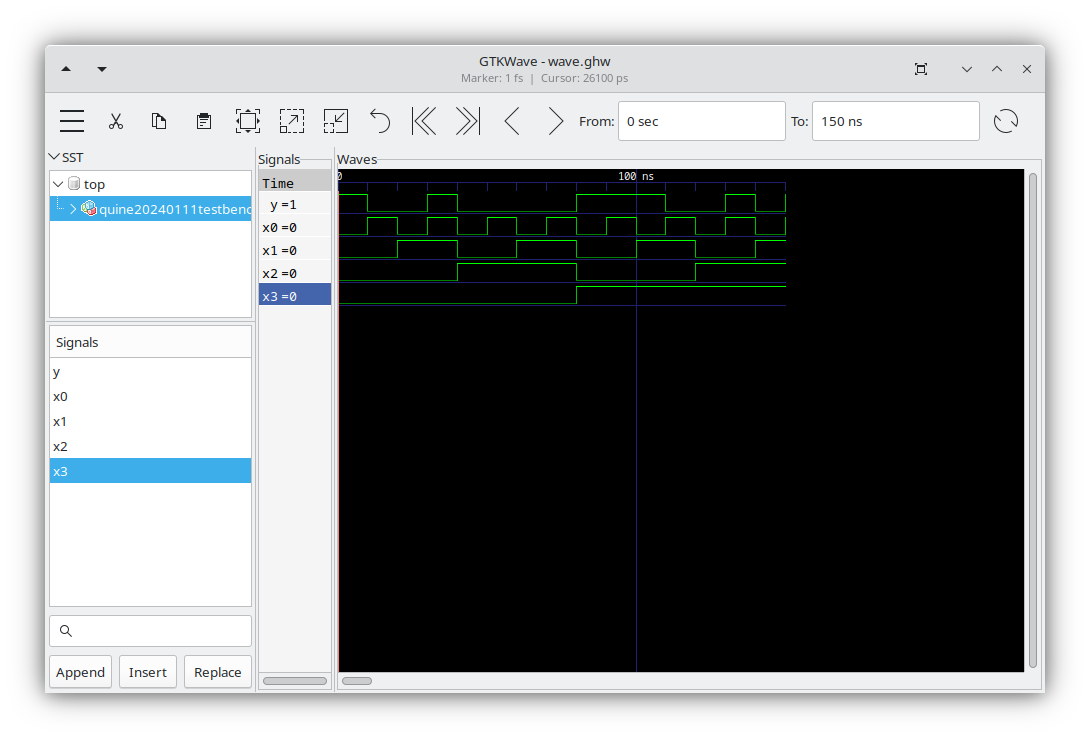

In zwischen machen wir zur Entspannung ein Quine Mc Cluskey auf die alte Art und Weise und ein "Binär CodiertesSSchaltwerk auf die alte Art und Weise. Das werde ich auch weiterhin tun

Allerdings muss ich eine Kurkorrektur anmelden

Schaltwerke sind normalerweise unär Codiert. Das heisst, sie erhalten pro Zustand ein Register

Binärcodierte Schaltwerke unterscheiden sich von unär Codierte nicht. Mit einer Ausnahme. Das Wort wird binär gespeichert. Damit aus dem binären Wort ein unärer Zustand wird, steht vor dem Register ein Encoder und nach dem Register ein Dekodierer

Schaut gut aus

0 0 0 0 0 1

1 0 0 0 1 0

2 0 0 1 0 0

3 0 0 1 1 1

4 0 1 0 0 0

5 0 1 0 1 0

6 0 1 1 0 0

7 0 1 1 1 0

8 1 0 0 0 1

9 1 0 0 1 1

10 1 0 1 0 1

11 1 0 1 1 0

12 1 1 0 0 0

13 1 1 0 1 1

14 1 1 1 0 0

15 1 1 1 1 1

0 0 0 0 0 1

3 0 0 1 1 1

8 1 0 0 0 1

9 1 0 0 1 1

10 1 0 1 0 1

13 1 1 0 1 1

15 1 1 1 1 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

8 1 0 0 0 1

Gruppe 2:

3 0 0 1 1 1

9 1 0 0 1 1

10 1 0 1 0 1

Grupppe 3:

13 1 1 0 1 1

Gruppe 4:

15 1 1 1 1 1

3 0 0 1 1

0:8 - 0 0 0

8:9 1 0 0 -

8:10 1 0 - 0

9:13 1 - 0 1

13:15 1 1 - 1

3 0 0 1 1

8:9 1 0 0 -

8:10 1 0 - 0

13:15 1 1 - 1

9:13 1 - 0 1

0:8 - 0 0 0

0 3 8 9 10 13 15

3 *

8:9 * *

8:10 * *

13:15 * *

9:13 * *

0:8 * *

0 3 8 9 10 13 15

3 *

8:9 * *

8:10 * *

13:15 * *

0:8 * *

3 0 0 1 1

8:9 1 0 0 -

8:10 1 0 - 0

13:15 1 1 - 1

0:8 - 0 0 0

Disjunktive Normalform:

y <= (not x3 and not x2 and x1 and x0) or

(x3 and not x2 and not x1) or

(x3 and not x2 and not x0) or

(x3 and x2 and x0) or

(not x2 and not x1 and not x0);

Konjunktive Normalform:

y <= not (

(x3 or x2 or not x1 or not x0) and

(not x3 or x2 or x1) and

(not x3 or x2 or x0) and

(not x3 or not x2 or not x0) and

(x2 or x1 or x0)

);

library ieee;

use ieee.std_logic_1164.all;

entity quine20240111 is

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture verhalten of quine20240111 is

begin

y <= (not x3 and not x2 and x1 and x0) or

(x3 and not x2 and not x1) or

(x3 and not x2 and not x0) or

(x3 and x2 and x0) or

(not x2 and not x1 and not x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity quine20240111testbench is

port (

x3, x2, x1, x0: inout std_logic;

y: out std_logic

);

end;

architecture verhalten of quine20240111testbench is

component quine20240111

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

begin

quinesn: quine20240111 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity quine20240111 is

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture verhalten of quine20240111 is

begin

y <= (not x3 and not x2 and x1 and x0) or

(x3 and not x2 and not x1) or

(x3 and not x2 and not x0) or

(x3 and x2 and x0) or

(not x2 and not x1 and not x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity quine20240111testbench is

port (

x3, x2, x1, x0: inout std_logic;

y: out std_logic

);

end;

architecture verhalten of quine20240111testbench is

component quine20240111

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

begin

quinesn: quine20240111 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;