Nächste Seite: TTL-Schaltnetz in DNFTTL-Schaltnetz in Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: Aufgaben und Übungen,

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

3 0 0 1 1 0

4 0 1 0 0 0

5 0 1 0 1 0

6 0 1 1 0 1

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 1

10 1 0 1 0 0

11 1 0 1 1 1

12 1 1 0 0 0

13 1 1 0 1 0

14 1 1 1 0 1

15 1 1 1 1 0

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

6 0 1 1 0 1

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 1

11 1 0 1 1 1

14 1 1 1 0 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

1 0 0 0 1 1

2 0 0 1 0 1

8 1 0 0 0 1

Gruppe 2:

6 0 1 1 0 1

9 1 0 0 1 1

Gruppe 3:

7 0 1 1 1 1

11 1 0 1 1 1

14 1 1 1 0 1

0:1 0 0 0 -

0:2 0 0 - 0

0:8 - 0 0 0

1:9 - 0 0 1

2:6 0 - 1 0

8:9 1 0 0 -

6:7 0 1 1 -

6:14 - 1 1 0

9:11 1 0 - 1

8:9 1 0 0 -

6:7 0 1 1 -

0:1 0 0 0 -

9:11 1 0 - 1

0:2 0 0 - 0

2:6 0 - 1 0

0:8 - 0 0 0

1:9 - 0 0 1

6:14 - 1 1 0

Gruppe 0

0:1 0 0 0 -

Gruppe 1:

8:9 1 0 0 -

Gruppe 2:

6:7 0 1 1 -

0:1:8:9 - 0 0 -

6:7 0 1 1 -

Gruppe 0:

0:2 0 0 - 0

Gruppe 2:

9:11 1 0 - 1

2:6 0 - 1 0

Gruppe 0:

0:8 - 0 0 0

Gruppe 1:

1:9 - 0 0 1

Gruppe 2:

6:14 - 1 1 0

0:8:1:9 - 0 0 -

6:14 - 1 1 0

0:1:8:9 - 0 0 -

6:7 0 1 1 -

0:2 0 0 - 0

9:11 1 0 - 1

2:6 0 - 1 0

0:8:1:9 - 0 0 -

6:14 - 1 1 0

0:1:8:9 - 0 0 -

6:7 0 1 1 -

0:2 0 0 - 0

9:11 1 0 - 1

2:6 0 - 1 0

6:14 - 1 1 0

0 1 2 6 7 8 9 11 14

0:1:8:9 * * * *

6:7 * *

0:2 * *

9:11 * *

2:6 * *

6:14 * *

0 1 2 6 7 8 9 11 14

0:1:8:9 * * * *

6:7 * *

0:2 * * +

9:11 * *

2:6 * * +

6:14 * *

0 1 2 6 7 8 9 11 14

0:1:8:9 * * * *

6:7 * *

9:11 * *

2:6 * *

6:14 * *

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

3 0 0 1 1 0

4 0 1 0 0 0

5 0 1 0 1 0

6 0 1 1 0 1

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 1

10 1 0 1 0 0

11 1 0 1 1 1

12 1 1 0 0 0

13 1 1 0 1 0

14 1 1 1 0 1

15 1 1 1 1 0

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

6 0 1 1 0 1

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 1

11 1 0 1 1 1

14 1 1 1 0 1

OK

0 1 2 6 7 8 9 11 14

0:1:8:9 * * * *

6:7 * *

9:11 * *

2:6 * *

6:14 * *

0:1:8:9 - 0 0 -

6:7 0 1 1 -

9:11 1 0 - 1

2:6 0 - 1 0

6:14 - 1 1 0

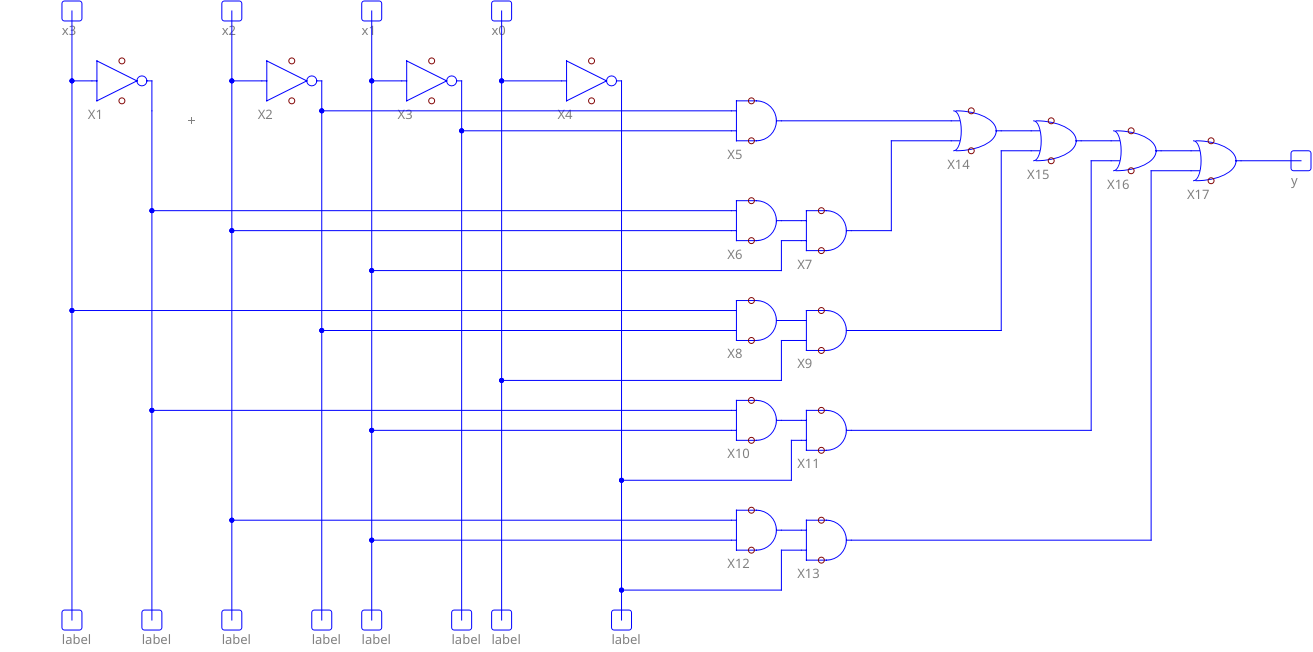

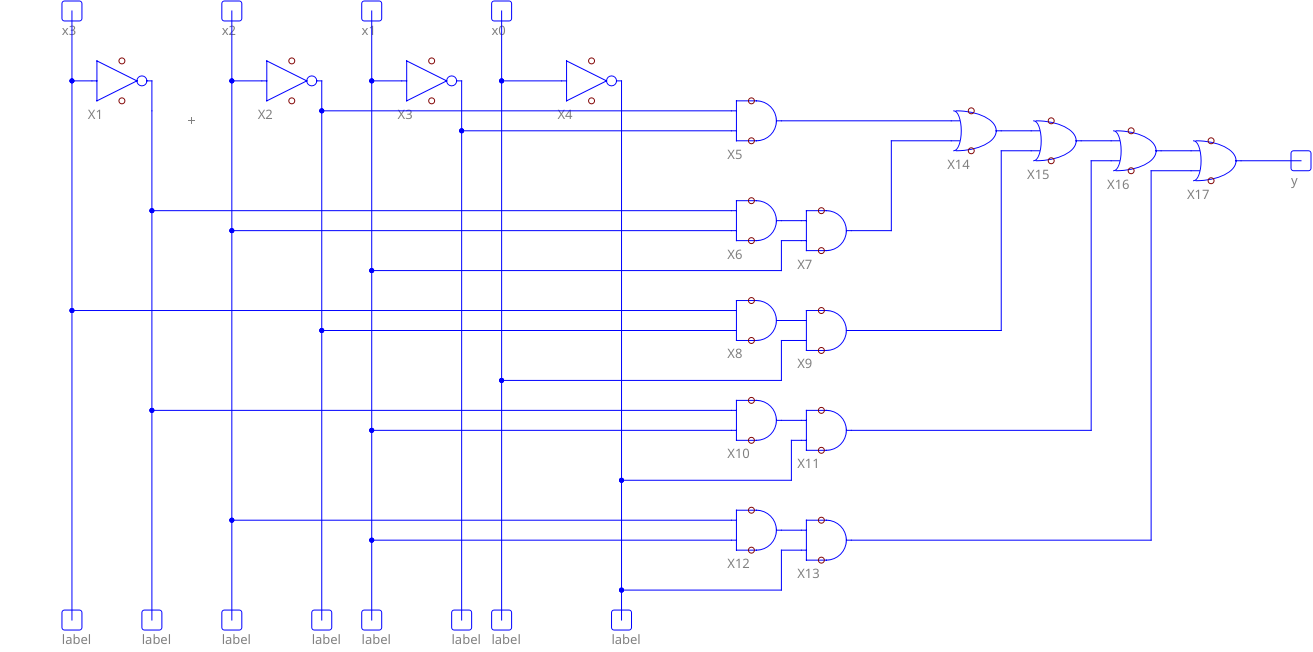

Disjunktive Normalform:

y <= (not x2 and not x1) or

(not x3 and x2 and x1) or

(x3 and not x2 and x0) or

(not x3 and x1 and not x0) or

(x2 and x1 and not x0);

Konjunktive Normalform:

y <= not ((x2 or x1) and

(x3 or not x2 or not x1) and

(not x3 or x2 or not x0) and

(x3 or not x1 or x0) and

(not x2 or not x1 or x0));

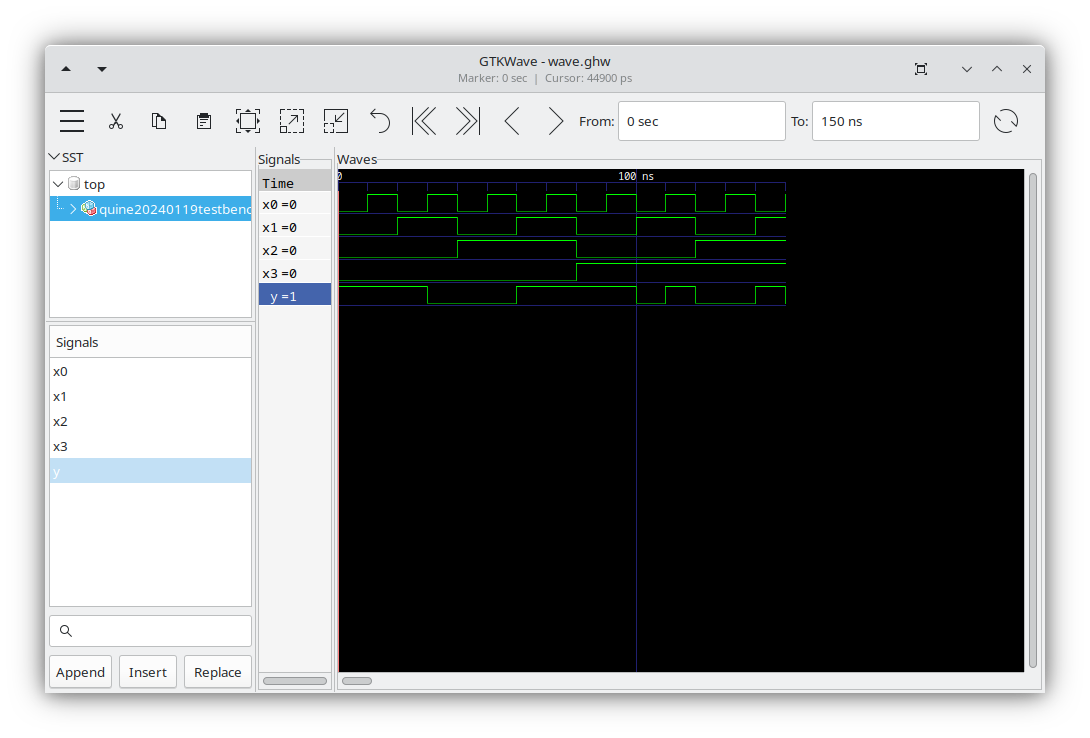

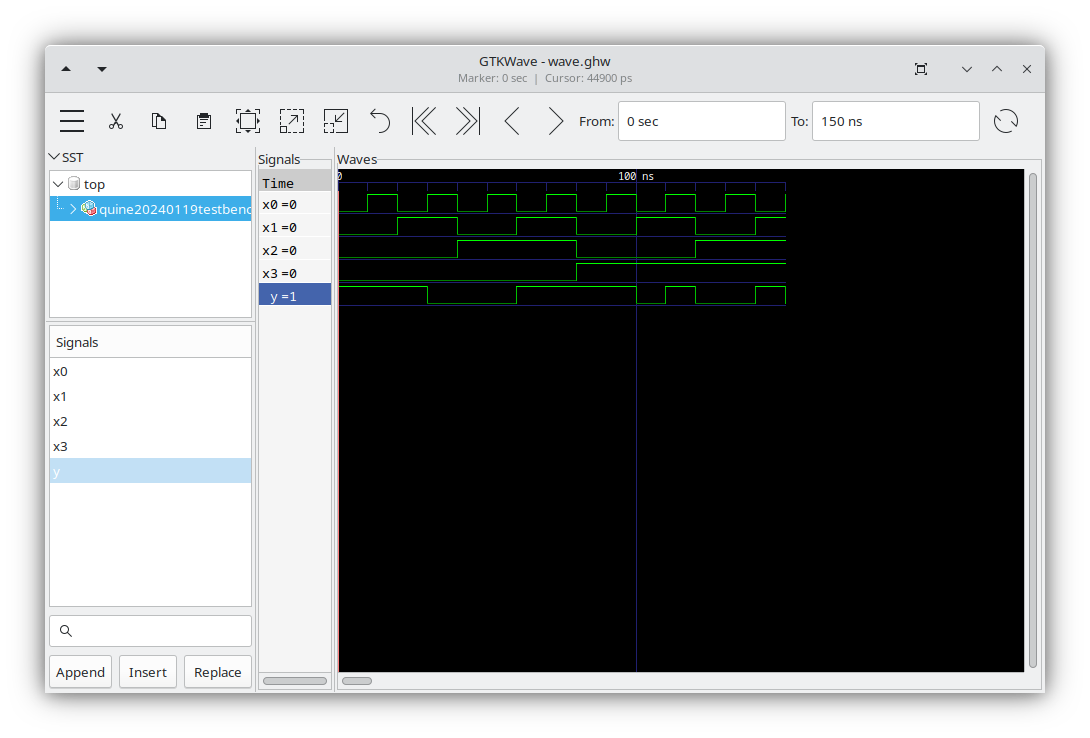

VHDL:

library ieee;

use ieee.std_logic_1164.all;

entity quine20240119 is

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture behaviourdisjunktivenormalform of quine20240119 is

begin

y <= (not x2 and not x1) or

(not x3 and x2 and x1) or

(x3 and not x2 and x0) or

(not x3 and x1 and not x0) or

(x2 and x1 and not x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity quine20240119testbench is

port (

y: out std_logic

);

end;

architecture behaviour of quine20240119testbench is

component quine20240119

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

sn: quine20240119 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity quine20240119 is

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture behaviourdisjunktivenormalform of quine20240119 is

begin

y <= (not x2 and not x1) or

(not x3 and x2 and x1) or

(x3 and not x2 and x0) or

(not x3 and x1 and not x0) or

(x2 and x1 and not x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity quine20240119testbench is

port (

y: out std_logic

);

end;

architecture behaviour of quine20240119testbench is

component quine20240119

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

sn: quine20240119 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;

// Nicht zu 100% der Testbench generator

#include <stdio.h>

int main (void) {

int i;

int j;

int k, l;

int v = 0;

char *a [] = {"x", "a", "b"};

for (k = 0, l = 1; k < 3; k++, l = l*2) {

printf ("%s <= ", a [k]);

for (j = 1, i = 0, v = 0; i < 80; i+=10, j++) {

printf ("'%i' after %i ns, ", v, i);

if ((j % l) == 0) {

v = (v + 1) % 2;

}

}

j = j%2;

printf ("'%i' after %i ns;nn", v, i);

}

return 0;

}

david@laptop-peaq:~\$ ./quine quine quine8 quine8.c quine.c david@laptop-peaq:~\$ ./quine quine quine8 quine8.c quine.c david@laptop-peaq:~\$ ./quine > quine20240119.txt david@laptop-peaq:~\$ cp quine quine quine20240119.txt quine8 quine8.c quine.c david@laptop-peaq:~\$ cp quine20240119.txt quine quine quine20240119.txt quine8 quine8.c quine.c david@laptop-peaq:~\$ cp quine20240119.txt quine20240119.txt.bak david@laptop-peaq:~\$ ./generatetestbench generatetestbench2 generatetestbench3 generatetestbench4 david@laptop-peaq:~\$ ./generatetestbench3 >> quine20240119.txt david@laptop-peaq:~\$ vhdl -a quine quine quine20240119.txt quine20240119.txt.bak quine20240119.vhdl quine8 quine8.c quine.c david@laptop-peaq:~\$ vhdl -a quine20240119.vhdl bash: vhdl: Kommando nicht gefunden. david@laptop-peaq:~\$ ghdl -a quine20240119.vhdl david@laptop-peaq:~\$ ghdl -r quine20240119testbench --wave=wave.ghw david@laptop-peaq:~\$ gtkwave wave.ghw GTKWave Analyzer v3.3.114 (w)1999-2023 BSI [0] start time. [150000000] end time. \^C david@laptop-peaq:~\$