Nächste Seite: Oszilloskop Test - Nummer Aufwärts: Übungen Vorherige Seite: 2024-12-13, VHDL/TTL - Quine

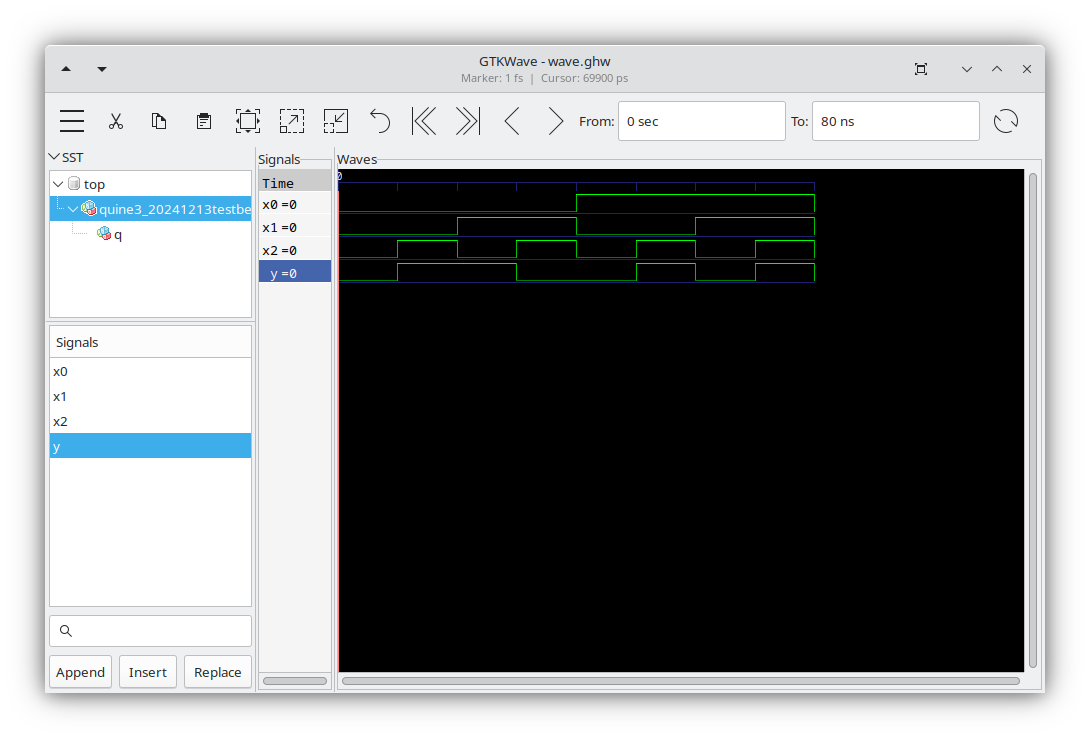

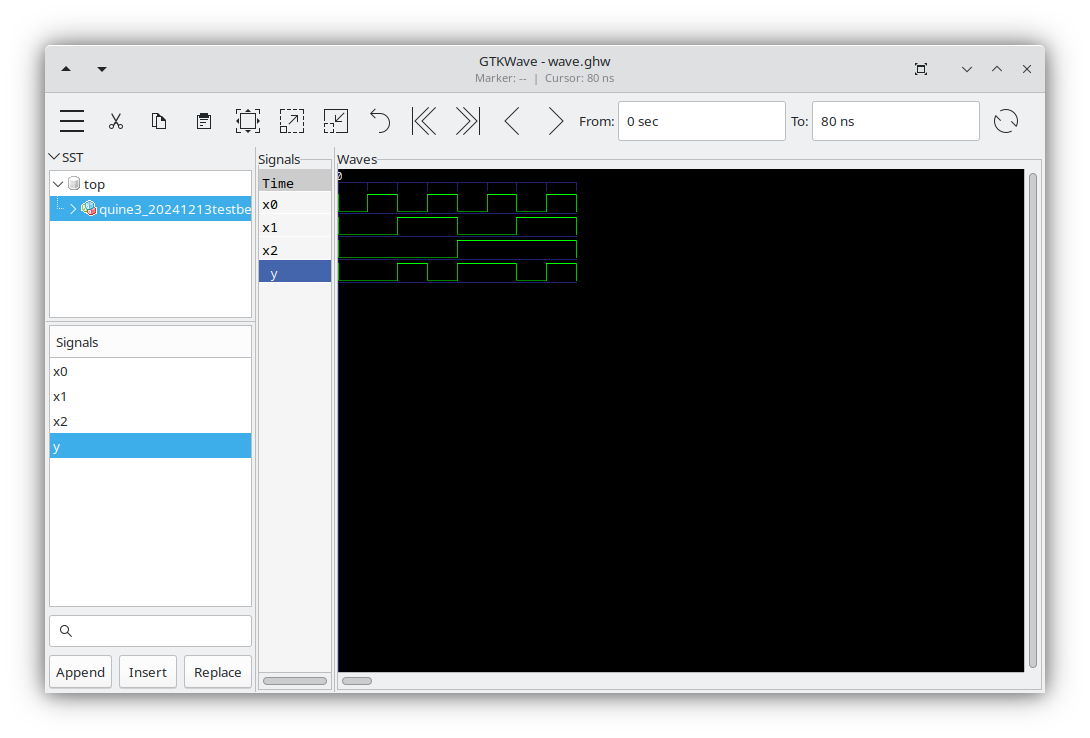

(C) David Vajda Fri Dec 13 12:44:46 2024 3 Network - TTL - Disjunktive Normalform x2 x1 x0 y 0 0 0 0 0 1 0 0 1 0 2 0 1 0 1 3 0 1 1 0 4 1 0 0 1 5 1 0 1 1 6 1 1 0 0 7 1 1 1 1 x2 x1 x0 y 2 0 1 0 1 4 1 0 0 1 5 1 0 1 1 7 1 1 1 1 x2 x1 x0 y Gruppe 1: 2 0 1 0 1 4 1 0 0 1 Gruppe 2: 5 1 0 1 1 Gruppe 3: 7 1 1 1 1 2 0 1 0 4:5 1 0 - 5:7 1 - 1 2 4 5 7 2 + 4:5 + + 5:7 + + 2 0 1 0 4:5 1 0 - 5:7 1 - 1 y <= (not x2 and x1 and not x0) or (x2 and not x1) or (x2 and x0); y <= not ( (x2 or not x1 or x0) and (not x2 or x1) and (not x2 or not x0) ); library ieee; use ieee.std_logic_1164.all; entity quine3_20241213 is port ( x2, x1, x0: in std_logic; y: out std_logic ); end; architecture behaviour of quine3_20241213 is begin y <= not ( (x2 or not x1 or x0) and (not x2 or x1) and (not x2 or not x0) ); end; library ieee; use ieee.std_logic_1164.all; entity quine3_20241213testbench is port ( y: out std_logic ); end; architecture behaviour of quine3_20241213testbench is component quine3_20241213 port ( x2, x1, x0: in std_logic; y: out std_logic ); end component; signal x2, x1, x0: std_logic; begin q: quine3_20241213 PORT MAP (x2=>x2, x1=>x1, x0=>x0, y=>y); |

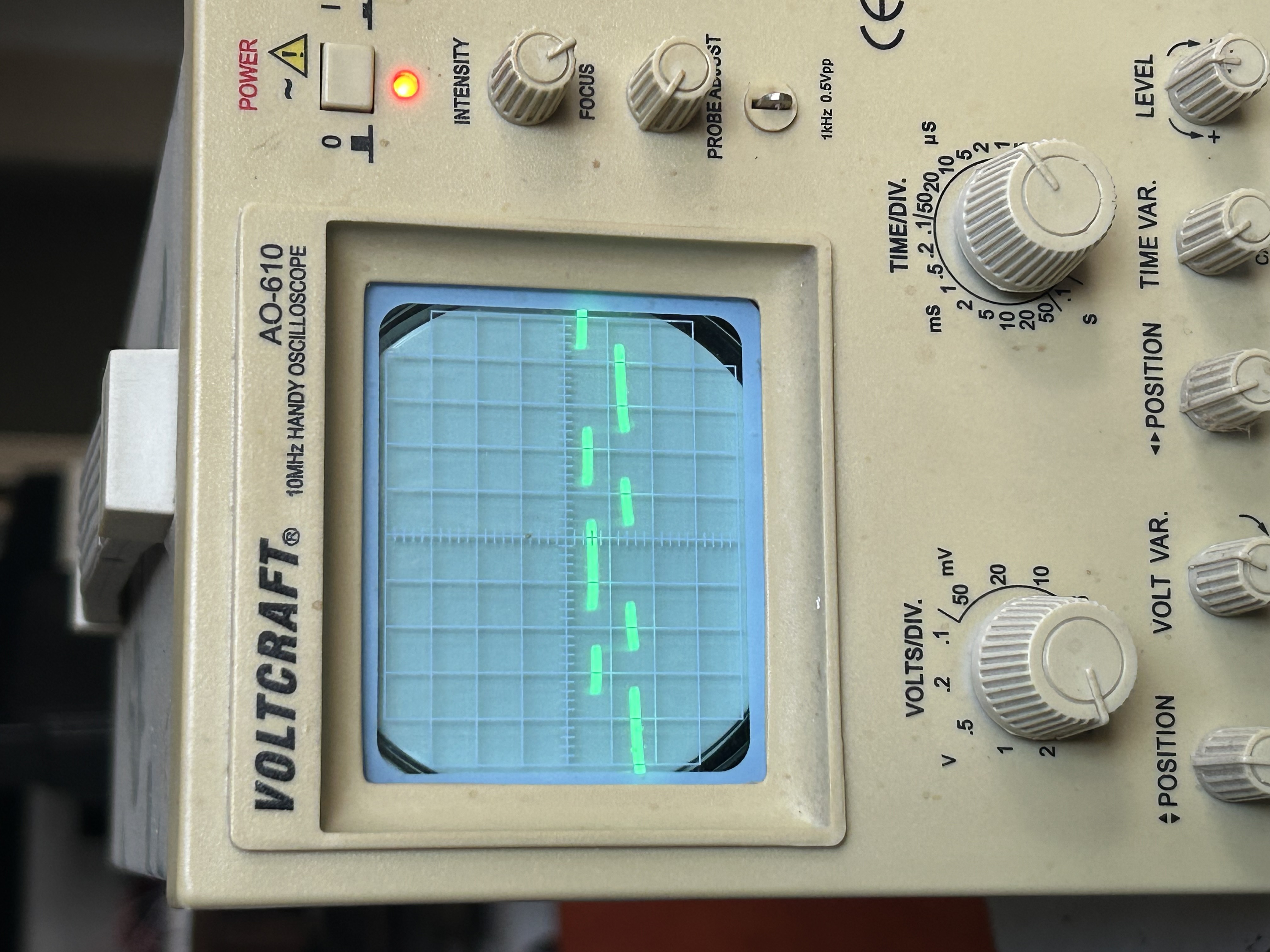

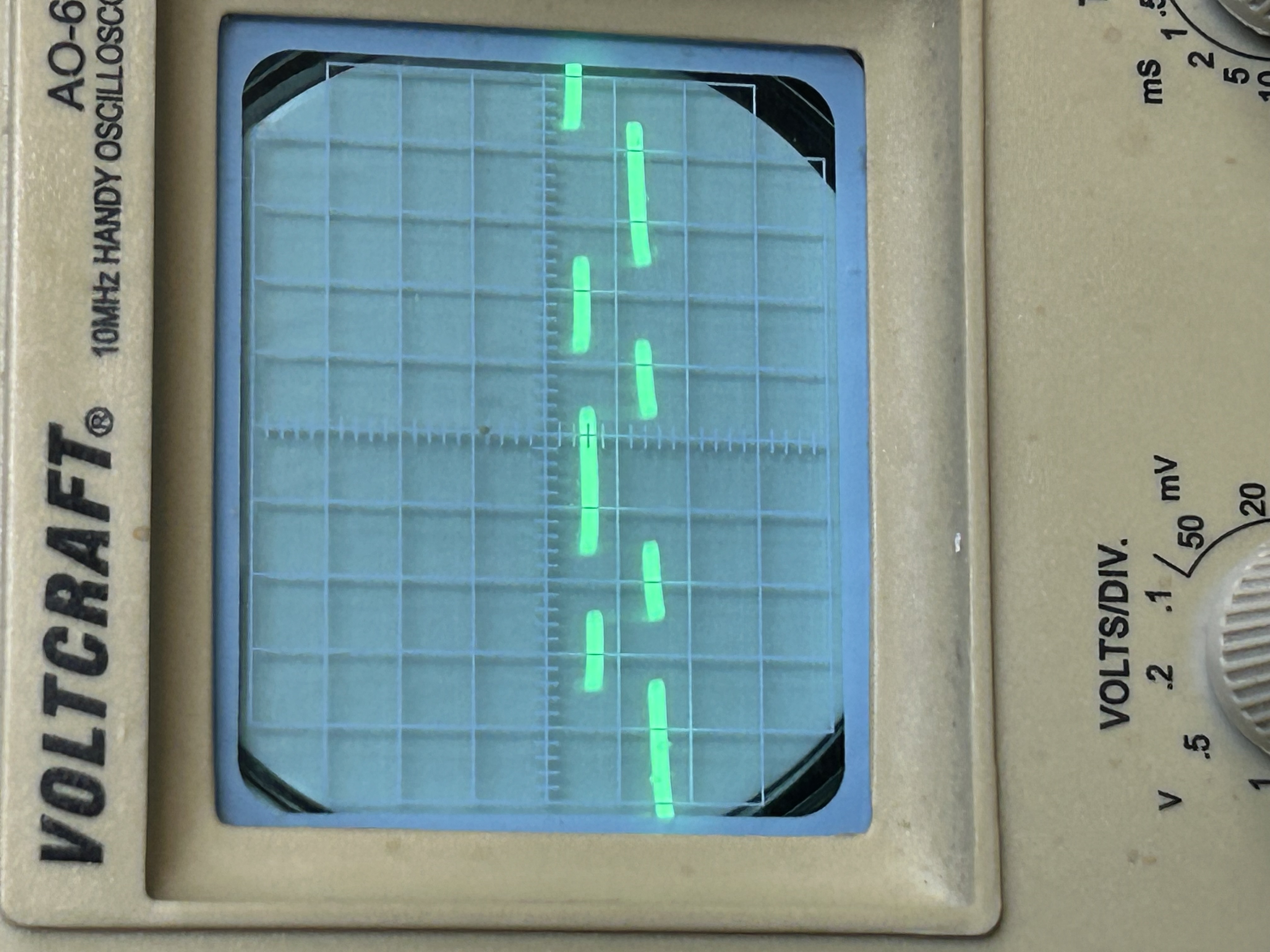

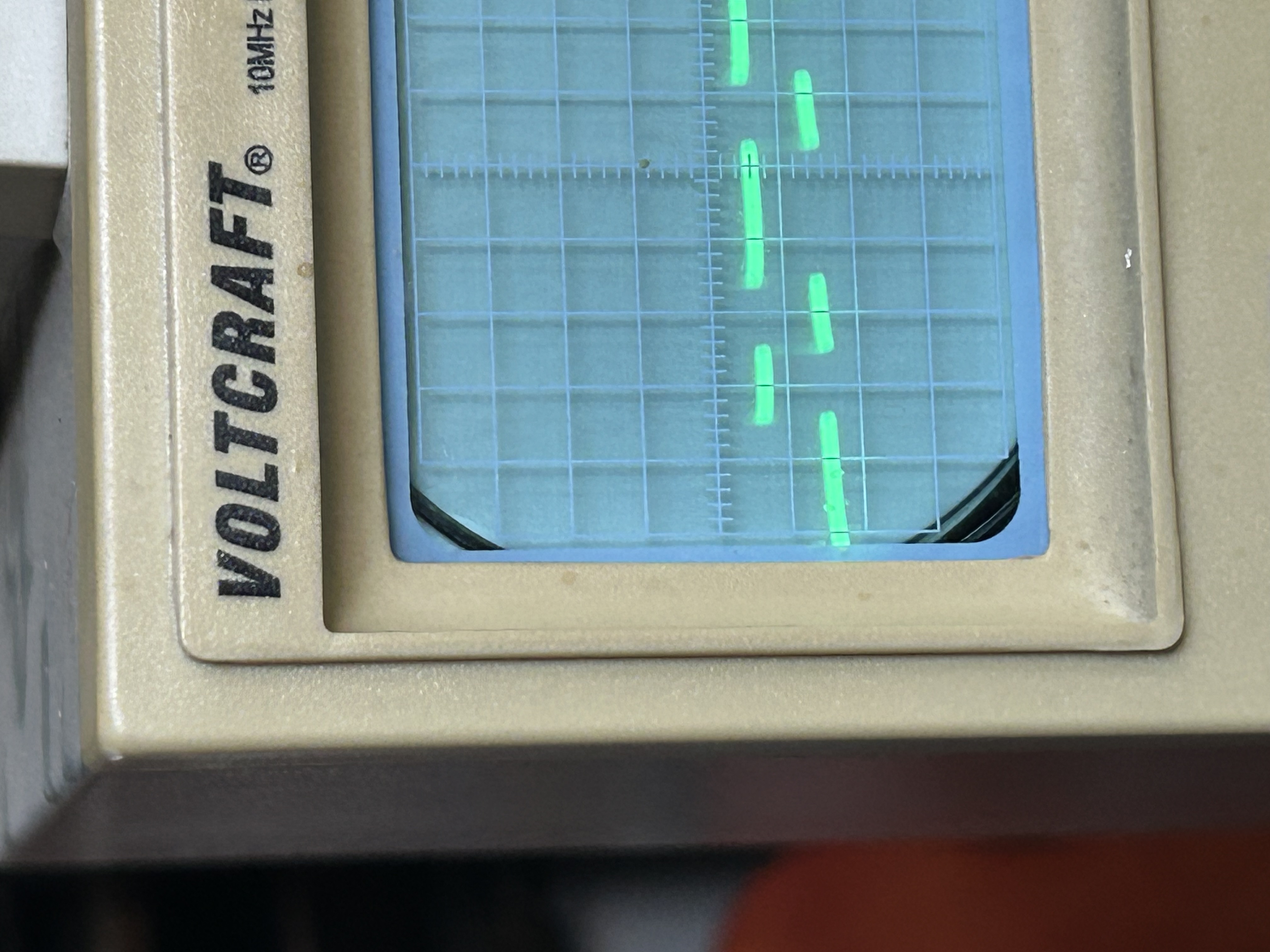

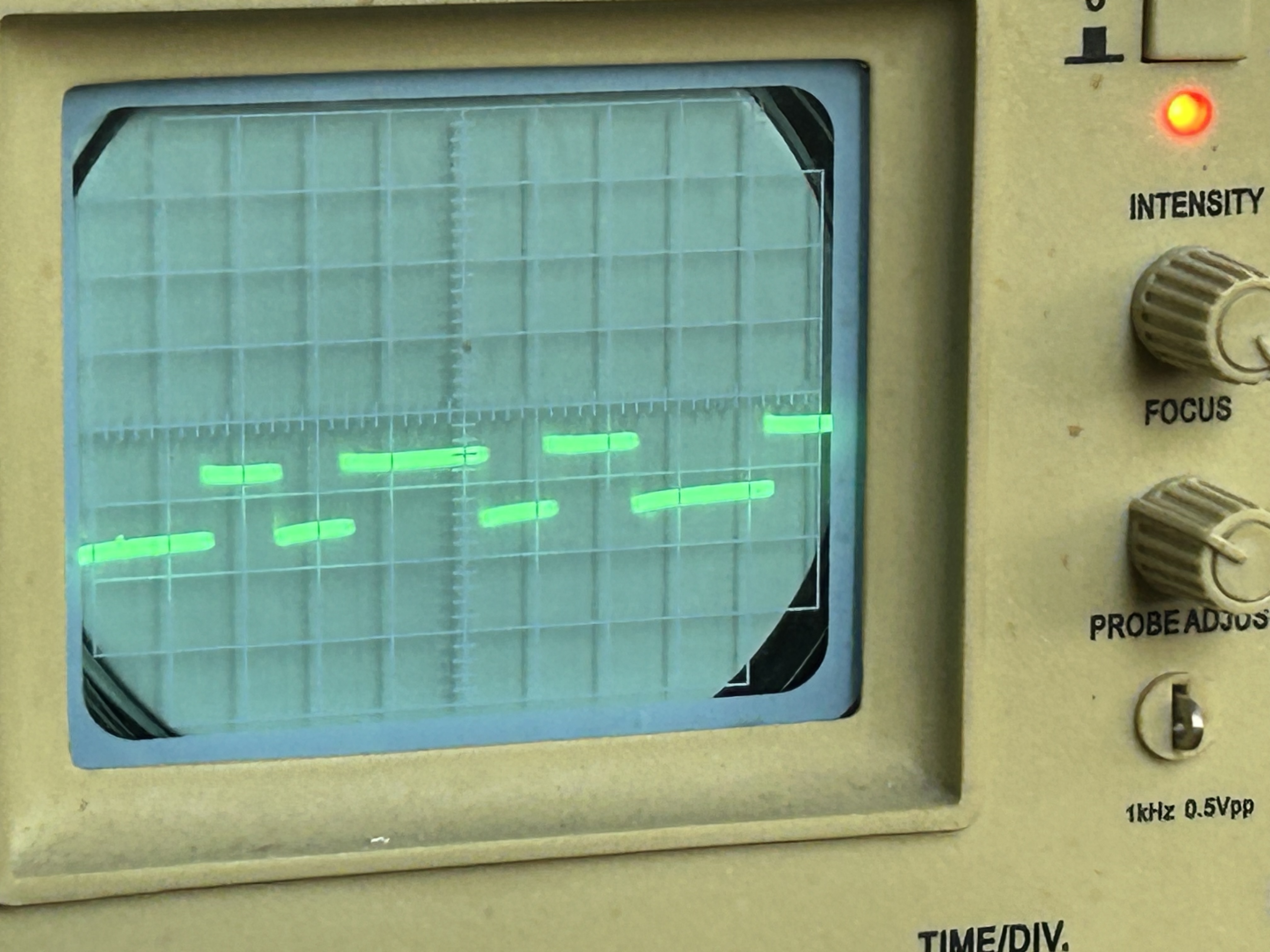

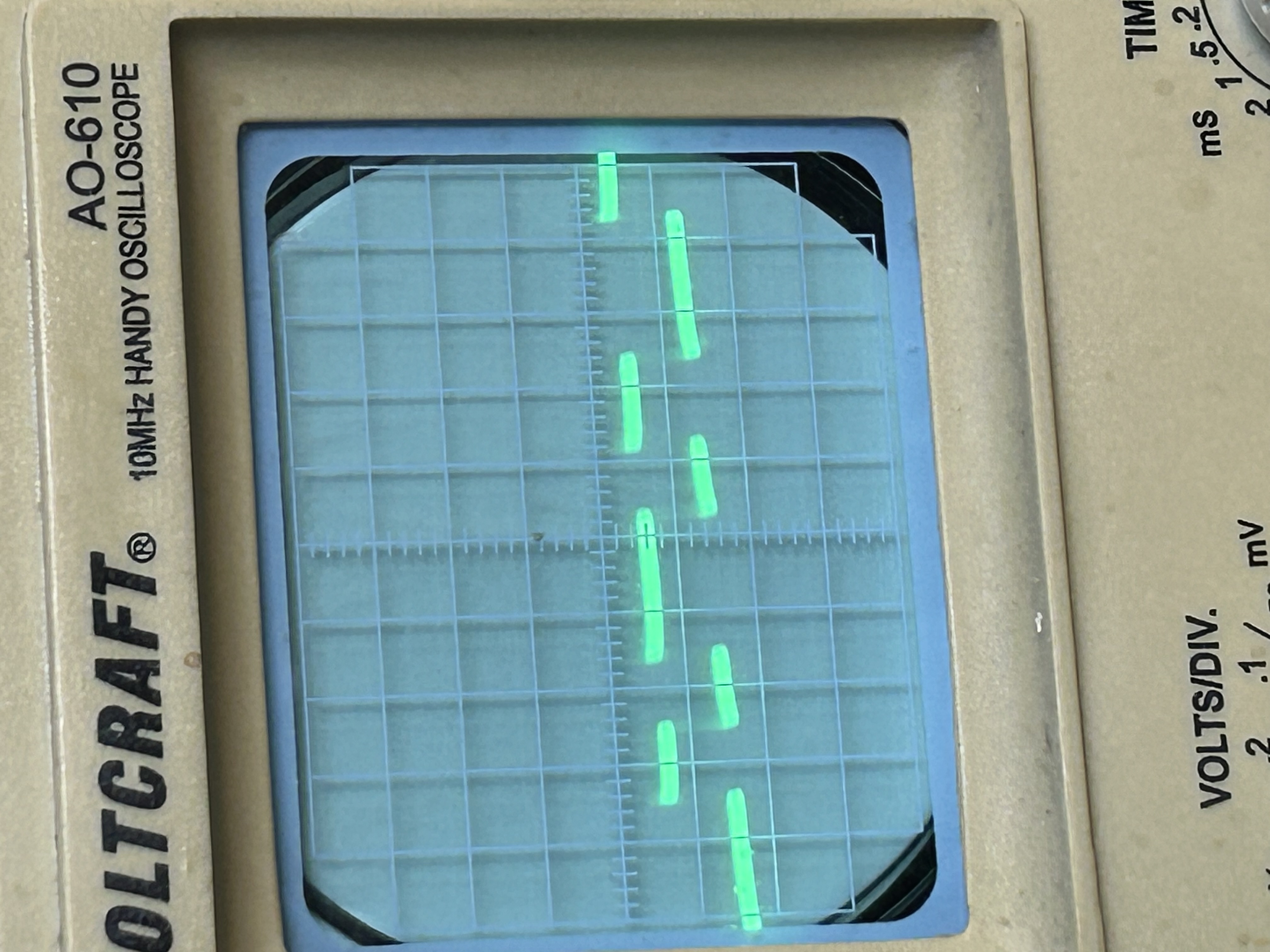

Es hat funktioniert! Natürlich musste die Frequenz nach oben gedreht werden.

.include "m8def.inc" ldi r16, HIGH (RAMEND) out SPH, r16 ldi r16, LOW (RAMEND) out SPL, r16 ldi r16, 0xff out DDRD, r16 out DDRB, r16 ldi r16, 0x01 loop1: mov r17, r16 com r17 out PORTB, r17 out PORTD, r16 ;rcall sleep inc r16 cpi r16, 0b00001000 brne loop1 ldi r16, 0x00 rjmp loop1 sleep: push r16 push r17 push r18 ldi r16, 0xff sleep_loop1: dec r16 ldi r17, 0xff sleep_loop2: dec r17 ldi r18, 0x08 sleep_loop3: dec r18 cpi r18, 0x01 brne sleep_loop3 cpi r17, 0x01 brne sleep_loop2 cpi r16, 0x01 brne sleep_loop1 pop r18 pop r17 pop r16 ret |