Nächste Seite: m820250116rs232transmit.asm Aufwärts: Übungen Vorherige Seite: m820250116ledblink.asm

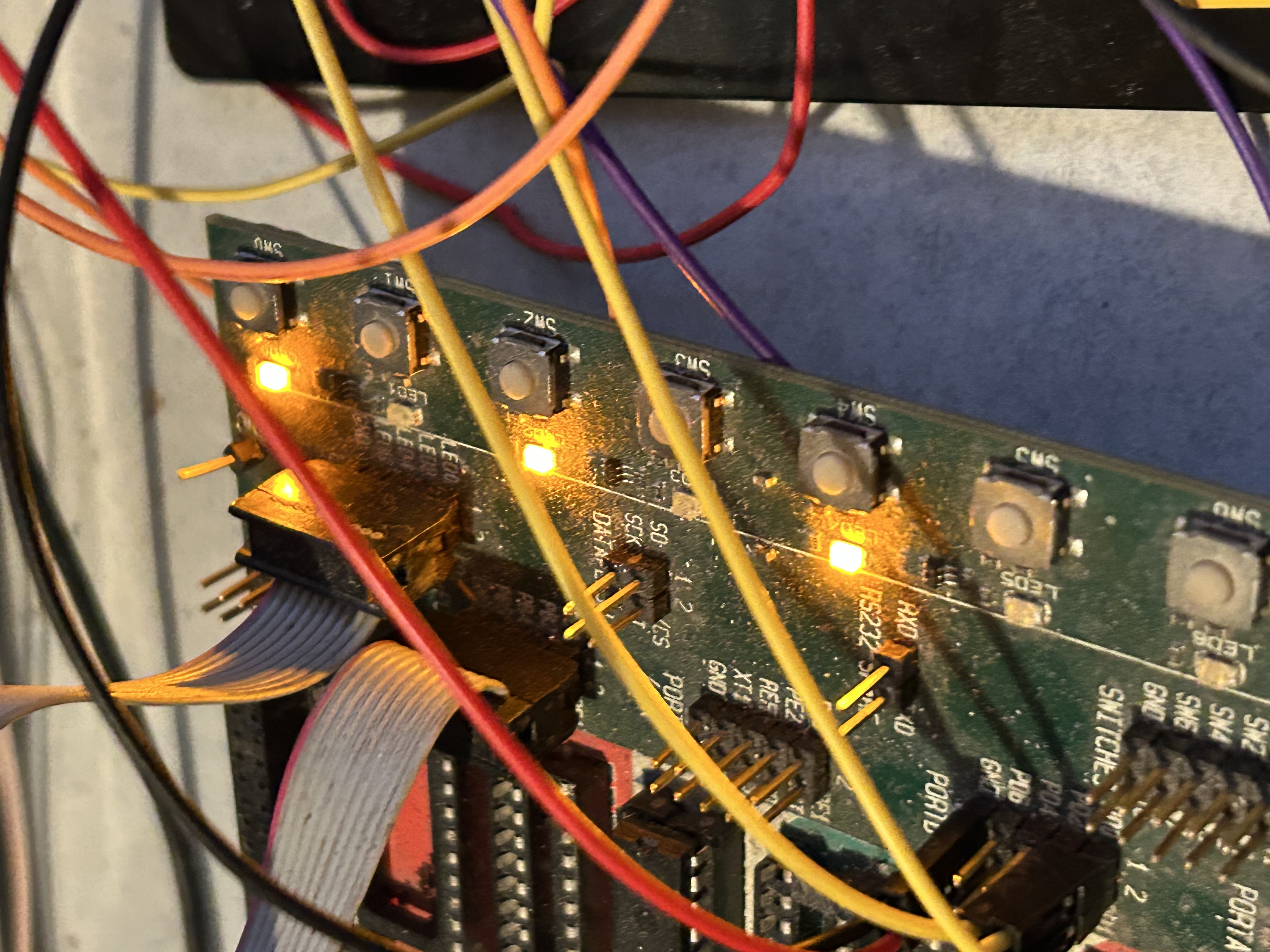

; (C) David Vajda ; 2025-01-16 ; AVR/Atmega8 LED, PORTB .include "m8def.inc" ldi r16, 0xff out DDRB, r16 ldi r16, 0b010101010 out PORTB, r16 end: rjmp end |