Nächste Seite: m820250116siebensegmentcount.asm Aufwärts: Übungen Vorherige Seite: m820250116portb.asm

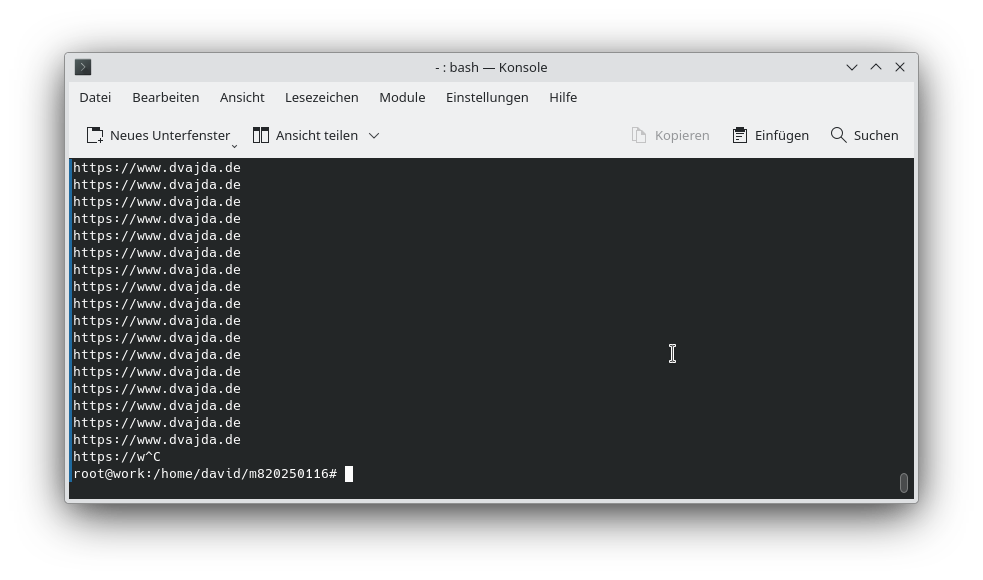

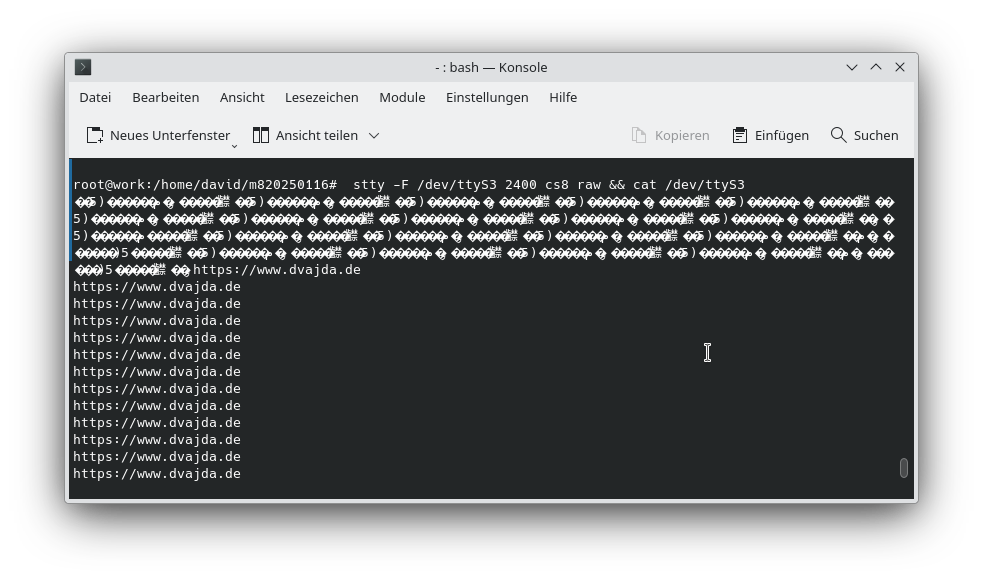

; (C) David Vajda ; 2025-01-16 ; AVR/Atmega8 LED, RS-232, Transmit .include "m8def.inc" ldi r16, HIGH (RAMEND) out SPH, r16 ldi r16, LOW (RAMEND) out SPL, r16 ldi r16, HIGH (25) out UBRRH, r16 ldi r16, LOW (25) out UBRRL, r16 ldi r16, (1 << URSEL) | (1 << UCSZ1) | (1 << UCSZ0) out UCSRC, r16 ldi r16, (1 << TXEN) out UCSRB, r16 loop1: ldi r16, 'h' rcall rs232transmit ldi r16, 't' rcall rs232transmit ldi r16, 't' rcall rs232transmit ldi r16, 'p' rcall rs232transmit ldi r16, 's' rcall rs232transmit ldi r16, ':' rcall rs232transmit ldi r16, '/' rcall rs232transmit ldi r16, '/' rcall rs232transmit ldi r16, 'w' rcall rs232transmit ldi r16, 'w' rcall rs232transmit ldi r16, 'w' rcall rs232transmit ldi r16, '.' rcall rs232transmit ldi r16, 'd' rcall rs232transmit ldi r16, 'v' rcall rs232transmit ldi r16, 'a' rcall rs232transmit ldi r16, 'j' rcall rs232transmit ldi r16, 'd' rcall rs232transmit ldi r16, 'a' rcall rs232transmit ldi r16, '.' rcall rs232transmit ldi r16, 'd' rcall rs232transmit ldi r16, 'e' rcall rs232transmit ldi r16, 10 rcall rs232transmit ldi r16, 13 rcall rs232transmit rjmp loop1 rs232transmit: sbis UCSRA, UDRE rjmp rs232transmit out UDR, r16 ret |